光电集成式半导体封装结构及其制备方法与流程

本发明属于半导体封装领域,涉及一种光电集成式半导体封装结构及其制备方法。

背景技术:

1、随着大数据、人工智能、远程医疗、物联网、电子商务、5g通信的不断发展,全球数据流量爆发式地增长,更低成本、更可靠、更快及更高密度的电路是集成电路封装追求的目标。

2、为了满足互联网流量的需求,数据中心节点带宽需要达到10tb/s,为了减缓数据中心能耗增长的趋势,必须想办法降低系统、器件的功耗。在超高数据容量的驱动下,传统的电芯片制程逐渐接近10nm尺寸,cmos工艺即将遇到物理极限,由于光具有信号衰减小、能耗低、高带宽以及与cmos兼容的性能,业界普遍认为硅光芯片有机结合了成熟微电子和光电子技术,既可减小芯片尺寸、降低成本与功耗,还可提高可靠性,有望成为“超越摩尔”的高速信息引擎。因此,引入硅光技术十分必要,由于硅光技术引入的目的是增加输入/输出(input/output,i/o)带宽并最大限度地降低能耗,光集成电路(pic)和电集成电路(eic)如何封装致关重要,这些因素将直接影响到i/o的带宽和能耗。

3、现有的光电集成式半导体封装结构大多直接将光集成芯片及电集成芯片键合于基板上,通过打线(wire-bonds)或倒置贴合(flip-chip)的方式与基板电连接。由于硅光工艺节点相对电芯片而言,比较落后,如目前单片集成开发的硅光工艺节点为45nm和32nm制程,这与电芯片10nm以下的工艺节点相比相差甚远,从而现有的光电集成式半导体封装结构难以满足高密度集成封装的需求。

4、因此,提供一种光电集成式半导体封装结构及其制备方法,实属必要。

技术实现思路

1、鉴于以上所述现有技术的缺点,本发明的目的在于提供一种光电集成式半导体封装结构及其制备方法,用于解决现有技术中难以将光芯片与电芯片进行高密度集成封装的问题。

2、为实现上述目的及其他相关目的,本发明提供一种光电集成式半导体封装结构的制备方法,包括以下步骤:

3、提供tsv基底,所述tsv基底的第一面显露tsv金属柱的第一端;

4、于所述tsv基底的第一面上形成第一重新布线层,且所述第一重新布线层与所述tsv金属柱的第一端电连接;

5、图形化所述第一重新布线层及所述tsv基底,形成贯穿所述第一重新布线层且位于所述tsv基底中的沟槽;

6、于所述第一重新布线层上形成图形化的光波导布线层、微反射镜及第二重新布线层,所述第二重新布线层与所述第一重新布线层电连接,所述光波导布线层填充所述沟槽并与所述微反射镜对应设置,且所述第二重新布线层覆盖所述光波导布线层显露所述微反射镜;

7、提供第一支撑衬底,将所述第二重新布线层与所述第一支撑衬底键合;

8、减薄所述tsv基底,显露所述tsv金属柱的第二端及所述光波导布线层;

9、于所述tsv基底的第二面上形成第三重新布线层及金属凸块,所述第三重新布线层与所述tsv金属柱的第二端电连接,所述金属凸块与所述第三重新布线层电连接,且所述第三重新布线层显露所述光波导布线层;

10、去除所述第一支撑衬底,提供第二支撑衬底,将所述金属凸块与所述第二支撑衬底键合;

11、于所述第二重新布线层上键合电芯片及第一光芯片,所述电芯片及所述第一光芯片均与所述第二重新布线层电连接,且所述第一光芯片的第一感光区与所述微反射镜对应设置;

12、去除所述第二支撑衬底,提供基板,所述基板中设置有第二光芯片;

13、于所述基板上形成第四重新布线层,所述第四重新布线层与所述基板电连接,且所述第四重新布线层显露所述第二光芯片的第二感光区;

14、将所述金属凸块与所述第四重新布线层键合,所述第四重新布线层与所述金属凸块电连接,且所述光波导布线层与所述第二感光区对应设置;

15、提供连接器,将所述连接器键合于所述基板上,且所述连接器与所述光波导布线层对应设置。

16、可选地,形成所述微反射镜的方法包括半导体曝光显影图案化法或键合法。

17、可选地,当采用半导体曝光显影图案化法制备所述微反射镜时,所述微反射镜与所述第二重新布线层同步形成。

18、可选地,形成所述光波导布线层的方法包括半导体曝光显影法,形成的所述光波导布线层包括有机聚合物光波导布线层、硅基光波导布线层、铌酸锂光波导布线层或硼酸锂光波导布线层。

19、可选地,还包括提供散热件并键合所述散热件的步骤,其中,键合后的所述散热件与所述电芯片和/或所述第一光芯片直接和/或间接接触。

20、可选地,在去除所述第二支撑衬底后还包括进行晶圆切割的步骤。

21、可选地,所述电芯片、所述第一光芯片及所述第二重新布线层之间形成有填充缝隙的第一底部填充层;所述第三重新布线层与所述第四重新布线层之间形成有填充缝隙的第二底部填充层。

22、可选地,形成的所述第一重新布线层包括大马士革重新布线层;形成的所述第二重新布线层包括有机重新布线层;形成的所述第三重新布线层包括有机重新布线层;形成的所述第四重新布线层包括有机重新布线层。

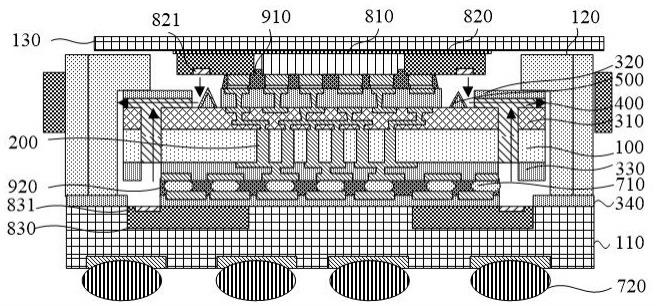

23、本发明还提供一种光电集成式半导体封装结构,所述光电集成式半导体封装结构包括:

24、tsv基底,所述tsv基底的第一面显露tsv金属柱的第一端;

25、第一重新布线层,所述第一重新布线层位于所述tsv基底的第一面上,且所述第一重新布线层与所述tsv金属柱的第一端电连接;

26、沟槽,所述沟槽贯穿所述第一重新布线层及所述tsv基底;

27、图形化的光波导布线层,所述光波导布线层位于所述第一重新布线层上且填充所述沟槽;

28、微反射镜,所述微反射镜位于所述第一重新布线层上,且所述光波导布线层与所述微反射镜对应设置;

29、第二重新布线层,所述第二重新布线层位于所述第一重新布线层上并与所述第一重新布线层电连接,且覆盖所述光波导布线层显露所述微反射镜;

30、第三重新布线层,所述第三重新布线层位于所述tsv基底的第二面上并与所述tsv金属柱的第二端电连接,且显露所述光波导布线层;

31、金属凸块,所述金属凸块位于所述第三重新布线层上,且与所述第三重新布线层电连接;

32、电芯片及第一光芯片,所述电芯片及所述第一光芯片均键合于所述第二重新布线层上,所述电芯片及所述第一光芯片均与所述第二重新布线层电连接,且所述第一光芯片的第一感光区与所述微反射镜对应设置;

33、基板,所述基板中设置有第二光芯片,且所述第二光芯片的第二感光区与所述光波导布线层对应设置;

34、第四重新布线层,所述第四重新布线层位于所述基板上,所述第四重新布线层与所述金属凸块键合并与所述金属凸块电连接,所述第四重新布线层显露所述第二感光区,且所述第二感光区与所述光波导布线层对应设置;

35、连接器,所述连接器键合于所述基板上,且所述连接器与所述光波导布线层对应设置。

36、可选地,还包括散热件,所述散热件与所述电芯片和/或所述第一光芯片直接和/或间接接触。

37、如上所述,本发明的光电集成式半导体封装结构及其制备方法,通过tsv基底、基板、重新布线层、光波导布线层及微反射镜,将光芯片及电芯片进行合封,可实现电信号布线与光信号布线的堆叠互连及交错走线,以缩小封装面积、增加布线密度、有效缩短光信号、电信号的传输路径,减少信号衰减,提高集成运算能力,满足高密度集成封装的需求。

- 还没有人留言评论。精彩留言会获得点赞!