沟槽栅IGBT器件、制作方法及仿真方法与流程

本发明涉及功率半导体,尤其涉及沟槽栅igbt器件、制作方法及仿真方法。

背景技术:

1、igbt(insulated gate bipolar transistor,绝缘栅双极型晶体管)是由bjt(双极结型三极管,bipolar junction transistor)和mosfet(金属氧化物半导体场效应晶体管,metal oxide semiconductor field effect transistor)组成的复合驱动式功率半导体器件,具备mosfet与双极结型三极管的特点,具有良好的通态电流和开关损耗之间的折中关系。igbt具有高正向导通电流密度和低导通压降、驱动电路简单、可控性好、安全工作区大等优点。igbt正向导通时,集电极会注入大量非平衡载流子来形成电导调制效应,大大降低导通压降,这也导致器件关断时,耐压区过剩的少数载流子需要一段时间才能抽取消失, 从而使得igbt关断速度较慢,关断损耗较高。为进一步改善igbt正向导通压降和关断损耗的折中性能,可采用发射极载流子增强技术,传统载流子增强技术所采用的结构为csl(带载流子存储层,carrier stored layer)的igbt器件。也有一种方式是把n型外延层上部分建立空穴屏障同沟槽栅极结构结合,提出在沟槽栅igbt的p型体区与n型外延层之间引入n型掺杂的载流子存储层这一结构,其中载流子存储层掺杂浓度要高于外延层掺杂浓度,并将这种结构命名为cstbt(载流子存储层沟槽型双极晶体管,carrier stored trench gatebipolar transistor),这是igbt中应用载流子增强技术的一种常用结构,器件正向导通时,外延层与载流子存储层之间的n n+结会建立起扩散电势阻碍空穴的流出,因此载流子存储层下方存在空穴的堆积。当空穴数量大于电子的数量时,该区域的n型外延层将不能维持电荷平衡条件,为了维持电荷平衡,发射极会注入更多的电子流过p型体区内的反型层沟道,提高了发射极的载流子注入率,这相当于使外延层中靠近发射极一侧的载流子浓度局部增加,降低了器件的导通压降。采用载流子存储层结构的igbt器件提高了发射极的注入效率,等同于可以降低集电极的注入效率来获得相同的导通压降,这样在igbt在关断时,由于集电极注入的载流子效率变低,关断时间就可以被大大降低,关断损耗也降低。

2、cstbt的导通压降随着cs层掺杂浓度的增加而降低,现有工艺中的cs层通常是在做完厚氧的刻蚀步骤之后不带光罩进行注入,因此无法有效地利用厚氧步骤的高温长时间热制程,使得cs层的推进深度往往受到限制,导致器件的导通损耗和安全工作区等性能大幅度降低。

3、因此,有必要设计一种新的方法,实现提高了cs层的注入效率,达到降低cstbt导通压降和饱和电流的目的,优化导通压降和关断损耗的折衷关系。

技术实现思路

1、本发明要解决的技术问题是提供沟槽栅igbt器件、制作方法及仿真方法。

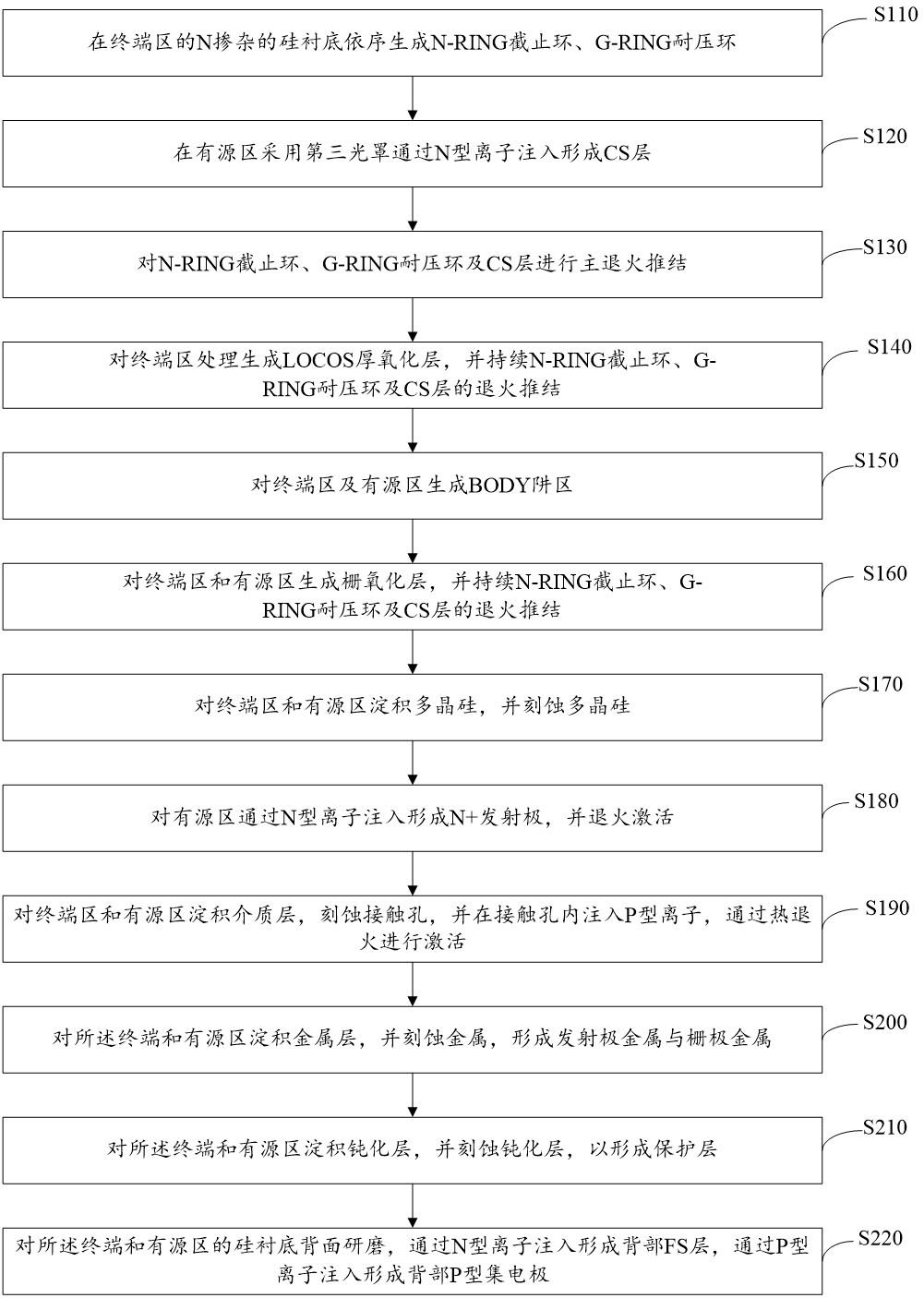

2、为解决上述技术问题,本发明的目的是通过以下技术方案实现的:提供沟槽栅igbt器件制作方法,包括:

3、在终端区的n掺杂的硅衬底依序生成n-ring截止环、g-ring耐压环;

4、在有源区采用第三光罩通过n型离子注入形成cs层;

5、对n-ring截止环、g-ring耐压环及cs层进行主退火推结;

6、对终端区处理生成locos厚氧化层,并持续n-ring截止环、g-ring耐压环及cs层的退火推结;

7、对终端区及有源区生成body阱区;

8、对终端区和有源区生成栅氧化层,并持续n-ring截止环、g-ring耐压环及cs层的退火推结;

9、对终端区和有源区淀积多晶硅,并刻蚀多晶硅;

10、对有源区通过n型离子注入形成n+发射极,并退火激活;

11、对终端区和有源区淀积介质层,刻蚀接触孔,并在接触孔内注入p型离子,通过热退火进行激活;

12、对所述终端和有源区淀积金属层,并刻蚀金属,形成发射极金属与栅极金属;

13、对所述终端和有源区淀积钝化层,并刻蚀钝化层,以形成保护层;

14、对所述终端和有源区的硅衬底背面研磨,通过n型离子注入形成背部fs层,通过p型离子注入形成背部p型集电极。

15、其进一步技术方案为:所述在终端区的n掺杂的硅衬底依序生成n-ring截止环、g-ring耐压环,包括:

16、采用第一光罩在终端区的n-掺杂的硅衬底上通过n型离子注入形成n-ring截止环;

17、采用第二光罩在终端区通过p型离子注入形成g-ring耐压环。

18、其进一步技术方案为:所述对n-ring截止环、g-ring耐压环及cs层进行主退火推结,包括:

19、对n-ring截止环、g-ring耐压环及cs层采用1150℃至1200c℃的退火推结,推结时间为180 min至400min。

20、其进一步技术方案为:所述对终端区生成body阱区,包括:

21、对所述终端区去除氮化硅,通过p型离子注入形成body阱区。

22、其进一步技术方案为:所述对终端区和有源区生成栅氧化层,并持续n-ring截止环、g-ring耐压环及cs层的退火推结,包括:

23、采用第五光罩对终端区和有源区通过在硅衬底表面刻蚀形成沟槽,并通过热氧化先后形成牺牲氧化层和栅氧化层,持续n-ring截止环、g-ring耐压环及cs层的退火推结。

24、其进一步技术方案为:所述对有源区通过n型离子注入形成n+发射极,并退火激活,包括:

25、对有源区采用第三光罩通过n型离子注入形成n+发射极,并退火激活。

26、另外,本发明要解决的技术问题是还在于提供沟槽栅igbt器件,其特征在于,所述沟槽栅igbt器件采用上述的沟槽栅igbt器件制作方法制作而得,其中,所述沟槽栅igbt器件包括有源区以及终端区,所述终端区环绕在所述有源区的周围,所述终端区设有终端结构,所述终端结构包括终端正面结构,所述终端正面结构包括硅衬底、n-ring截止环、g-ring耐压环、locos厚氧化层、body阱区、栅氧化层、介质层、金属层以及保护层;其中,所述n-ring截止环、g-ring耐压环位于同一层,所述硅衬底位于所述n-ring截止环、g-ring耐压环的下层;相邻两个所述locos厚氧化层之间连接有body阱区;所述栅氧化层、介质层、金属层以及保护层自下而上设置在所述locos厚氧化层的上方;所述终端正面结构的介质层上设有接触孔,且所述接触孔内填充有p型杂质;所述有源区设有有源结构,所述有源结构包括有源正面结构;所述有源正面结构包括自下而上依序设置的硅衬底、cs层、body阱区、栅氧化层、n+发射极、介质层、金属层以及保护层;所述cs层上设有若干个沟槽,且所述沟槽贯穿所述cs层,所述body阱区所述栅氧化层设置在沟槽内壁以及所述body阱区的上方;所述body阱区设置在所述cs层上;所述沟槽内填充有多晶硅;所述body阱区上设有n+发射极;所述有源正面结构的介质层设有接触孔,且所述接触孔内填充有p型杂质。

27、其进一步技术方案为:所述终端结构还包括终端背面结构,所述终端背面结构包括背部fs层以及背部p型集电极,所述有源结构包括有源背面结构;所述有源背面结构包括背部fs层以及背部p型集电极。

28、另外,本发明要解决的技术问题是还在于提供沟槽栅igbt器件的仿真方法,其特征在于,包括:

29、获取上述的沟槽栅igbt器件的终端结构以及上述的沟槽栅igbt器件制作方法;

30、根据预置的分割规则对所述终端正面结构进行分割,得到多个分割区域;

31、确定沟槽栅igbt器件制作方法所对应的仿真代码,并利用仿真代码以及各所述分割区域的区域参数对各所述分割区域进行结构仿真,以生成对应的仿真模块;

32、根据各所述分割区域的区域位置对与各所述分割区域对应的仿真模块进行组合,得到初步组合结构;

33、根据所述终端背面结构进行平面结构仿真,得到背面仿真模块;

34、将所述初步组合结构与所述背面仿真模块进行整合,得到整合仿真终端结构;

35、采用历史经验法对所述整合仿真终端结构中各仿真模块的虚拟网格密度进行优化调整,得到调整后的整合仿真终端结构;

36、根据预置的运行规则对调整后的所述整合仿真终端结构进行仿真运行,以得到所述整合仿真终端结构的仿真电学性能参数。

37、其进一步技术方案为:所述采用历史经验法对所述整合仿真终端结构中各仿真模块的虚拟网格密度进行优化调整,得到调整后的整合仿真终端结构,包括:

38、根据已存的历史数据查找出与各仿真模块的结构最接近一致的历史虚拟网格密度,并按所述历史虚拟网格密度对所述整合仿真终端结构中各仿真模块的虚拟网格密度进行优化调整,得到调整后的整合仿真终端结构。

39、本发明与现有技术相比的有益效果是:本发明通过在厚氧生长之前增加一次np光刻,预先定义cs层的注入,将整个流程中的高温热制程高效地利用起来,综合对cs层进行推进,从而获得一个比较理想的深度与浓度分布,显著提高了cs层的注入效率,达到降低cstbt导通压降和饱和电流的目的,优化导通压降和关断损耗的折衷关系;选择性注入cs层,不会对p型的耐压环掺入n型杂质,更有利于稳定击穿电压;并没有增加光罩层数,最大限度地降低生产成本。

40、下面结合附图和具体实施例对本发明作进一步描述。

- 还没有人留言评论。精彩留言会获得点赞!