半导体器件结构及其制备方法与流程

本技术涉及半导体,具体涉及一种半导体器件结构及其制备方法。

背景技术:

1、碳化硅(silicon carbide, sic)因其优异的物理特性和电子特性而备受关注,其中包括高电子迁移率、高击穿电场强度、高热导率等优异的特性,这使得碳化硅成为满足高性能、高功率和高温应用需求的材料之一。然而,碳化硅也因其特殊的材料特性面临着许多挑战,例如:传统硅基mosfet(metal-oxide-semiconductor field-effect transistor)的栅极设计不一定适用于碳化硅,因此需要针对碳化硅的特点进行栅极优化。为了提高栅极的控制效果和性能,引入了高-k材料和金属栅极等新型材料和工艺,这些材料和工艺的创新使得栅极设计更加灵活,更加有助于优化电子的控制效果。

2、然而,现有的平面型碳化硅mosfet栅极技术仍然存在着许多问题,例如:材料兼容性差、界面特性有待优化、电子迁移率有待提高、制造工艺复杂、热管理差、可靠性差以及工艺一致性差等。

技术实现思路

1、本技术的目的是提供一种半导体器件结构及其制备方法,具有利于改善半导体器件结构的性能和可靠性,以及提高对电子的控制效果的优点。

2、为实现本技术的目的,本技术提供了如下的技术方案:

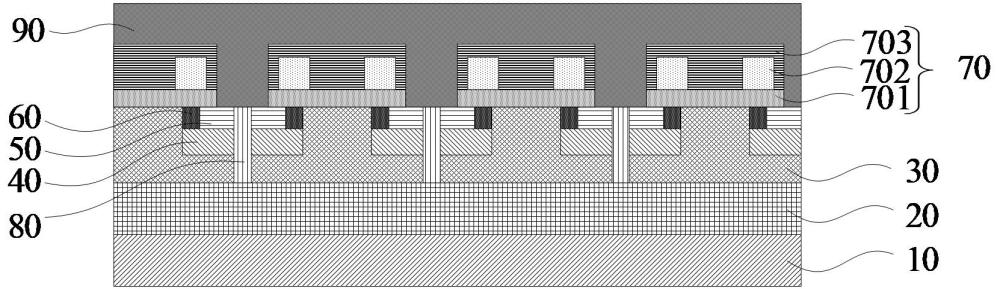

3、第一方面,本技术提供了一种半导体器件结构,包括:

4、第一导电类型的衬底;

5、第一导电类型的漂移区,位于所述衬底的表面;

6、jfet区,位于所述漂移区远离所述衬底的表面;

7、多个第二导电类型的阱区,位于所述jfet区内,且于所述jfet区内间隔排布;所述第二导电类型与所述第一导电类型不同;

8、多个第一导电类型的源区,位于所述阱区内;

9、多个沟道区,位于所述阱区内,且位于所述源区的外侧;

10、栅极结构,包括:栅介质层及多个栅极;所述栅介质层位于所述jfet区远离所述漂移区的表面,所述栅介质层于所述jfet区远离所述漂移区的表面的正投影覆盖所述沟道区、部分所述源区及位于相邻所述阱区之间的jfet区;多个所述栅极均位于所述栅介质层远离所述jfet区的表面,且位于所述沟道区的正上方,与所述沟道区一一对应设置。

11、本技术的半导体器件结构中,通过将栅极与沟道区上下对应设置,利用栅极在沟道区内产生的电场对称耦合,以此实现了均匀的电场分布,提高了电子的迁移率;减小了热点效应,避免了半导体器件结构中的局部热量积累和损坏器件;有助于更均匀地控制沟道中的电子或空穴,从而提高了电流的传输效率;减小了漏电流,提高了半导体器件结构的静态功耗特性;提高了电流传输效率,从而提高了半导体器件结构的开关速度;减小了失效风险,提高了可靠性、延长了器件的寿命以及提高了器件的一致性。解决了材料兼容性差、界面特性有待优化、电子迁移率有待提高、制造工艺复杂、热管理差、可靠性差以及工艺一致性差等技术方面的问题。

12、在其中一个实施例中,所述栅极结构还包括覆盖介质层,所述覆盖介质层位于所述栅介质层远离所述jfet区的表面,且覆盖所述栅极。

13、在其中一个实施例中,所述栅极结构的数量为多个,多个所述栅极结构间隔排布;

14、所述半导体器件结构还包括隔离结构,所述隔离结构位于相邻所述栅极结构之间,自所述阱区远离所述漂移区的表面贯穿所述源区、所述阱区及所述jfet区;所述隔离结构包括第二导电类型的掺杂区。

15、在其中一个实施例中,所述半导体器件结构还包括;源极电极,所述源极电极覆盖所述栅极结构,且与所述源区电连接。

16、在其中一个实施例中,所述半导体器件结构还包括:

17、欧姆接触层,位于所述源区与所述源极电极之间,与所述源区及所述源极电极均相接触;

18、钝化保护层,位于所述jfet区远离所述漂移区的表面,且覆盖所述源极电极。

19、第二方面,本技术还提供一种半导体器件结构的制备方法,包括:

20、提供第一导电类型的衬底;

21、于所述衬底的表面形成第一导电类型的漂移区;

22、于所述漂移区远离所述衬底的表面形成jfet区,所述jfet区位于保留的所述漂移区远离所述衬底的表面;

23、于所述jfet区内形成多个第二导电类型的阱区;多个所述阱区与所述jfet区内间隔排布;所述第二导电类型与所述第一导电类型不同;

24、于多个所述阱区内形成多个第一导电类型的源区;

25、于所述jfet区内形成沟道区,所述沟道区位于所述源区的外侧;

26、形成栅极结构,所述栅极结构包括:栅介质层及多个栅极;所述栅介质层位于所述jfet区远离所述漂移区的表面,所述栅介质层于所述jfet区远离所述漂移区的表面的正投影覆盖所述沟道区、部分所述源区及位于相邻所述阱区之间的jfet区;多个所述栅极均位于所述栅介质层远离所述jfet区的表面,且位于所述沟道区的正上方,与所述沟道区一一对应设置。

27、本技术的半导体器件结构的制备方法中,通过将栅极与沟道区尺寸上下对应设置,利用栅极在沟道区内产生的电场对称耦合,以此实现了均匀的电场分布,提高了电子的迁移率;减小了热点效应,避免了半导体器件结构中局部热量积累和损坏器件;有助于更均匀地控制沟道中的电子或空穴,从而提高了电流的传输效率;减小了漏电流,提高了半导体器件结构的静态功耗特性;提高了电流传输效率,从而提高了半导体器件结构的开关速度;减小了失效风险,提高了可靠性、延长了器件的寿命以及提高了器件的一致性。解决了材料兼容性差、界面特性有待优化、电子迁移率有待提高、制造工艺复杂、热管理差、可靠性差以及工艺一致性差等技术方面的问题。

28、在其中一个实施例中,所述栅极结构的数量为多个,多个所述栅极结构间隔排布;所述于所述jfet区内形成沟道区之后,形成栅极结构之前,还包括:形成隔离结构;所述隔离结构位于相邻所述栅极结构之间,自所述阱区远离所述漂移区的表面贯穿所述源区、所述阱区及所述jfet区;所述隔离结构包括第二导电类型的掺杂区。

29、在其中一个实施例中,所述形成隔离结构之后,还包括:将所得结构进行第一退火处理;所述栅极结构还包括覆盖介质层,所述覆盖介质层位于所述栅介质层远离所述jfet区的表面,且覆盖所述栅极;形成栅极结构包括:

30、于所述jfet区远离所述漂移区的表面形成栅介质材料层;

31、对所述栅介质材料层进行第二退火处理;

32、于所述栅介质材料层远离所述jfet区的表面形成栅极材料层;

33、刻蚀所述栅极材料层以得到所述栅极;

34、于所述栅介质材料层远离所述jfet区的表面形成覆盖介质材料层;

35、刻蚀所述覆盖介质材料层及所述栅介质材料层,以得到所述覆盖介质层及所述栅介质层。

36、在其中一个实施例中,所述形成栅极结构之后,还包括:形成源极电极,所述源极电极覆盖所述栅极结构,且与所述源区电连接。

37、在其中一个实施例中,所述形成源极电极之前,还包括:于所述源区远离所述阱区的表面形成欧姆接触层;所述源极电极与所述欧姆接触层相接触;

38、所述形成源极电极之后,还包括:形成钝化保护层,所述钝化保护层覆盖所述源极电极。

- 还没有人留言评论。精彩留言会获得点赞!