半导体器件及其制造方法与流程

本发明涉及半导体集成电路制造领域,特别涉及一种半导体器件及其制造方法。

背景技术:

1、随着半导体器件特征尺寸的不断缩小,芯片的性能日益受到金属互连结构带来的电阻-电容延迟(rc delay)的制约。为了改善rc delay,在现有工艺中,一方面引入低电阻率的铜替代传统铝进行布线,一方面采用低介电常数的材料作为层间介质层,而介电常数最低的绝缘介质-空气成为目前集成电路制造中的层间介质层的最理想选择。其中,气隙作为金属互连结构中的绝缘介质层不仅能显著减少寄生电容,而且能够改善金属互连结构的漏电流和与时间相关电介质击穿(tddb)特性。

2、参阅图1a~图1b,形成具有气隙的半导体器件的步骤可以包括:首先,如图1a所示,提供一衬底11,衬底11上形成有第一绝缘介质层12和第二绝缘介质层13,第一绝缘介质层12中形成有导电插塞14,第二绝缘介质层13中形成有金属互连线15,导电插塞14的一端与源极区或漏极区电连接,导电插塞14的另一端与金属互连线15电连接;然后,形成硬掩膜层16于第二绝缘介质层13和金属互连线15上,并通过光刻和干法刻蚀工艺形成开口于相邻两条金属互连线15之间的第二绝缘介质层13上方的硬掩膜层16中;然后,采用干法刻蚀工艺,刻蚀开口暴露出的第二绝缘介质层13和第一绝缘介质层12,以形成气隙17于栅极结构上方;然后,如图1b所示,形成第三绝缘介质层18将气隙17封口。

3、其中,在通过光刻和干法刻蚀工艺形成开口于相邻两条金属互连线15之间的第二绝缘介质层13上方的硬掩膜层16中时,由于受到光刻时的对准精度的影响,形成的开口的位置会向一侧的金属互连线15偏移,而若开口的宽度过大,会导致偏移后的开口暴露出一侧的金属互连线15,进而导致在后续执行刻蚀工艺时对暴露出的金属互连线15产生刻蚀而影响器件性能,因此,开口的宽度不能过大。但是,开口的宽度设计的很小会导致形成的气隙17的宽度也很小,即相邻两个导电插塞14之间剩余的第一绝缘介质层12的宽度以及相邻两条金属互连线15之间剩余的第二绝缘介质层13的宽度仍然很大,另一方面,在形成第三绝缘介质层18时,第三绝缘介质层18会进入气隙17内,并形成在气隙17内壁,气隙17的尺寸进一步缩小,难以实现理想状态下的空气介质层,从而导致对寄生电容的降低程度有限。

4、因此,如何改善气隙的形成工艺,以使得寄生电容得到明显降低是亟需解决的问题。

技术实现思路

1、本发明的目的在于提供一种半导体器件及其制造方法,使得半导体器件的寄生电容得到降低。

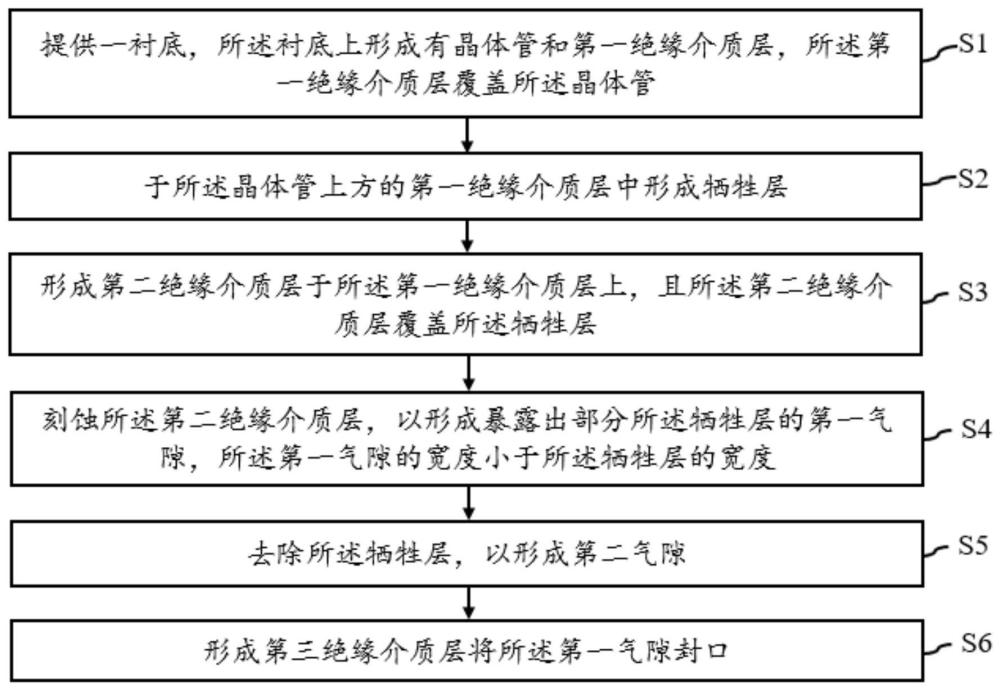

2、为实现上述目的,本发明提供了一种半导体器件的制造方法,包括:

3、提供一衬底,所述衬底上形成有晶体管和第一绝缘介质层,所述第一绝缘介质层覆盖所述晶体管;

4、于所述晶体管上方的第一绝缘介质层中形成牺牲层;

5、形成第二绝缘介质层于所述第一绝缘介质层上,且所述第二绝缘介质层覆盖所述牺牲层;

6、刻蚀所述第二绝缘介质层,以形成暴露出部分所述牺牲层的第一气隙,所述第一气隙的宽度小于所述牺牲层的宽度;

7、去除所述牺牲层,以形成第二气隙;

8、形成第三绝缘介质层将所述第一气隙封口。

9、可选地,所述晶体管包括形成于所述衬底上的栅极结构以及形成于所述栅极结构两侧衬底中的源极区和漏极区。

10、可选地,在形成所述第二绝缘介质层于所述第一绝缘介质层上之前,所述半导体器件的制造方法还包括:

11、于所述源极区和所述漏极区上均形成贯穿所述第一绝缘介质层的至少一个导电插塞,或者,于所述栅极结构、所述源极区和所述漏极区上均形成贯穿所述第一绝缘介质层的至少一个导电插塞。

12、可选地,所述牺牲层形成于所述栅极结构上方;和/或,所述牺牲层形成于所述源极区上的所述至少一个导电插塞与所述栅极结构上的所述至少一个导电插塞之间;和/或,所述牺牲层形成于所述漏极区上的所述至少一个导电插塞与所述栅极结构上的所述至少一个导电插塞之间。

13、可选地,所述导电插塞与所述牺牲层同时形成。

14、可选地,在形成所述第二绝缘介质层于所述第一绝缘介质层上之后且在形成暴露出部分所述牺牲层的第一气隙之前,所述半导体器件的制造方法还包括:

15、于所述源极区和/或所述漏极区和/或所述栅极结构上的至少一个导电插塞上形成贯穿所述第二绝缘介质层的金属互连线;相邻两条所述金属互连线的间距大于所述牺牲层的宽度。

16、可选地,所述牺牲层的材质为钨或铜。

17、可选地,采用湿法刻蚀工艺去除所述牺牲层。

18、本发明还提供一种半导体器件,包括:

19、衬底,所述衬底上形成有晶体管和第一绝缘介质层,所述第一绝缘介质层覆盖所述晶体管;

20、第二气隙,形成于所述晶体管上方的第一绝缘介质层中;

21、第二绝缘介质层和第一气隙,所述第二绝缘介质层形成于所述第一绝缘介质层上,所述第一气隙形成于所述第二气隙上的第二绝缘介质层中,所述第一气隙与所述第二气隙连通,且所述第一气隙的宽度小于所述第二气隙的宽度;

22、第三绝缘介质层,将所述第一气隙封口。

23、可选地,所述晶体管包括形成于所述衬底上的栅极结构以及形成于所述栅极结构两侧衬底中的源极区和漏极区。

24、可选地,所述半导体器件还包括:

25、至少一个导电插塞,所述源极区和所述漏极区上均形成有贯穿所述第一绝缘介质层的所述至少一个导电插塞,或者,所述栅极结构、所述源极区和所述漏极区上均形成有贯穿所述第一绝缘介质层的所述至少一个导电插塞。

26、可选地,所述第二气隙形成于所述栅极结构上方;和/或,所述第二气隙形成于所述源极区上的所述至少一个导电插塞与所述栅极结构上的所述至少一个导电插塞之间;和/或,所述第二气隙形成于所述漏极区上的所述至少一个导电插塞与所述栅极结构上的所述至少一个导电插塞之间。

27、可选地,所述半导体器件还包括:

28、金属互连线,形成于所述源极区和/或所述漏极区和/或所述栅极结构上的所述至少一个导电插塞上的所述第二绝缘介质层中,相邻两条所述金属互连线的间距大于所述第二气隙的宽度。

29、可选地,所述第二绝缘介质层为多层堆叠结构。

30、与现有技术相比,本发明的技术方案具有以下有益效果:

31、1、本发明的半导体器件的制造方法,通过于晶体管上方的第一绝缘介质层中形成牺牲层;形成第二绝缘介质层于所述第一绝缘介质层上,且所述第二绝缘介质层覆盖所述牺牲层;刻蚀所述第二绝缘介质层,以形成暴露出部分所述牺牲层的第一气隙,所述第一气隙的宽度小于所述牺牲层的宽度;去除所述牺牲层,以形成第二气隙;形成第三绝缘介质层将所述第一气隙封口,使得半导体器件的寄生电容得到降低。

32、2、本发明的半导体器件,由于包括:第二气隙,形成于晶体管上方的第一绝缘介质层中;第二绝缘介质层和第一气隙,所述第二绝缘介质层形成于所述第一绝缘介质层上,所述第一气隙形成于所述第二气隙上的第二绝缘介质层中,所述第一气隙与所述第二气隙连通,且所述第一气隙的宽度小于所述第二气隙的宽度;第三绝缘介质层,将所述第一气隙封口,使得半导体器件的寄生电容得到降低。

- 还没有人留言评论。精彩留言会获得点赞!