半导体器件及其制作方法与流程

本技术涉及半导体,具体而言,涉及一种半导体器件及其制作方法。

背景技术:

1、电力电子器件是现代电力电子技术的核心,它作为能源转换装置最基础的元件之一,决定着系统的整体性能。电力电子器件性能的好坏,将直接影响整个能源转换装置的转换效率。

2、宽禁带半导体材料碳化硅sic mosfet(metal-oxide-semiconductor field-effect transistor,金属氧化物半导体场效应晶体管)非常适合用于研制高温、大功率、高频功率器件,用sic材料制备的器件比si器件的功耗降低了50%,并且在峰值功率下,工作效率大于96%,开关频率比硅器件提高数十倍,同时,碳化硅的热导率高达4.9j.k.cm,甚至优于金属铜,又可以在更高的温度下(300℃以上)工作,散热系统可以大大简化甚至可以完全取消,最终使整个系统的体积和重量显著降低。

3、目前sic mosfet有平面栅和沟槽栅两种不同的结构类型。平面栅结构具有结构简单、容易制造、高可靠性等优点,是行业内应用最早、最广泛、最可靠的架构。然而在减小芯片尺寸和提高产能的驱动下,平面栅其横向拓扑结构限制了它最终可以缩小的程度。沟槽栅结构是一种改进的技术,与平面栅相比,沟槽栅mosfet去除了jfet区,不存在jfet(junction field-effect transistor,结型场效应晶体管)电阻,所以沟槽栅的特征电阻比平面栅要小,因此可以使用更少的sic原材料制备沟槽栅mosfet,从而提高产量。

4、然而,沟槽栅型sic mosfet也存在一些问题,比如,现有的沟槽栅型sic mosfet的导通电阻较高。

技术实现思路

1、本技术的主要目的在于提供一种半导体器件及其制作方法,以至少解决现有技术中沟槽型mosfet的导通电阻较高,影响器件性能的技术问题。

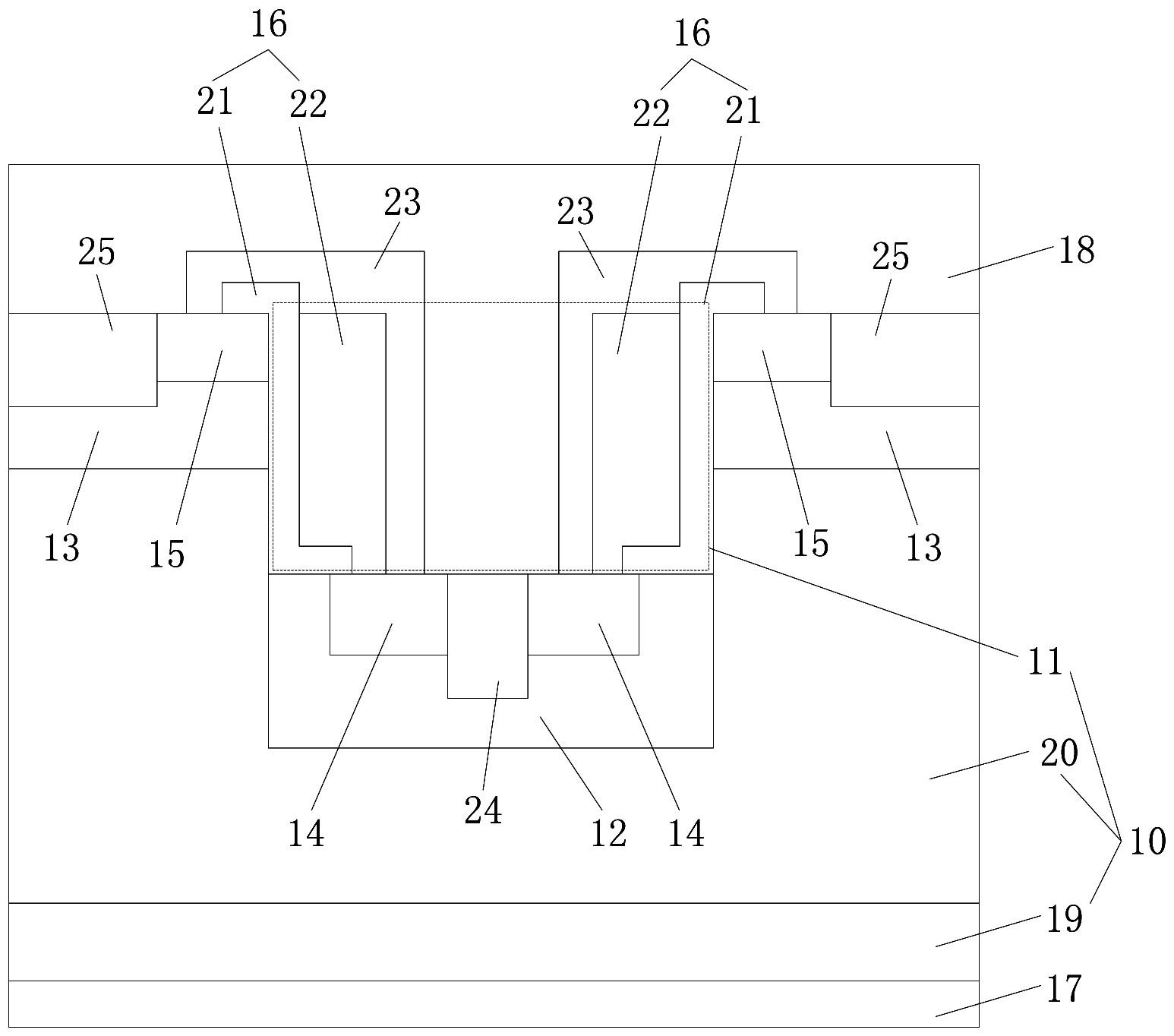

2、为了实现上述目的,根据本技术的一个方面,提供了一种半导体器件,包括:基底,具有沟槽;第一阱区以及第二阱区,所述第一阱区位于所述基底中且与所述沟槽的底部接触,所述第二阱区位于所述沟槽至少一侧的所述基底中,所述第一阱区与所述第二阱区的掺杂类型相同;第一掺杂区和第二掺杂区,所述第一掺杂区位于第一阱区中,所述第二掺杂区位于所述第二阱区中,所述第一掺杂区、所述第二掺杂区以及所述基底的掺杂类型相同,且不同于所述第一阱区的掺杂类型,所述第一掺杂区以及所述第一阱区的部分表面构成所述沟槽的部分底壁,所述第二掺杂区以及所述第二阱区的部分表面构成所述沟槽的部分侧壁;栅极结构,所述栅极结构至少覆盖所述沟槽的侧壁、所述沟槽的底壁中所述第一阱区的部分表面以及所述第一掺杂区的部分表面;第一金属层和第二金属层,所述第一金属层位于所述基底远离所述沟槽的表面上,所述第二金属层位于所述第一掺杂区和所述第二掺杂区远离所述第一金属层的表面上。

3、可选地,所述基底包括:衬底,所述第一金属层位于所述衬底的表面上;外延层,位于所述衬底远离所述第一金属层的表面上,所述沟槽、所述第一阱区以及所述第二阱区分别位于所述外延层中,所述外延层与所述衬底的掺杂类型相同,且不同于第一阱区的掺杂类型,所述外延层的掺杂浓度小于所述衬底的掺杂浓度。

4、可选地,所述第二掺杂区远离所述衬底的表面构成所述外延层远离所述衬底的部分表面,所述栅极结构包括:栅氧化层,位于所述第二掺杂区远离所述衬底的部分表面上、所述沟槽的侧壁上、所述第一阱区远离所述衬底的表面上以及所述第一掺杂区远离所述衬底的部分表面上;栅极,位于所述栅氧化层远离所述沟槽侧壁的部分表面上以及所述第一掺杂区远离所述衬底的部分表面上,所述半导体器件还包括:介质层,位于所述外延层与所述第一掺杂区的远离所述衬底的部分表面上、所述栅氧化层与所述栅极的远离所述衬底的表面上以及所述栅氧化层与所述栅极的远离所述沟槽侧壁的表面上。

5、可选地,所述第一掺杂区以及所述第二掺杂区的掺杂浓度分别大于所述外延层的掺杂浓度。

6、可选地,所述半导体器件还包括:第三掺杂区,位于所述第一阱区中,且与所述第一掺杂区接触;第四掺杂区,位于所述第二阱区中,且与所述第二掺杂区接触,所述第三掺杂区与所述第四掺杂区的掺杂类型相同,且不同于所述第一掺杂区的掺杂类型,所述第二金属层还覆盖所述第三掺杂区的部分表面。

7、可选地,所述第三掺杂区的掺杂浓度大于所述第一阱区的掺杂浓度,所述第四掺杂区的掺杂浓度大于所述第二阱区的掺杂浓度。

8、可选地,所述第一金属层包括沿远离所述基底方向依次叠置的第一金属子层、第二金属子层、第三金属子层和第四金属子层,所述第二金属层包括沿远离所述基底方向依次叠置的第五金属子层、第六金属子层和第七金属子层,其中,所述第一金属子层、所述第三金属子层和所述第五金属子层的材料分别包括镍,所述第二金属子层以及所述第六金属子层的材料分别包括钛,所述第四金属子层的材料包括银,所述第七金属子层的材料包括铝。

9、根据本技术的另一方面,提供了一种所述的半导体器件的制作方法,包括:提供具有沟槽的初始基底;对所述初始基底进行离子注入,以在所述初始基底中形成第一初始阱区以及第二初始阱区,剩余的所述初始基底形成基底,所述第一初始阱区与所述沟槽的底部接触,所述第二初始阱区位于所述沟槽的至少一侧;对所述第一初始阱区和所述第二初始阱区进行离子注入,以至少在所述第一初始阱区中形成第一掺杂区,以及在所述第二初始阱区中形成第二掺杂区,剩余的所述第一初始阱区形成第一阱区,剩余的所述第二初始阱区形成第二阱区,其中,所述第一阱区与所述第二阱区的掺杂类型相同,所述第二掺杂区位于所述第二阱区中,所述第一掺杂区、所述第二掺杂区以及所述基底的掺杂类型相同,且不同于所述第一阱区的掺杂类型,所述第一掺杂区以及所述第一阱区的部分表面构成所述沟槽的部分底壁,所述第二掺杂区以及所述第二阱区的部分表面构成所述沟槽的部分侧壁;至少在所述沟槽的侧壁、所述沟槽的底壁中所述第一阱区的裸露表面以及所述第一掺杂区的部分裸露表面上形成栅极结构;在所述基底远离所述沟槽的表面上形成第一金属层,以及在所述第一掺杂区和所述第二掺杂区的裸露表面上形成第二金属层。

10、可选地,提供具有沟槽的初始基底,包括:提供衬底;在所述衬底的表面上形成初始外延层,所述初始外延层与所述衬底的掺杂类型相同,且不同于第一阱区的掺杂类型;去除部分的所述初始外延层,以形成伸入所述初始外延层中的所述沟槽,剩余的所述初始外延层形成中间外延层,对所述初始基底进行离子注入,以在所述初始基底中形成第一初始阱区以及第二初始阱区,包括:在所述沟槽两侧的所述中间外延层远离所述衬底的表面上形成第一阻挡层;对形成有所述第一阻挡层的所述中间外延层进行离子注入,以在所述沟槽底部的所述中间外延层中形成所述第一初始阱区,以及在所述沟槽两侧的所述中间外延层中形成所述第二初始阱区,剩余的所述中间外延层形成所述外延层;去除所述第一阻挡层。

11、可选地,至少在所述沟槽的侧壁、所述沟槽的底壁中所述第一阱区的裸露表面以及所述第一掺杂区的部分裸露表面上形成栅极结构,包括:在所述沟槽的侧壁和底壁、所述第二掺杂区的裸露表面以及所述外延层的裸露表面上形成初始栅氧化层;对所述初始栅氧化层进行刻蚀操作,保留位于所述第二掺杂区远离所述衬底的部分表面上、所述沟槽的侧壁上、所述第一阱区远离所述衬底的表面上以及所述第一掺杂区远离所述衬底的部分表面上的所述初始栅氧化层,得到所述栅氧化层;在所述栅氧化层的至少部分裸露表面上形成栅极,得到所述栅极结构。

12、应用本技术的技术方案,半导体器件中,沟槽底部的基底中设置有与基底的掺杂类型不同的第一阱区,第一阱区中形成有与第一阱区掺杂类型不同的第一掺杂区,通过栅极结构连接该第一阱区和第一掺杂区,从而在栅极结构与第一阱区接触的表面形成第一个沟道区;沟槽一侧的基底中设置有与基底的掺杂类型不同的第二阱区,第二阱区中形成有与第二阱区掺杂类型不同的第二掺杂区,通过栅极结构连接第二阱区和第二掺杂区,从而在栅极结构与第二阱区接触的表面形成第二个沟道区,因此,本技术的所述半导体器件实现了双沟道区域,可以降低整个半导体器件的导通电阻,提升半导体器件的整体性能。

- 还没有人留言评论。精彩留言会获得点赞!