半导体器件的制作方法

背景技术:

1、迄今为止,功率电子应用中使用的晶体管通常由硅(si)半导体材料制成。功率应用常见的晶体管器件包括硅硅功率mosfet和硅绝缘栅双极晶体管(igbt)。

2、在一些应用中,两个或更多半导体器件被集成在公共半导体衬底内。取决于应用,可能期望将器件之一与半导体衬底以及与半导体衬底中的其他器件电隔离。us2019/098666a1公开了一种包括耗尽式mosfet器件和嵌入式二极管的器件。嵌入式二极管通过位于二极管阳极和mosfet源极之间的隔离区进行结隔离。

3、期望对包括集成在公共半导体衬底中的两个或更多器件的半导体器件进行改进。

技术实现思路

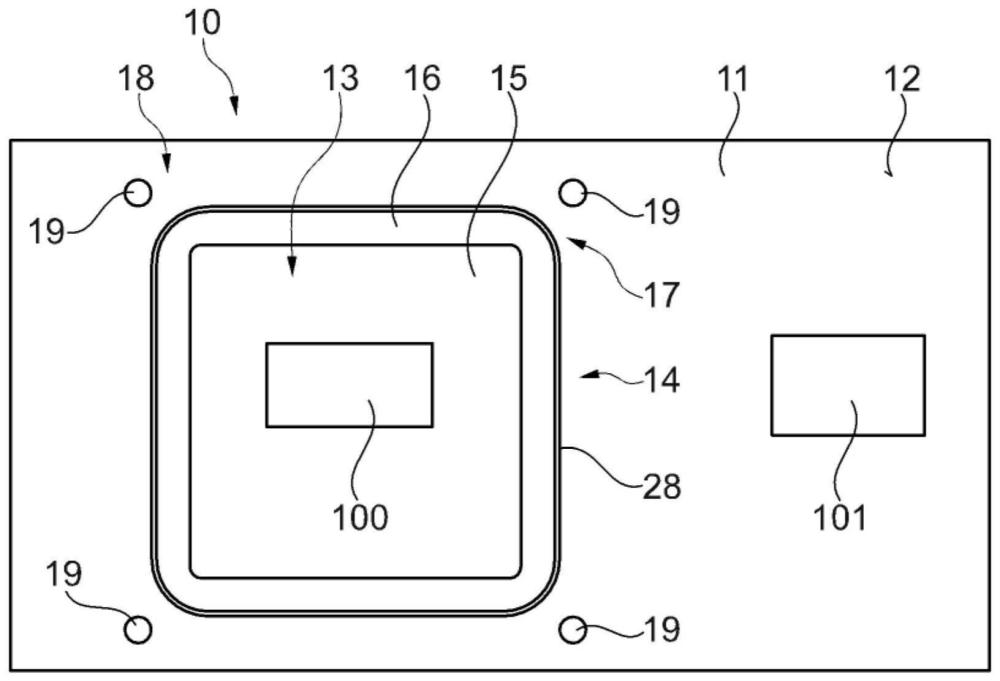

1、根据本发明,提供了一种半导体器件,其包括第一导电类型的半导体衬底,该半导体衬底包括第一主表面。第一器件区形成在半导体衬底中并具有第一导电类型。第一器件区具有横向范围,该横向范围小于半导体衬底的第一表面的横向范围。第一器件区通过隔离结构与半导体衬底电分离。隔离结构包括用与第一导电类型相反的第二导电类型掺杂的掩埋层,并且还包括第二导电类型的第一细长下沉区(sinker)。第一细长下沉区从第一表面延伸到半导体衬底中,并且与掩埋层电接触。半导体器件还包括第二导电类型的击穿电压影响结构,该击穿电压影响结构布置在半导体衬底中并且横向邻近掩埋层。

2、该半导体器件包括形成在半导体衬底中的第一器件区域,该第一器件区域通过隔离结构与半导体衬底的其余部分电分离。半导体衬底的其余部分可以提供一个或多个另外的器件区域。第一器件区域占据第一主表面的一小部分,即小于第一主表面的区域的50%。隔离结构包括与半导体衬底和第一器件区域的导电类型相反的导电类型,并且包括掩埋层和第一下沉区,掩埋层和第一下沉区二者包括第二导电类型的材料。掩埋层位于半导体衬底的体积内,并且与半导体衬底的第一主表面以及还与相对的第二主表面间隔开。掩埋层将第一器件区与半导体衬底的下面部分垂直绝缘。掺杂的第一细长下沉区电接触掩埋层,并为半导体衬底提供第一器件区的横向绝缘。

3、击穿电压影响结构包括第二导电类型,并且位于半导体衬底中横向邻近掩埋层并且在第一器件区域横向外部。击穿电压影响结构用于增加绝缘结构相对于衬底的击穿电势。因此,改进了半导体器件的隔离强度。

4、击穿电压影响结构可以具有不同的形式。例如,击穿影响结构可以包括掺杂有第二导电类型的掩埋区和/或包括第二导电类型的第二细长下沉区。在一些实施例中,击穿电压影响结构是第一细长下沉区的组成部分。

5、使用具有开口区域的掩模制造掩埋层和第一下沉区,通过该开口区域将掺杂剂注入半导体衬底。例如,用于掩埋层的第一掩模可以具有由连续边缘限定的基本上正方形或矩形的开口。用于下沉区的第二掩模可以包括环形开口。设计掩模,使得在对准状态下,第二掩模中的环形开口位于用于掩埋层的第一掩模中开口的垂直上方并与其重叠。两个掩模(即掩埋层的注入掩模和第一下沉区的沟槽掩模)的开口区域可以被设计为重叠,例如具有相同的外部开口边缘。

6、为了优化第一下沉区接触电阻和击穿电压,在一些实施例中,对于长边,选择第二下沉区和掩埋层边缘之间的较小间距,以减小下沉区接触电阻,并且在拐角处选择较大间距,以增加拐角击穿电压。可以选择间距,使得拐角和直边处的击穿电压相似或尽可能相似。

7、在一些实施例中,击穿电压影响结构包括从第一表面延伸到半导体衬底中的第二导电类型的第二下沉区。第二下沉区与掩埋层横向邻近布置。在一些实施例中,第二下沉区通过半导体衬底的一部分与掩埋层横向隔开。

8、掩埋层具有横向范围。第二下沉区布置在掩埋层区域和第一器件区域横向外部,而第一下沉区布置在掩埋层区域的横向内部或内。

9、掩埋层以及第一和第二下沉区的横向范围部分地由用于形成相应结构的掩模确定。这里描述的掩埋层与第一和第二下沉区的相对布置对应于掩埋层与第一和第二下沉区的相应掩模的相对布置。

10、第一细长下沉区可以具有连续的环形形状,其横向并连续地围绕第一器件区。第一细长下沉区可以沿其整个长度与掩埋层接触,或者可以在一个或多个分立区与掩埋层接触,以便使细长的第一下沉区与掩埋层电接触,并将第一器件区与半导体衬底电分离。

11、为了降低寄生pnp增益,可以在拐角处提供第二下沉区。内部第一下沉区在具有较高bl浓度(较高的基极浓度用于较低的增益)的位置连接掩埋层。外部第二下沉区提供较高的击穿电压,并屏蔽内部下沉区免受高电场的影响。两个下沉区可以形成t形连接,或者一个下沉区可以在另一个附近终止,导致重叠的向外扩散的轮廓高度集中。也可以使用两个或更多圆周连续下沉区。

12、在n掺杂掩埋层(bl)和p掺杂衬底的情况下,第二下沉区可以是电浮置的或者连接到具有比第一器件区更低的电势的电压源。在p掺杂(bl)和n掺杂衬底的情况下,第二下沉区可以是电浮置的或连接到具有比第一器件区更高的电势的电压源。

13、在一些实施例中,添加第二下沉区,与掩埋层的边缘具有间距。该间距指的是用于掩埋层的掩模中的开口边缘和用于第二下沉区的掩模中的开口边缘之间的空间。可以调整间距以获得特定的击穿电压。例如,在一组模拟条件下,在没有浮置的第二下沉区的比较情况中观察到的大约165v的击穿电压随着间距的增加而减小,然后其增加并在192v处达到峰值。

14、在一些实施例中,通过将掺杂的bsg/psg预沉积到形成在第一主表面中的沟槽中,然后进行相当短的向外扩散,来制造下沉区。向外扩散的低温预算导致陡的掺杂浓度梯度,该陡的掺杂浓度梯度比掩埋层的掺杂梯度陡得多。

15、在一些实施例中,击穿电压影响结构包括第二导电类型的至少一个掩埋区,该至少一个掩埋区与掩埋层横向邻近布置。在一些实施例中,掩埋区通过半导体衬底的一部分与掩埋层隔开。掩埋区被横向布置在掩埋层的横向范围的外侧,并且被布置在半导体衬底中横向邻近第一器件区并且在第一器件区横向外部。

16、在一些实施例中,掩埋层在平面视图中具有多边形形式,具有至少三个拐角。一个掩埋区被布置成横向邻近掩埋层的一个拐角。在一些实施例中,一个掩埋层被布置成横向邻近掩埋层的每个拐角。典型地,掩埋层具有正方形或矩形的形式,并且具有四个拐角,并且一个掩埋区被布置成横向邻近每个拐角,从而提供四个分立的掩埋区。拐角处的掩埋层掩模可以是圆形的或倒角的,或者可以包括多边形。在向外扩散之后,典型的圆形半径可以归因于掩埋层区。

17、击穿电压也是曲率半径的函数,使得拐角处的曲率半径进一步降低击穿电压。因此,与条形几何形状(即在拐角之间延伸的直边)相比,掩埋层的拐角具有较低的击穿电压。因此,与拐角之间延伸的区相比,拐角处的击穿影响结构可能不同。由于在掩埋层的典型圆形拐角处降低的击穿电压,在一些实施例中,击穿电压影响结构仅布置在拐角附近,以便局部增加拐角区中的击穿电压。

18、在一些实施例中,击穿电压影响结构包括第二导电类型的第二下沉区和第二导电类型的至少一个掩埋区。在一些实施例中,掩埋区与第二下沉区重叠。第二下沉区从第一主表面延伸到半导体衬底中,并且具有与掩埋区重叠并且可以位于掩埋区中的基极。

19、在一组模拟条件下,在没有浮置的第二下沉区的比较情况中观察到的大约165v的击穿电压随着间距的增加而减小,然后其增加并在192v处达到峰值。使用浮置掩埋层代替第二下沉区允许击穿电压高达206v。连接到下沉区的浮置掩埋层的组合允许甚至更高的击穿电压。

20、在一些实施例中,在隔离结构外部提供一个或多个第二下沉区或掩埋区。下沉区和/或掩埋区可以具有细长形式、环形形式或气泡形式。对于n掺杂的掩埋区和/或下沉区和p掺杂的衬底,下沉区和/或掩埋区可以是电浮置的或连接到比第一器件区更低电势的电压源。对于p掺杂的掩埋区和/或下沉区以及n掺杂的衬底,下沉区和/或掩埋区可以是电浮置的或连接到比第一器件区更高电势的电压源。浮置掩埋区可以在第一器件区周围形成闭环结构。

21、在一些实施例中,第一下沉区的一部分横向位于掩埋层内部并与掩埋层接触,并且第一下沉区的另一部分横向位于掩埋层外部以增加击穿电压。第一下沉区的横向位于掩埋层外部的这部分提供了击穿影响结构。第一下沉区的横向位于掩埋层外部的不与掩埋层直接接触的部分可以用于提供具有更高击穿电压的半导体器件的隔离结构。第一下沉区的路径穿过掩埋层的横向范围。仅通过修改用于形成掩埋层和下沉区的掩模,就可以实现击穿电压的增加。

22、在一些实施例中,第一细长下沉区的第一区段与掩埋层重叠,并且第一细长下沉区的第二区段布置为横向邻近掩埋层。布置为横向邻近掩埋层的该第二区段提供了击穿影响结构。在该实施例中,击穿电压影响结构与第一细长下沉区集成。第二区段布置在掩埋层的横向范围的横向外侧,并且第一区段布置在掩埋层的横向范围的横向内侧。因此,第一细长下沉区穿过限定掩埋层横向范围的边界。

23、在一些实施例中,至少一个下沉区完全在掩埋层的横向范围内部。该实施例可以用于实现下沉区和掩埋层之间的最低欧姆连接。

24、在一些实施例中,掩埋层在平面视图中具有多边形形式,具有至少三个拐角,并且第一细长下沉区的第二区段布置成横向邻近至少一个拐角。第一细长下沉区的第二区段与掩埋层横向隔开,而细长下沉区的第一区段与掩埋层重叠。第一细长下沉区的第二区段位于第一器件区的横向外部,并且第一区段位于第一器件区的横向内部,其中横向表示平行于第一主表面的方向。第二区段用于增加拐角处的隔离结构的击穿电压,使得沿着第一器件区外围的击穿电压更加均匀。这可以有助于防止掩埋层拐角处的过早击穿。

25、可以为每个拐角提供一个这样的第一细长下沉区。换句话说,为单个掩埋层提供多个分立分离的第一下沉区,这些第一下沉区围绕掩埋层的外围隔开。在其他实施例中,提供单个连续的第一细长下沉区,其具有一个第二区段,该第二区段在每个拐角处位于掩埋层的横向外部。第一下沉区的中间直区段位于掩埋层区域内部,并与掩埋层接触。

26、在一些实施例中,半导体器件的击穿电压影响结构还包括从第一表面延伸到掩埋层并且与掩埋层电接触的第三细长下沉区。第三细长下沉区可包括第二导电类型。

27、第三细长下沉区可以位于第一细长下沉区的横向内部,并且更靠近第一器件区的中心。在一些实施例中,第三细长下沉区具有连续的环形形式,并且横向且连续地围绕器件区。在该实施例中,第三下沉区连续电接触掩埋层。第一细长下沉区可位于第三细长下沉区的横向外侧,并与第三细长下沉区隔开。在包括连续环形第三下沉区的一些实施例中,根据下面描述的实施例之一,为掩埋层的每个拐角提供一个第一细长下沉区,并且该第一细长下沉区与其相应的拐角具有基本相同的关系。

28、在一些实施例中,击穿电压影响结构具有连续的环形形式,并且横向围绕第一器件区。击穿影响结构可以包括掩埋区、第二下沉区、具有其远端的第一下沉区结构和第三下沉区结构中的一个或多个。

29、在一些实施例中,第一细长下沉区的第二区段形成第一细长下沉区的中心区段,并且第一细长下沉区的中心区段布置成横向邻近掩埋层并与掩埋层隔开。第一中心区段位于掩埋层的横向外部。细长下沉区的第一中心区段包括两个远端区段,每个远端区段位于中心区段的相对端。每个远端区段与掩埋层重叠并且在掩埋层的横向范围内部。远端区段可位于与第三细长下沉区横向邻近并隔开一段距离,该距离小于中心区段与第三细长下沉区之间的距离。远端区段与掩埋层电接触。

30、在一些实施例中,远端设置的每个远端区段的端面被布置成基本上垂直于第三细长下沉区。在其他实施例中,每个远端区段具有基本平行于第三细长下沉区延伸的最外或末端区段。

31、在一些实施例中,第一细长下沉区具有连续的环形形式,并且横向围绕第一器件区。在一些实施例中,第一和第三细长下沉区二者都具有连续的环形形式,并且横向围绕第一器件区,由此第一细长下沉区被布置在第三细长下沉区的横向外侧。在一些实施例中,第一、第二和第三细长下沉区每个都具有连续的环形形式,并且横向且连续地围绕第一器件区,其中第二细长下沉区布置在第三细长下沉区的横向外侧,并且第一细长下沉区布置在第二细长下沉区的横向外侧,使得第二细长下沉区布置在第一和第三细长下沉区之间。

32、如果使用的话,第一细长下沉区、第二细长下沉区和第三细长下沉区可以具有不同的形式。第一、第二和第三下沉区的每一个可以具有相同的形式,或者可以具有不同的形式。在一些实施例中,第一细长下沉区和/或第二细长下沉区和/或第三细长下沉区包括从第一表面延伸到半导体衬底中的沟槽。沟槽填充有材料,例如n掺杂的bsg(硼硅酸盐玻璃)或psg(磷硅酸盐玻璃)或未掺杂的玻璃或其他绝缘体。

33、在一些实施例中,掺杂的bsg或psg材料经受加热,以引起掺杂剂从bsg或psg向外扩散,并在邻近沟槽的半导体衬底中形成掺杂区。该掺杂区形成下沉区。掺杂区可以具有第二导电类型。稍后去除bsg或psg材料,并且用由未掺杂的氧化物、氮化物、多晶硅、硅、硅化物、金属或空腔中的一种或多种形成的一层或多层填充沟槽。在这些实施例中,在最终的半导体器件中,沟槽可以包括电绝缘结构,并且下沉区(视情况而定,第一细长下沉区和/或第二细长下沉区和/或第三细长下沉区)由布置在横向邻近沟槽的半导体衬底中的第二导电类型的掺杂区形成。

34、在其他实施例中,第一细长下沉区和/或第二细长下沉区和/或第三细长下沉区包括掺杂有第二导电类型的掺杂剂的半导体衬底区。这种结构可以借助于具有一个或多个开口的掩模通过将掺杂剂注入到衬底中来形成,所述一个或多个开口具有对应于半导体衬底中相应下沉区的期望横向形状的形式,掺杂剂通过开口来注入,通过所述开口,掺杂剂被注入。

35、在一些实施例中,第二细长下沉区和掩埋区是电浮置的。

36、在一些实施例中,掩埋层具有带中心最大区和尾部区的掺杂分布,中心最大区横向延伸到尾部区中,所述尾部区具有作为距中心最大区的横向距离的函数而降低的掺杂水平。尾部区位于掩埋层的横向边缘。击穿电压影响结构还可以具有掺杂分布,该掺杂分布具有最大区和尾部区,中心最大区横向延伸到尾部区中,所述尾部区具有作为距中心最大区的横向距离的函数而降低的掺杂水平。尾部区位于击穿影响结构的横向边缘,例如第一下沉区、掩埋区或第二下沉区或第三下沉区(如果使用的话)的横向边缘。

37、在用氧化物填充或加衬的沟槽的情况下,从侧壁的向外扩散导致形成具有两个最大值而没有恒定区的掺杂分布,并且存在从两个最大值中的每一个的单侧向外扩散。

38、在一些实施例中,掩埋层具有带中心最大区和尾部区的掺杂分布,并且击穿电压影响结构包括一个或多个沟槽,所述一个或多个沟槽内衬有氧化物和可选掺杂的多晶硅。多晶硅可以是n掺杂的或p掺杂的。击穿影响结构还包括邻近沟槽的掺杂下沉区。掩埋层的尾部区与击穿电压影响结构的掺杂下沉区在击穿影响结构布置成横向邻近掩埋层的区中重叠,和/或击穿电压影响结构的最大区与掩埋层的最大区在击穿电压影响结构与掩埋层电接触的区中重叠。

39、掺杂的下沉区可以通过掺杂剂从沟槽内的材料的早期向外扩散来形成。这种材料可能在向外扩散之后被去除,并且然后在沟槽中形成氧化物和掺杂多晶硅。

40、在一些实施例中,掩埋层的尾部区与击穿电压影响区的尾部区在击穿电压影响结构布置为横向邻近掩埋层的一个或多个位置中重叠。

41、在一些实施例中,击穿电压区的最大区的至少一部分与掩埋层的最大区的至少一部分在击穿电压影响结构与掩埋层电接触的区中重叠。

42、可以通过调整掺杂分布的重叠来调整击穿电压影响结构和掩埋层之间的电接触的电阻。例如,为了降低电阻,击穿电压影响区的最大掺杂区被布置成与掩埋层的掺杂区的最大区重叠。在期望电阻更大或者没有电接触的其他区中,具有较低掺杂浓度的击穿电压影响区的尾部区被调整为与具有较低掺杂浓度的掩埋层的尾部区重叠。

43、在一些实施例中,第一下沉区的尾部区的掺杂浓度的降低dd/dx大于掩埋层的尾部区的掺杂浓度的降低dd/dx。在这些实施例中,第一下沉区的尾部区具有比掩埋层的尾部区更小的横向范围。

44、在一些实施例中,掩埋层的高度是第一下沉区宽度的至少两倍或至少三倍或至少四倍,掩埋层的高度由在掩埋层和半导体衬底之间形成的上pn结和在掩埋层和半导体衬底之间形成的下pn结之间的垂直距离定义,所述宽度被定义为在第一下沉区和半导体衬底之间形成的相对pn结之间的横向距离。

45、第一半导体器件可以布置在第一器件区中,并且第二半导体器件布置在半导体衬底中与第一器件区横向邻近。半导体衬底可以包括一个或多个第二器件区,并且第二半导体器件布置在第二器件区中。

46、例如,第一半导体器件可以是栅极驱动器,例如用于半桥电路的高侧开关的栅极驱动器,并且第二半导体器件可以是用于半桥电路的低侧开关的栅极驱动器。在其他实施例中,第一半导体器件可以是逻辑器件,并且第二半导体器件可以是功率器件,例如功率晶体管器件。

47、多于一个的半导体器件可以布置在半导体衬底的第二器件区中。例如,电连接以与半桥电路的低侧开关的栅极驱动器一起形成半桥电路的两个功率晶体管器件可以布置在半导体器件的第二器件区中,并且半桥电路的高侧开关的栅极驱动器可以布置在通过隔离结构与半导体衬底电分离的第一器件区中。在第一器件区中可以布置多于一个器件。半导体衬底还可以包括多于一个的第一器件区,每个第一器件区通过根据这里描述的任何一个实施例的隔离结构与半导体衬底电分离。

48、本领域技术人员在阅读以下详细描述和查看附图后将认识到附加的特征和优点。

- 还没有人留言评论。精彩留言会获得点赞!