半导体器件及其制造方法与流程

本公开总体上涉及半导体器件,尤其涉及半导体器件及其制造方法。

背景技术:

1、mos(metal oxide semiconductor金属氧化物半导体)晶体管是现在芯片或集成电路(ic)领域中最重要的一种基本电子元件,被广泛地应用于汽车和工业应用,例如cmos(互补金属氧化物半导体complementary metal oxide semiconductor)技术。通常,完整的芯片或ic包括许多个mos管,为了防止这些临近的晶体管之间发生干扰,相邻的mos晶体管间必须加入用于电性隔离的隔离结构,其中典型的是深沟槽隔离技术。

2、目前使用的一种深沟槽隔离结构包括填充由第一导电材料的第一沟槽、填充有浮空第二导电材料的第二沟槽和填充有第二导电材料的第三沟槽,其中,第一沟槽连接至埋层,第三沟槽连接至衬底,第二沟槽在第一沟槽与第三沟槽之间以承受电压差。然而,此类深沟槽隔离结构的直流击穿电压(bv)是相对有限的。而且,在两个相邻的深沟槽隔离结构之间抽电流的状态下,会导致击穿电压进一步降低。另外,受限于沟槽的高度、深度和宽度的比值,第二沟槽底部的氧化物层厚度相对较小,均匀性相对欠佳。

3、因此,期望提供一种可靠、高性能、简单且成本有效的深沟槽隔离结构以及制造其的方法。

技术实现思路

1、鉴于以上内容,本公开的目的是提供一种用于解决或至少减轻现有技术的问题的半导体器件及其制造方法。

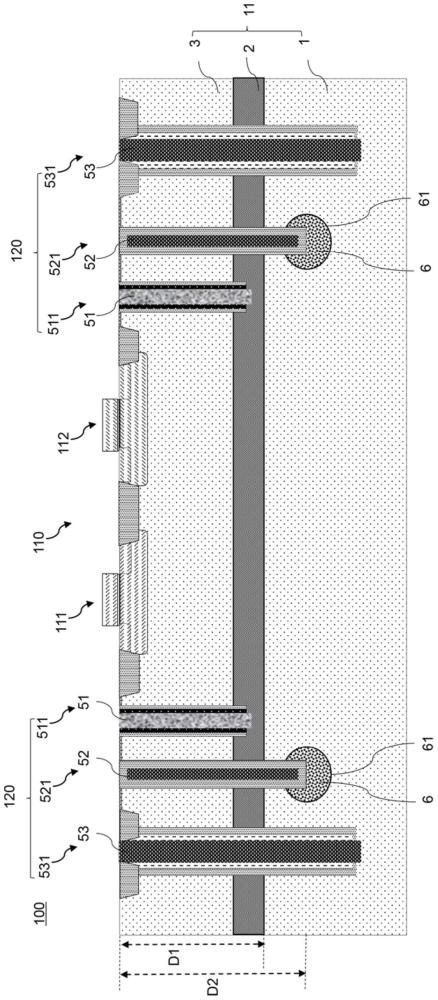

2、根据本公开的示例性方面,提供了一种半导体器件。该半导体器件包括:半导体主体,该导体主体包括衬底、设置在衬底之上的埋层以及设置在埋层之上的外延层,该衬底具有第一掺杂类型,所述埋层具有与第一掺杂类型相反的第二掺杂类型;第一沟槽,从外延层的顶表面延伸到埋层中或者外延层中靠近埋层的位置处;第二沟槽,从外延层的顶表面延伸到衬底中;第三沟槽,从外延层的顶表面延伸到衬底中;其中,第二沟槽位于第一沟槽与第三沟槽之间;第一深沟槽结构,设置在第一沟槽中,并且被配置为隔离外延层中的不同器件区域并将埋层电连接至外延层的顶表面;第二深沟槽结构,设置在第二沟槽中,并且被配置为隔离外延层中的不同器件区域;第三深沟槽结构,设置在第三沟槽中,并且被配置为隔离外延层中的不同器件区域并将衬底电连接至外延层的顶表面;以及其中,在第二深沟槽结构的底部处具有由第二掺杂类型的掺杂物所形成的掺杂区。

3、根据本公开的示例性方面,掺杂区是通过将掺杂物离子注入第二沟槽的底部处所形成的。

4、根据本公开的示例性方面,掺杂区与埋层隔离开。

5、根据本公开的示例性方面,第一掺杂类型为p型,第二掺杂类型为n型。当第一掺杂类型为p型,第二掺杂类型为n型时,掺杂物包括磷(p)、砷(as)、锑(sb)或其组合中的至少一项。

6、根据本公开的示例性方面,第一掺杂类型为n型,第二掺杂类型为p型。当第一掺杂类型为n型,第二掺杂类型为p型时,掺杂物可包括硼(b)、铝(al)、铟(in)或其组合中的至少一项。

7、根据本公开的示例性方面,第二沟槽的深度和/或埋层的深度能够被调整以改变第二沟槽与埋层的深度差,从而允许提高掺杂物的离子注入的注入剂量。

8、根据本公开的示例性方面,用于形成掺杂区的离子注入的注入能量选自5kev-100kev。根据本公开的示例性方面,用于形成掺杂区的离子注入的注入剂量选自5e11~1e15 cm2。

9、根据本公开的示例性方面,半导体器件还包括位于至少一个器件区域中的至少一个器件。根据本公开的示例性方面,半导体器件还包括形成在外延层中的隔离区域。该隔离区域可包括浅沟槽隔离区域。

10、根据本公开的另外的示例性方面,提供了一种用于制造半导体器件的方法。该方法包括:提供半导体主体,该半导体主体包括衬底、设置在衬底之上的埋层以及设置在埋层之上的外延层,衬底具有第一掺杂类型,埋层具有与第一掺杂类型相反的第二掺杂类型;在外延层的顶表面上形成硬掩模层;对硬掩模层和半导体主体进行刻蚀,以在半导体主体中形成第一沟槽、第二沟槽和第三沟槽,第一沟槽从外延层的顶表面延伸到埋层中或者外延层中靠近埋层的位置处,第二沟槽从外延层的顶表面延伸到衬底中,第三沟槽从外延层的顶表面延伸到衬底中,其中第二沟槽位于第一沟槽与第三沟槽之间;其中,在第一沟槽中形成第一深沟槽结构,该第一深沟槽结构被配置为隔离外延层中的不同器件区域并将埋层电连接至外延层的顶表面;在第二沟槽中形成第二深沟槽结构,该第二深沟槽结构被配置为隔离外延层中的不同器件区域;在第三沟槽中形成第三深沟槽结构,该第三深沟槽结构被配置为隔离外延层中的不同器件区域并将衬底电连接至外延层的顶表面。用于制造半导体器件的方法还包括将具有第二掺杂类型的掺杂物至少离子注入到第二沟槽的底部处,以形成位于第二沟槽的底部处的掺杂区。

11、根据本公开的示例性方面,用于制造半导体器件的方法进一步包括:在第一沟槽中形成第一深沟槽结构之后,在第二沟槽和第三沟槽中分别形成第二深沟槽结构和第三深沟槽结构;以及在形成第二深沟槽结构和第三深沟槽结构期间,将掺杂物离子注入第二沟槽和第三沟槽的底部处。

12、根据本公开的示例性方面,用于制造半导体器件的方法进一步包括:将掺杂物离子注入第一沟槽、第二沟槽和第三沟槽的底部处。

13、根据本公开的示例性方面,用于制造半导体器件的方法还包括形成用于掺杂物的离子注入的额外的掩模层,以允许提高掺杂物的离子注入的注入能量。

14、根据本公开的示例性方面,掺杂物的离子注入在对硬掩模层和半导体主体进行刻蚀以形成第二沟槽之后进行。

15、根据本公开的示例性方面,用于制造半导体器件的方法进一步包括:在第二沟槽的侧壁和底部上形成衬垫;在衬垫上形成介电层;对第一沟槽或第三沟槽进行各向异性刻蚀,使得第一沟槽的底部被打开以与埋层连接或第三沟槽的底部被打开以与衬底连接;以及利用导电材料填充第二沟槽。

16、根据本公开的示例性方面,用于制造半导体器件的方法还包括在第二沟槽的侧壁和底部上形成衬垫。掺杂物的离子注入可在形成衬垫之后进行。

17、根据本公开的示例性方面,用于制造半导体器件的方法还包括在衬垫上形成介电层。掺杂物的离子注入在沉积介电层之后进行。

18、根据本公开的示例性方面,用于制造半导体器件的方法还包括对第一沟槽或第三沟槽进行各向异性刻蚀,使得第一沟槽的底部被打开以与埋层连接或第三沟槽的底部被打开以与衬底连接。掺杂物的离子注入在对第一沟槽或第三沟槽进行各向异性刻蚀之后进行。

19、根据本公开的示例性方面,用于制造半导体器件的方法还包括利用导电材料填充第二沟槽。掺杂物的离子注入在填充导电材料之前的任何步骤之前进行。

20、根据本公开的示例性方面,用于制造半导体器件的方法包括化学机械抛光(cmp)工艺。根据本公开的另外示例性方面,用于制造半导体器件的方法还包括回蚀工艺。根据本公开的另外示例性方面,用于制造半导体器件的方法还包括剥离硬掩模层。

21、根据本公开的示例性方面,用于制造半导体器件的方法还包括在外延层中形成至少一个器件区域。根据本公开的另外示例性方面,用于制造半导体器件的方法还包括在外延层中形成多个隔离区域。

22、借助于本发明,能够显著提升连接高压的沟槽与连接低压的沟槽之间的直流击穿电压,从而增强深沟槽隔离结构在不同器件区域之间的隔离效果,使得提高半导体器件的可靠性。同时,借助于本发明,两个相邻的深沟槽隔离结构之间在抽电流状态下的击穿电压也相对得以提升。此外,在进行蚀刻操作以形成第二沟槽和第三沟槽之后进行掺杂物的离子注入,还可以促进在第二沟槽底部处的硅的非晶化,从而使得在后续形成衬垫的步骤中的氧化速度加快,且能够提高氧化物层的厚度,使氧化物层更均匀。

23、通常,权利要求中使用的所有术语应当根据其在技术领域中的普通含义进行解释,除非本文另有明确定义。除非另有明确说明,否则对“元素、装置、组件、部件”等的所有提及均应当公开解释为提及该元素、装置、组件、部件等的至少一个实例。

24、提供

技术实现要素:

部分是为了以简化的形式来介绍对概念的选择,它们在下文的具体实施方式中将被进一步描述。发明内容部分无意标识本公开内容的关键特征或主要特征,也无意限制本公开内容的范围。

- 还没有人留言评论。精彩留言会获得点赞!