一种多通道高压晶体管电路模块封装方法及其封装结构与流程

本发明属于电子封装,进一步来说涉及多通道高压混合集成电路模块封装领域,具体来说,涉及一种多通道高压晶体管电路模块封装方法及其封装结构。

背景技术:

1、近年来,随着现代化设备不断向智能化、小型化、轻便化方向发展,设备的电子线路也随之向密集化、小型化、单元化/模块化方向转变,从而对半导体分立器件提出了新的应用要求,即需利用异构整合封装技术将局部线路进行资源整合,以提高效能、降低成本、实现小型化发展。利用异构整合封装技术开发的半导体特种器件与集成电路有着本质上区别,半导体特种器件是通过资源整合,系统性地解决了半导体集成电路在工艺制程上遇到的难题,是集成电路构成功能系统发展道路上的重要补充手段。此外,半导体特种器件还要综合考虑热设计、功耗、线路互联等问题,属于综合性器件,因此无法被半导体单片集成电路所取代。半导体芯片制程工艺的不断提高,集成电路芯片中的晶体管越来越多,且越做越小,生产难度极具增大,量子隧穿效应带来的功耗也越来越明显。在使用更小的晶体管节点(小于20nm)缩小芯片的成本优势已经不再明显,导致行业力图提高系统性能和能效转向新技术节点的速度减缓,传统晶体管尺寸缩小和异构集成的整合变得迫在眉睫。因此,需要采用新的方法,即将单片式芯片分解成较小的芯片单元或片段,实现高功率密度、小型化需求。这就要求通过异构整合封装技术实现装备芯片单元和被动组件的功能扩展,基板或管基必须从芯片载体转变为集成平台。这个集成平台的推动特性需要新的封装技术来满足性能优化、产品可定制、低成本等基本要求。

2、对于多通道高压晶体管集成电路模块,每个单元高压晶体管集成电路模块均包括高压芯片单元、控制芯片单元和反相芯片单元,高压芯片单元、控制芯片单元和反相芯片单元是生产工艺、电路性能、材料特点各不相同的芯片单元,需要通过异构整合封装技术实现这些芯片单元功能扩展和一体化集成,将基板或管基从单一性的芯片载体转变为综合式的集成平台。

3、目前的陶瓷封装外壳,功率芯片的集成方式和普通芯片相同,使其功率芯片散热效果差,不能将异质电子元器件高集成度集成在一起,导致封装体积大、集成工艺不兼容、抗干扰性差、可靠性低等问题。

4、有鉴于此,特提出本发明。

技术实现思路

1、本发明所要解决的技术问题是:解决现有封装技术不能将高压芯片单元、控制芯片单元和反相芯片单元集成于一体,芯片间隔离尺寸大、功率芯片散热效果差、封装体积大、抗干扰性差、可靠性低等问题。

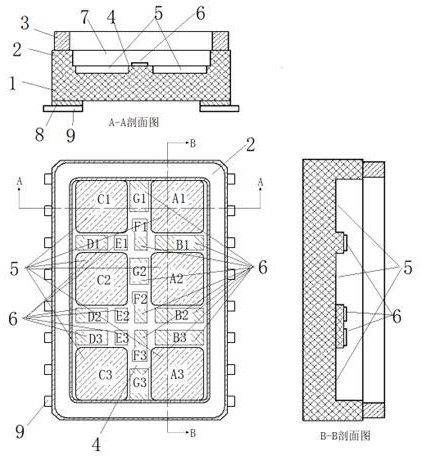

2、为此,本发明提供一种多通道高压晶体管电路模块封装方法,如图1-2所示。封装方法如下:

3、采用多层共烧陶瓷工艺制作陶瓷外壳底座,陶瓷底座顶面具有用于组装电子元器件的平底内腔及内腔周边的环形边框。

4、在陶瓷外壳底座内腔的芯片组装区域,设置多个互相隔离的高压晶体管电路通道区域,在每个高压晶体管电路通道区域内,根据高压晶体管电路模块的电路结构,将单元高压晶体管电路模块的电子元器件组装区域划分为高压晶体管芯片载体区、晶体管控制芯片载体区、信号反相芯片载体区,将高压晶体管芯片载体区通过层错结构设计为空间异构层错,空间异构层错内安装有热沉,形成多芯腔隔离结构。

5、将晶体管控制芯片载体区及信号反相芯片载体区设置在陶瓷外壳底座的底表面,以高压晶体管芯片载体区的布局为核心,晶体管控制芯片载体区及信号反相芯片载体区分布于多个压晶体管芯片载体区之间。

6、根据高压晶体管电路模块的高电压、大电流、高热量特点,将外电极结构设置为l型电极,l型电极的竖边金属层制作的陶瓷外壳底座的侧边,l型电极的底边金属层制作的陶瓷外壳底座的背面,并在l型电极的底边金属层的外表面焊接外引线金属片。

7、将高压芯片组装在低于内腔底表面的空间异构层错区内,晶体管控制芯片焊接区、信号反相芯片焊接区,引线键合区设置在内腔底表面,与空间异构层错区穿插布局,从而实现高压芯片单元、控制芯片单元和反相芯片单元的异构整合封装。

8、陶瓷外壳底座的环形边框上方为封口环,封口环上通过与盖板熔接形成空腔密封器件。

9、所述陶瓷外壳的材料为92%以上al2o3陶瓷。

10、所述封口环的材料为4j42或4j29。

11、所述热沉的材料为cmc。

12、所述外部电极金属片的材料为4j42或4j29。

13、将高压芯片组装在低于内腔底表面的空间异构层错区内,晶体管控制芯片焊接区、信号反相芯片焊接区,引线键合区设置在内腔底表面,与空间异构层错区穿插布局,从而实现高压芯片单元、控制芯片单元和反相芯片单元的异构整合封装。

14、通过多芯腔结构设计将高压晶体管与其他芯片区域做高压绝缘隔离,以达到更高耐压的绝缘要求。

15、所述一种多通道高压晶体管电路模块封装方法的封装结构,如图1-2所示。

16、包括陶瓷外壳底座1,环形边框2,封口环3,底座内腔底表面4,高压芯片组装空间异构层错区5,腔体底表面芯片组装区或键合区金属层6,底座内腔7,外电极背面金属层8,外电极背面金属片9,外电极背面起脚标志10,外电极侧面金属层11,外电极侧面起脚标志12,盖板13。

17、所述陶瓷外壳底座1顶面具有用于组装电子元器件的平底内腔及内腔周边的环形边框2,平底内腔及内腔周边的环形边框2共同围合成陶瓷外壳底座内腔7。

18、在陶瓷外壳底座内腔的芯片组装区域,设置有高压晶体管芯片载体区、晶体管控制芯片载体区、信号反相芯片载体区,以高压晶体管芯片载体区为核心,晶体管控制芯片载体区、及信号反相芯片载体区穿插布局于高压晶体管芯片载体区之间,三个区域之间为物理隔离。

19、在高压晶体管芯片载体区有低于底表面的一个以上高压芯片组装空间异构层错区5,在空间异构层错区5的平底凹坑底表面设置有金属层,在金属层上面焊接有热沉,在热沉上按电路设计要求焊接有高压晶体管芯片。

20、在陶瓷外壳底座内腔的非空间异构层错区的底表面,根据电路具体结构设置有一个以上腔体底表面芯片组装区或键合区金属层6,在腔体底表面芯片组装区上组装控制芯片单元和反相芯片单元及其他电子元器件。

21、在陶瓷外壳底座的背面,根据电路具体结构设置有一个以上外电极背面金属层8,在外电极背面金属层8上焊接有外电极背面金属片9,外电极背面金属片9的内端与外电极背面金属层8平齐,外电极背面金属片9的外端与略微超出陶瓷外壳底座的底侧面,在第一脚位置制作有外电极背面起脚标志10,外电极背面起脚标志10的金属层长度大于外电极背面金属层8的金属层长度。

22、在陶瓷外壳底座的侧面,根据电路具体结构设置有与在外电极背面金属层8一一垂直的外电极侧面金属层11,在第一脚位置制作有外电极侧面起脚标志12,外电极侧面起脚标志12的上端金属层宽度大于外电极侧面金属层11的金属层宽度。

23、根据电路具体结构,芯片与键合区之间、键合区与键合区之间通过键合丝进行键合连接。

24、在陶瓷外壳底座的环形边框上固接有封口环,在封口环上焊接有盖板13。

25、本发明的有益效果在于:

26、高压芯片单元、控制芯片单元和反相芯片单元有机地集成在同一陶瓷封装底座里面,形成一个基本完整、独立的功能模块。

27、将原先需要在pcb板级封装实现的系统功能进行了sip集成技术封装,让功能系统具有更高的性能及更高的功率密度、更多的功能以及更小的体积。

28、采用异构整合封装技术方案,空间异构层错区与底表面区域通过错层,实现水平无间距隔离,使该产品具有超小型的尺寸、高功率密度、高可靠性结构、抗外部冲击性能更强等特点。

29、本发明广泛应用于异质电子元器件的微型化、片式化、高集成度、高可靠性一体化集成技术领域中。

- 还没有人留言评论。精彩留言会获得点赞!