一种高质量结晶的3C-SiC外延片的制作方法

本技术涉及一种高质量结晶的3c-sic外延片,属于半导体制备。

背景技术:

1、碳化硅具有非常多的晶型,其中最常见的是4h、6h和3c晶型,目前商用的大部分都是4h-sic晶型。3c-sic是所有多型中唯一一个立方结构的晶型,因此有着一些潜在的应用前景。

2、3c-sic晶型除了具有和其他多型体一样的宽禁带性质之外,还具有更高的电子迁移率和更好的电子漂移速度等,这将有利于mosfet和hemt器件,另外,由于3c-sic的高电子漂移速度,还可以用作导通电极,起到降低电阻率的作用。

3、然而,传统的3c-sic异质外延是通过cvd(化学气相沉积)方法在si衬底上进行的,这会存在严重的晶格失配,比如热扩展系数8%不兼容,晶格常数20%失配等,导致3c-sic结晶质量较差,而且具有高密度的缺陷,比如层错、空洞、反相缺陷(apd)等。

4、因此研究者们现在会更倾向于选择六方晶型的衬底来进行外延生长3c-sic,比如4h-sic、6h-sic等。但是,这又会引入一种新的缺陷类型,即dpb(double positionboundary,双定位边界),dpb缺陷的成因是3c-sic具有两种不同的排列方式,即abc和acb,因此在4h-sic或6h-sic上进行外延生长时,会不可避免的生长这两种晶型,而它们的交界线便是dpb缺陷。故目前在在4h-sic和6h-sic上外延生长得到的3c-sic外延片,其具有高密度的dpb缺陷,严重阻碍3c-sic衬底的进一步应用。

技术实现思路

1、为了解决上述问题,提供了一种高质量结晶的3c-sic外延片,该3c-sic外延片的dpb小于100个/cm2,结晶质量远高于现有的3c-sic外延片,具有更多的可利用面积,提高其使用率,从而降低了使用其制作的半导体器件的成本,利于工业化推广使用。

2、本技术提供了一种高质量结晶的3c-sic外延片,所述3c-sic外延片为异质外延,且所述3c-sic外延片的dpb小于100个/cm2。

3、可选地,所述3c-sic外延片中至少40cm2的整块区域无dpb。

4、该整块区域是指由平滑的曲线或直线所限定的区域,整块区域的形状可以为三角形、矩形、圆形、椭圆形或多边形(边长不超过8)的任意一种,无dpb的整块区域面积越大,其3c-sic外延片的可利用面积越大,因此同一外延片就能切割出更多数量的合格品,故利用该合格品制作的器件数量就越多,从而能够降低器件的制作成本,利用规模化扩大生产。对比结晶质量好的区域,在边缘位置能明显看到dpb密度增多,即可认为在降低dpb密度的同时,将dpb限定在边缘位置生长,提高无dpb区域的面积。

5、可选地,所述3c-sic外延片自中心起每15mm划分为一个同心区域,自中心向边缘方向,所述同心区域内的dpb密度递增。

6、优选的,相邻同心区域dpb密度的差值为0-500个/cm2,优选为0-350个/cm2,更优选的,越靠近边缘,相邻同心区域的dpb密度差值越大。

7、将3c-sic外延片的中心至15mm处为中心圆,自中心圆的边缘向外每15mm均为一个同心环,中心圆和每个同心环均单独计算其内的dpb密度、掺杂均匀性和厚度均匀性,此处同心区域是指中心圆和多个同心环的统称。

8、可选地,所述3c-sic外延片的电阻率为0.001-100ω·cm。

9、可选地,所述3c-sic外延片的电阻率为中心向边缘降低,最高点为中心。

10、3c-sic外延片的电阻率反映了产品的导电性能,电阻率越低,则外延片的品质越好,制备的得到的器件的质量也越高。

11、可选地,所述3c-sic外延片的表面粗糙度ra小于0.2nm。

12、3c-sic外延片的表面粗糙度越小,外延片的表面质量越好,其应用价值也越高。

13、可选地,所述3c-sic外延片的直径不小于6英寸。

14、优选的,所述3c-sic外延片的直径不小于8英寸。

15、3c-sic外延片直径越大,其无dpb的区域面积越大,即有效利用面积越多,则同一外延片切割后得到的合格品数量越多,制备的器件数量也越多,进而能够提高外延片的利用率,降低器件的生产成本。

16、可选地,所述3c-sic外延片的偏角≤4°,优选的,所述3c-sic外延片的偏角≤1°。

17、可选地,所述3c-sic外延片的厚度大于0.5μm。

18、优选的,所述3c-sic外延片的厚度为0.5-30μm。所述3c-sic外延片包括缓冲层和外延层,所述缓冲层的厚度为0.1-3μm。

19、可选地,所述3c-sic外延片的厚度分布为中心向边缘逐渐变薄,最高点为中心。

20、3c-sic外延片的厚度越大,其耐压越高,该外延片的应用越广。

21、可选地,所述3c-sic外延片通过在sic衬底上进行外延生长得到。

22、可选地,所述sic衬底的表面粗糙度ra小于1nm。

23、可选地,所述sic衬底的偏角≤4°。

24、优选的,所述sic衬底的偏角≤1°。

25、可选地,所述sic衬底为半绝缘型或导电型。

26、优选的,所述导电型包括n型掺杂和p型掺杂。

27、可选地,所述3c-sic外延片的晶向为(111)方向,外延片在4h-sic或6h-sic衬底的(0001)方向进行生长,得到的外延片晶向为(111)方向,晶向发生变化。

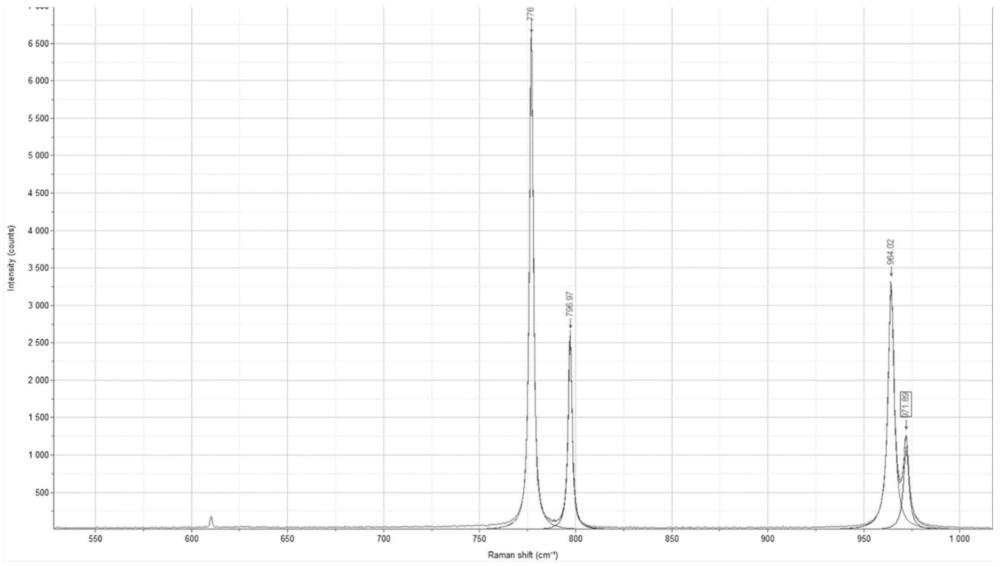

28、可选地,所述3c-sic外延片的半峰宽小于60arcsec。

29、优选的,所述3c-sic外延片的半峰宽小于40arcsec。

30、可选地,所述3c-sic外延片的微管数量、层错数量和划痕数量均为0,表面颗粒物小于100个/cm2。

31、可选地,所述3c-sic外延片的bow值大于-10μm,且小于10μm,warp值小于30μm,优选的,所述3c-sic外延片的bow值大于-2.5μm,且小于5.5μm,warp值小于15μm。

32、可选地,所述3c-sic外延片的掺杂浓度的均匀性小于2%。

33、可选地,所述掺杂浓度为n的掺杂浓度。

34、该3c-sic外延片的掺杂浓度的均匀性越小,代表外延片在各个区域的质量越均匀,越能够提高外延片的导电性,从而提高其制备的半导体器件的质量及使用寿命。

35、可选地,3c-sic外延片的厚度均匀性小于1%。

36、该3c-sic外延片的厚度均匀性越小,表示外延片的厚度偏差越小,可提高同一外延片得到的合格品数量,即提高了外延片的利用率,降低了半导体器件的生产成本。

37、可选地,自中心向边缘方向,所述同心区域的厚度均匀性和掺杂均匀性下降。

38、优选的,相邻同心区域的厚度均匀性的差值为0-0.5%,掺杂均匀性的差值为0-1.0%,且越靠近边缘,相邻同心区域的厚度均匀性和掺杂均匀性的差值越大。

39、中心圆中的dpb密度、掺杂均匀性和厚度均匀性最低,越远离中心,同心环中的dpb密度、掺杂均匀性和厚度均匀性均增加,且增加幅度也越大。

40、上述厚度均匀性和掺杂均匀性的计算公式如下:

41、

42、其中u代表均匀性,数值越小,代表均匀性越好,是测试点的平均值,σ为标准差,σ的计算公式如下:

43、

44、其中,xi为每一个点的测试数值,n是测试点数。实际测试中通常沿直径测试10-15个点。

45、上述3c-sic外延片的生产工艺包括下述步骤:

46、(1)将sic衬底固定;

47、(2)在1600-1700℃下,使用h2或者hcl对sic衬底进行刻蚀,刻蚀时间为1-30min;

48、(3)降温至1300-1550℃,通入碳源,碳源的流量为1-20ml/min,通入1-10min后停掉碳源,持续1-3min以后,通入氮气,氮气的流量为10-500ml/min,并按照碳源和硅源的碳硅比在0.5-3范围内通入碳源和硅源,控制碳源和硅源的流量,先进行3c-sic缓冲层的生长,控制长速为0.1-3μm/h,生长时间为2-10min;再进行外延层的生长,控制长速为10-60μm/h,生长时间为1-30min,得到3c-sic外延片。

49、本技术的有益效果包括但不限于:

50、1.本技术公开了一种低dpb密度缺陷的高质量结晶的3c-sic外延片,其在至少40cm2的整块区域无dpb,可利用面积大大提高,在后续器件的制作中,能够通过切割该3c-sic外延片来获得更多数量的合格品。

51、2.本技术的高质量结晶的3c-sic外延片,其尺寸至少为6寸,厚度至少为0.5μm,使得可用于制作半导体器件的有效面积更大,能够节省半导体器件的生产成本,提高3c-sic外延片的利用率。

52、3.本技术的高质量结晶的3c-sic外延片,解决了si片上异质外延3c-sic存在晶格失配严重的问题,通过在sic衬底上进行外延生长得到,又能够降低dpb缺陷密度,扩大了3c-sic外延片的应用前景。

- 还没有人留言评论。精彩留言会获得点赞!