介电弛豫量测结构和系统以及半导体器件的制作方法

本公开属于半导体芯片领域,具体涉及一种介电弛豫量测结构和系统以及半导体器件。

背景技术:

1、随着dram(dynamic random access memory,动态随机存取储存器)芯片行业的不断发展,电容的尺寸不断缩小,存储密度增加的同时,也要求dram的读写速度进一步加快,因此,介电弛豫便成了不可避免的影响因素,其中,介电弛豫时间非常短,如何有效的表征介电弛豫,实现介电材料的快速、精准筛选是亟待要解决的技术问题。

技术实现思路

1、本公开实施例提供一种介电弛豫量测结构和系统以及半导体器件,以提高介电弛豫检测的精准性。

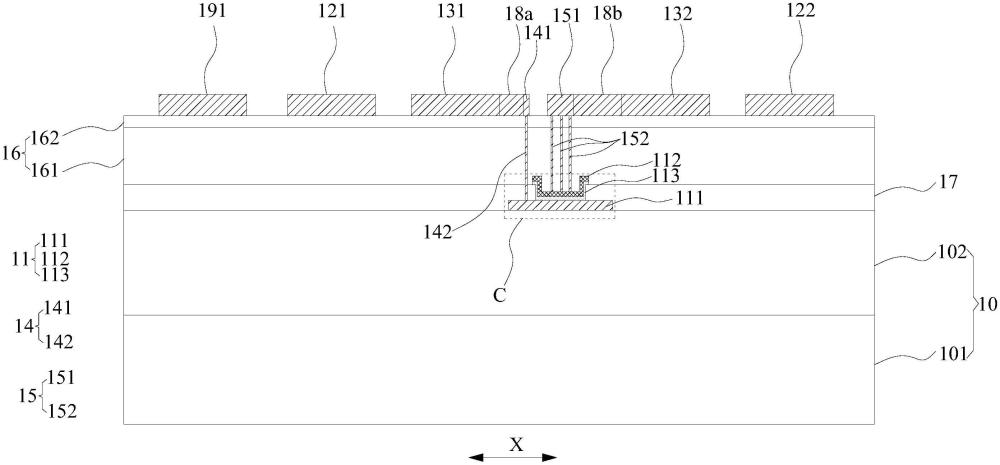

2、本公开第一方面提供了一种介电弛豫量测结构,用于测量半导体器件中电容的介电弛豫情况,所述半导体器件包括衬底,所述电容形成在所述衬底上,所述电容包括第一电极层、第二电极层及形成在所述第一电极层和所述第二电极层之间的介电材料层;其中,所述介电弛豫量测结构包括:

3、充电探针组,形成在所述衬底上,所述充电探针组包括与所述第一电极层电性连接的第一充电探针和与所述第二电极层电性连接的第二充电探针,所述第一充电探针和所述第二充电探针用于与充电装置相导通,实现为所述电容进行充电;

4、量测探针组,形成在所述衬底上,所述量测探针组包括与所述第一电极层电性连接的第一量测探针和与所述第二电极层电性连接的第二量测探针,所述第一量测探针和所述第二量测探针用于在所述充电装置停止向所述电容充电的同时与检测装置相导通,以检测所述电容的介电弛豫情况。

5、在本公开的一种示例性实施例中,所述介电弛豫量测结构还包括形成在所述衬底上的第一导电结构和第二导电结构;其中,

6、所述第一充电探针与所述第一量测探针间隔设置,所述第一导电结构的一端与所述第一量测探针和所述第一充电探针电性连接,所述第一导电结构的另一端与所述第一电极层电性连接;

7、所述第二充电探针与所述第二量测探针间隔设置,所述第二导电结构的一端与所述第二量测探针和所述第二充电探针电性连接,所述第二导电结构的另一端与所述第二电极层电性连接。

8、在本公开的一种示例性实施例中,所述半导体器件还包括形成在所述衬底上的平坦化层,所述平坦化层覆盖所述电容;其中,

9、所述第一充电探针、所述第二充电探针、所述第一量测探针和所述第二量测探针形成在所述平坦化层远离所述电容的表面;

10、所述第一导电结构贯穿所述平坦化层,所述第一导电结构的顶端与所述第一量测探针和所述第一充电探针电性相连,所述第一导电结构的底端与所述第一电极层相接触;

11、所述第二导电结构贯穿所述平坦化层,所述第二导电结构的顶端与所述第二量测探针和所述第二充电探针电性相连,所述第二导电结构的底端与所述第二电极层相接触。

12、在本公开的一种示例性实施例中,所述第一电极层与所述衬底相平行,所述第一电极层包括第一主区域和环绕所述第一主区域的第一边缘区域,所述第二电极层形成在所述第一电极层远离所述衬底的一侧,且所述第二电极层和所述介电材料层在所述衬底上的正投影位于所述第一主区域在所述衬底上的正投影内;其中,

13、所述第一导电结构环绕所述第二导电结构设置,所述第一导电结构在所述衬底上的正投影与所述第一边缘区域在所述衬底上的正投影存在交叠,且所述第一导电结构的底端与所述第一边缘区域相接触,所述第二导电结构在所述衬底上的正投影位于所述第二电极层在所述衬底上的正投影内。

14、在本公开的一种示例性实施例中,所述第一导电结构包括第一转接部和第一过孔部,所述第一转接部位于所述平坦化层远离所述电容的表面,并与所述第一量测探针和所述第一充电探针电性连接,所述第一过孔部在所述衬底上的正投影位于所述第一转接部在所述衬底上的正投影内,所述第一过孔部贯穿所述平坦化层,且所述第一过孔部的顶端和所述第一转接部相接触,所述第一过孔部的底端和所述第一边缘区域相接触;

15、所述第二导电结构包括第二转接部和第二过孔部,所述第二转接部位于所述平坦化层远离所述电容的表面,并与所述第二量测探针和所述第二充电探针电性连接,所述第二过孔部在所述衬底上的正投影位于所述第二转接部在所述衬底上的正投影内,所述第二过孔部贯穿所述平坦化层,且所述第二过孔部的顶端和所述第二转接部相接触,所述第二过孔部的底端和所述第二电极层相接触;

16、其中,所述第一转接部环绕所述第二转接部设置,所述第一过孔部设置多个,并沿周向间隔排布,以环绕所述第二过孔部设置。

17、在本公开的一种示例性实施例中,所述第一充电探针、所述第二充电探针、所述第一量测探针和所述第二量测探针在所述衬底上的正投影与所述电容在所述衬底上的正投影不存在交叠;

18、所述介电弛豫量测结构还包括第一引线和第二引线,所述第一引线和所述第二引线形成在所述平坦化层远离所述电容的表面,所述第一引线和所述第二引线包括主干段和支干段,所述主干段和所述支干段具有第一端和第二端,所述支干段的第一端位于所述主干段的第一端和第二端之间,并与所述主干段连接;

19、在所述第一引线中:主干段的第一端与所述第一转接部相接触,主干段的第二端与所述第一充电探针和所述第一量测探针中的一者相接触,支干段的第二端与所述第一充电探针和所述第一量测探针中的另一者相接触;

20、在所述第二引线中:主干段的第一端与所述第二转接部相接触,主干段的第二端与所述第二充电探针和所述第二量测探针中的一者相接触,支干段的第二端与所述第二充电探针和所述第二量测探针中的另一者相接触;

21、其中,所述第一转接部具有供所述第二引线的主干段穿过的避让开口,所述第二引线的主干段与所述第一转接部在所述避让开口处具有间隙。

22、在本公开的一种示例性实施例中,所述第一引线中主干段的第二端与所述第一量测探针相接触,且所述第一充电探针位于所述第一量测探针远离所述第一转接部的一侧;

23、所述第二引线中主干段的第二端与所述第二量测探针相接触,且所述第二充电探针位于所述第二量测探针远离所述第二转接部的一侧。

24、在本公开的一种示例性实施例中,所述介电材料层在所述衬底上的正投影与所述第二电极层在所述衬底上的正投影完全重合,且所述第二电极层和所述介电材料层包括第二主区域和环绕所述第二主区域的第二边缘区域;

25、所述第二导电结构在所述衬底上的正投影位于所述第二主区域在所述衬底上的正投影内。

26、在本公开的一种示例性实施例中,所述半导体器件还包括形成在所述衬底上的层间介质层,位于所述平坦化层靠近所述衬底的一侧;

27、所述层间介质层覆盖所述第一主区域的边缘位置以及覆盖所述第一边缘区域,且所述层间介质层具有贯通孔,所述贯通孔露出所述第一主区域的中间位置;

28、所述第二边缘区域搭接在所述层间介质层远离所述第一电极层的表面,所述第二主区域形成在所述贯通孔内;

29、其中,所述第一导电结构在贯穿所述平坦化层并与所述第一电极层相接触时,还贯穿所述层间介质层以与所述第一边缘区域相接触。

30、在本公开的一种示例性实施例中,所述介电弛豫量测结构还包括:

31、接地探针,形成在所述平坦化层远离所述衬底的一侧,用于接地;

32、接地屏蔽部,所述接地屏蔽部贯穿所述平坦化层,所述接地屏蔽部的顶端与所述接地探针电性连接,所述接地屏蔽部的底端向所述衬底的方向延伸,所述接地屏蔽部在所述衬底上正投影位于所述电容在所述衬底上的正投影的至少相对两侧。

33、在本公开的一种示例性实施例中,所述接地屏蔽部靠近所述衬底的表面低于所述电容靠近所述衬底的表面或与所述电容靠近所述衬底的表面相平齐。

34、在本公开的一种示例性实施例中,所述第一充电探针、所述第一量测探针、所述第二充电探针、所述第二量测探针在所述衬底上的正投影与所述电容在所述衬底上的正投影不存在交叠;

35、所述接地屏蔽部与所述电容之间的水平间距小于所述第一充电探针、所述第一量测探针、所述第二充电探针、所述第二量测探针与所述电容之间的水平间距。

36、在本公开的一种示例性实施例中,所述第一充电探针和所述第一量测探针组成第一探针组,所述第二充电探针和所述第二量测探针组成第二探针组,所述第一探针组和所述第二探针组在第一方向上排布;

37、所述第一导电结构和所述第二导电结构位于所述第一探针组和所述第二探针组之间,所述第一导电结构朝向所述第一探针组的表面通过第一引线与所述第一充电探针和所述第一量测探针连接,所述第二导电结构朝向所述第二探针组的表面通过第二引线与所述第二充电探针和所述第二量测探针连接;

38、所述第一引线和所述第二引线形成在所述平坦化层远离所述电容的表面,所述接地屏蔽部远离所述衬底的表面与所述第一引线和所述第二引线靠近所述平坦化层的表面相平齐,或高于所述第一引线和所述第二引线靠近所述平坦化层的表面;

39、所述接地屏蔽部设置两个,并在第二方向上排布,所述电容位于两个所述接地屏蔽部之间,且所述第二方向与所述第一方向相交;

40、其中,两个所述接地屏蔽部靠近所述第一探针组的一侧间隔排布以形成有供所述第一引线穿过的第一避让缺口,所述第一引线在所述第一避让缺口处具有间隙,两个所述接地屏蔽部靠近所述第二探针组的一侧间隔排布以形成有供所述第二引线穿过的第二避让缺口,所述第二引线在所述第二避让缺口处具有间隙;各所述接地屏蔽部分别通过一条接地引线与所述接地探针电性连接。

41、在本公开的一种示例性实施例中,所述接地引线形成在所述平坦化层远离所述衬底的一侧;和/或

42、所述第一探针组和所述第二探针组中一者远离所述第一导电结构和所述第二导电结构的一侧形成所述接地探针。

43、在本公开的一种示例性实施例中,所述接地屏蔽部为在所述第一方向上延伸的长条形结构;或

44、所述接地屏蔽部包括在所述第一方向上延伸的主屏蔽部和位于所述主屏蔽部的两延伸端处的副屏蔽部,所述副屏蔽部在第二方向上延伸。

45、在本公开的一种示例性实施例中,所述第一量测探针相比于所述第一充电探针靠近所述第一导电结构设置;

46、所述第二量测探针相比于所述第二充电探针靠近所述第二导电结构设置。

47、本公开第二方面提供了一种半导体器件,其包括:

48、衬底;

49、电容,形成在所述衬底上,所述电容包括第一电极层、第二电极层及形成在所述第一电极层和所述第二电极层之间的介电材料层;以及

50、介电弛豫量测结构,形成在所述衬底上,并包括充电探针组和量测探针组,所述充电探针组包括与所述第一电极层电性连接的第一充电探针和与所述第二电极层电性连接的第二充电探针,所述第一充电探针和所述第二充电探针用于与充电装置相导通,实现为所述电容进行充电;所述量测探针组包括与所述第一电极层电性连接的第一量测探针和与所述第二电极层电性连接的第二量测探针,所述第一量测探针和所述第二量测探针用于在所述充电装置停止向所述电容充电的同时与检测装置相导通,以测量所述电容的介电弛豫情况。

51、在本公开的一种示例性实施例中,所述第一电极层与所述衬底相平行,且所述第二电极层形成在所述第一电极层远离所述衬底的一侧。

52、本公开第三方面提供了一种介电弛豫量测系统,用于测量半导体器件中电容的介电弛豫情况,所述半导体器件包括衬底,所述电容形成在所述衬底上,所述电容包括第一电极层、第二电极层及形成在所述第一电极层和所述第二电极层之间的介电材料层;其中,所述介电弛豫量测系统包括:

53、控制装置;

54、介电弛豫量测结构,形成在所述衬底上,并包括充电探针组和量测探针组,所述充电探针组包括与所述第一电极层电性连接的第一充电探针和与所述第二电极层电性连接的第二充电探针,所述量测探针组包括与所述第一电极层电性连接的第一量测探针和与所述第二电极层电性连接的第二量测探针;

55、充电装置,与所述控制装置电性连接,所述充电装置能够在所述控制装置的控制下与所述第一充电探针和所述第二充电探针相导通,以为所述电容进行充电,所述充电装置还能够在所述控制装置的作用下与所述第一充电探针和所述第二充电探针相断开,以停止向所述电容进行充电;

56、检测装置,与所述控制装置电性连接,所述检测装置能够在所述充电装置停止向所述电容充电的同时在所述控制装置的控制下与所述第一量测探针和所述第二量测探针相导通,以检测所述电容的介电弛豫情况。

57、在本公开的一种示例性实施例中,所述检测装置包括电流表,所述电流表能够在所述充电装置停止向电容充电的同时在所述控制装置的控制下串接在所述第一量测探针和所述第二量测探针之间;或

58、所述检测装置包括电压表和短接线,所述电压表能够在所述充电装置停止向电容充电的同时在所述控制装置的作用下串接在所述第一量测探针和所述第二量测探针之间,所述短接线能够在所述充电装置停止向电容充电的同时在所述控制装置的控制下短接在所述第一充电探针和所述第二充电探针之间。

59、本公开实施例提供的技术方案至少具有以下优点:通过设置两组探针组,一组为充电探针组,用于与充电装置相导通,为电容进行充电,另一组为量测探针组,用于在停止向电容充电后与检测装置相导通,以检测电容的介电弛豫情况,相比于利用一组共用探针组既进行充电又进行介电弛豫检测的方案,本方案在检测电容的介电弛豫情况的过程中,无需进行将充电装置与共用探针组先拆除,然后再将检测装置与共用探针连接的这一切换步骤,本方案可在充电装置停止向电容充电后的同时,直接使检测装置与量测探针组相导通,以检测电容的介电弛豫情况,这样可节省切换所耗费的时间,降低介电弛豫检测过程中的测量误差,以更加精准的表征介电弛豫情况,从而实现介电材料的快速、精准筛选。

- 还没有人留言评论。精彩留言会获得点赞!