一种IGBT半导体结构及其制造方法与流程

本发明涉及功率半导体,涉及一种igbt半导体结构及其制造方法。

背景技术:

1、具有沟槽栅极结构的半导体功率器件,特别是沟槽igbt(绝缘栅双极晶体管)。这些器件具有栅极接触,该栅极接触通过适当的介电材料(例如二氧化硅)与晶体管结构的其余部分电隔离,该介电材料用于控制器件并将其从阻断状态切换到导通状态,反之亦然。现代igbt设计可以包括许多不同的设计元件以实现器件的期望。例如,没有形成mos沟道的单元(非有源单元)、具有浮动p-阱层的区域或不连接到栅极电势的附加沟槽(虚设沟槽)。

2、目前,如图1a、图1b和图1c,已经公开了用于虚设沟槽、栅极沟槽和p-阱的不同布局,具体的,图1a的半导体结构包括虚拟沟槽901、栅极沟槽906,浮动p-阱907,非活动台面904,活动台面905,源极902,触点903;图1b的半导体结构包括虚拟沟槽911、栅极沟槽916,浮动p-阱917,非活动台面914,活动台面915,源极912,触点913;图1c半导体结构包括虚拟沟槽921、栅极沟槽926,浮动p-阱927,非活动台面924,活动台面925,源极922,触点923;上述结构设计的目的是提供对栅极沟槽底部电场的保护,并改善开关行为。然而,现有的技术问题是在同一步骤中扩散增强和浮动p-阱,没有办法独立控制增强区和浮动p-阱的扩散深度,限制了设计的选择。再有如果存在具有“空穴路径”的虚设沟槽结构,目前的技术是不允许独立的调节栅极沟槽结构和虚设沟槽结构中的“载流子限制”,即载流子流入空穴路径与有源接触的自由度。

3、本发明急需提供一种igbt半导体结构及其制造方法。

技术实现思路

1、本发明的目的是提供一种igbt半导体结构及其制造方法,通过一igbt半导体结构结构的设计,以解决现有的在同一步骤中扩散增强和浮动p-阱,没有办法独立控制增强区和浮动p-阱的扩散深度,限制了器件设计的选择性的技术问题。

2、本发明提供的一种igbt半导体结构,包括

3、半导体衬底,所述半导体衬底上设有第一导电类型的漂移区;

4、所述漂移区内设有第二导电类型的主体区;

5、所述主体区(102)嵌入有第一导电类型的源极区;

6、位于所述主体区(2)下方的第一导电类型的增强区;

7、设置在所述半导体衬底背面上的第二导电类型的阳极层;

8、所述阳极层上设有第一导电类型的缓冲层;

9、栅极沟槽结构,包括栅极沟槽,栅极沟槽包围主体区、源极区和增强区,栅极沟槽内设有介电层,通过介电层与半导体电隔离,源极区上设有用于器件连接的源极触点;

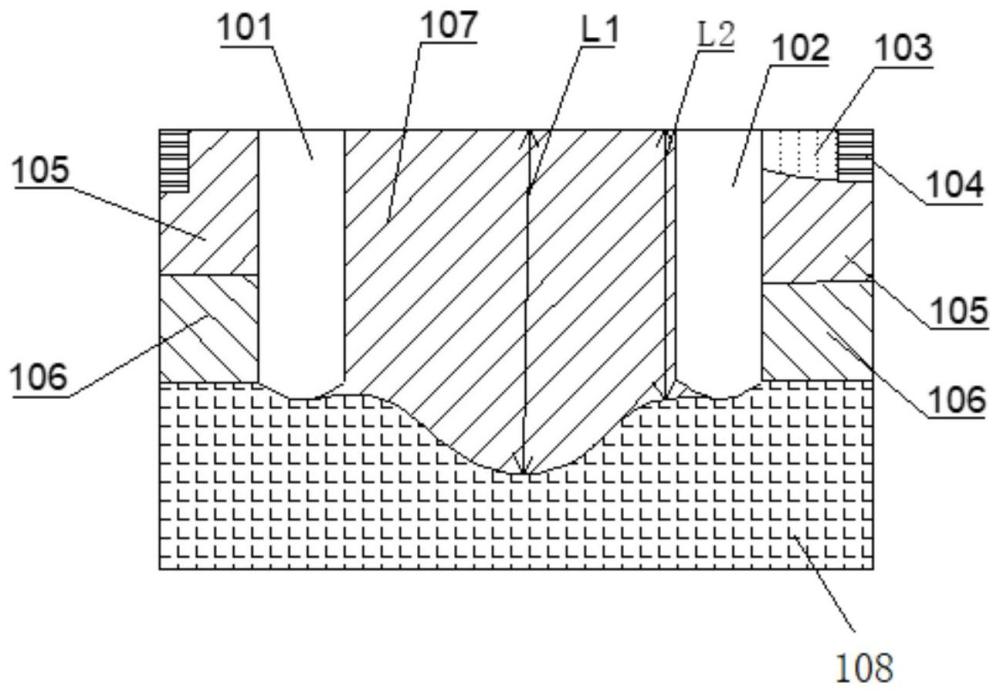

10、第二导电类型的高掺杂区,是电浮动的,即为浮动p-阱,所述浮动p-阱存在于栅极沟槽结构的任一侧,所述浮动p-阱与所述漂移区形成结线;所述结线延伸的最大深度为l1,所述结线延伸的最大深度大于栅极沟槽的深度,所述结线延伸的最大深度位置远离栅极沟槽;在沟槽附近,所述结线在深度l2处显现,深度l2与栅极沟槽的底部齐平;l1和l2之间的连接线遵循平滑的s曲线;

11、设置在所述源极区内的源极触点,所述源极触点将所述半导体衬底连接到器件的顶侧上的发射极电势;

12、虚设沟槽结构,包括虚设沟槽,虚设沟槽包围主体区和增强区,虚设沟槽内设有介电层,通过虚设沟槽内的介电层与半导体电隔离,并连接到器件的发射极触点;

13、虚设沟槽结构中的所述主体区内设有虚设触点,所述虚设触点将半导体材料连接到器件顶侧上的发射极电势;

14、上述结构,在纵向方向上排列成条纹,其中所述虚设沟槽结构和栅极沟槽结构可以在水平方向上以任何组合排列,在任意两个所述虚设沟槽结构和栅极沟槽结构之间存在浮动p-阱。

15、优选地,所述的栅极沟槽结构中的源极区在纵向上任一比例中断。

16、优选地,栅极沟槽结构中的所述增强区的深度与虚设沟槽结构中的增强区的深度不同;

17、或者,在栅极沟槽结构中或虚设沟槽结构中,不设置增强区;

18、或者,栅极沟槽结构中的所述增强区的深度与虚设沟槽结构中的增强区在纵向上的深度可以调整。

19、优选地,栅极沟槽结构中的所述主体区与虚设沟槽结构中的所述主体区的深度不同。

20、优选地,虚设沟槽结构中的源极触点在纵向上任一比例中断。

21、优选地,虚设沟槽的宽度大于栅极沟槽的宽度;或者虚设沟槽的深度大于栅极沟槽的深度。

22、优选地,使用硅的局部氧化(locos)工艺,对半导体衬底的虚设沟槽结构区域进行处理,形成凹陷,使得虚设沟槽结构在半导体器件内比栅极沟槽结构更深。

23、优选地,使用硅的局部氧化(locos)工艺,对半导体衬底的栅极沟槽结构区域进行处理,形成凹陷,使得栅极沟槽结构区域在半导体器件内比虚设沟槽结构区域更深。

24、优选地,所述虚设沟槽不连接到发射极,保持浮动。

25、优选地,虚设沟槽不连接到发射极,而是连接到栅极,并且具有栅极沟槽结构不具有源极区的特征。

26、优选地,虚设沟槽结构在发射电极和半导体材料之间形成肖特基接触(schottky接触),在虚设沟槽结构中的所述主体区不嵌入电极。

27、本发明还提供了一种igbt半导体结构,包括:

28、半导体衬底,所述半导体衬底上设有第一导电类型的漂移区;

29、所述漂移区内设有第二导电类型的主体区;

30、所述主体区内嵌设有源极区;

31、在所述主体区下方设有第一导电类型的增强区;

32、在所述半导体衬底背面设有第二导电类型的阳极层;

33、在所述阳极层上设置缓冲层;

34、栅极沟槽结构,包括栅极沟槽,栅极沟槽包围主体区、源极区和增强区,栅极沟槽内设有介电层,通过介电层与半导体电隔离,源极区上设有用于器件连接的源极触点;

35、第二导电类型的高掺杂区,是电浮动的,即为浮动p-阱,所述浮动p-阱存在于栅极沟槽结构的任一侧,所述浮动p-阱与所述漂移区形成结线;所述结线延伸的最大深度为l1,所述结线延伸的最大深度大于沟槽的深度,所述结线延伸的最大深度位置远离沟槽;在沟槽附近,所述结线在深度l2处显现,该深度与栅极沟槽的底部齐平;l1和l2之间的连接线遵循平滑的s曲线;

36、设置在所述源极区内的源极触点,所述源极触点将所述半导体材料连接到器件的顶侧上的发射极电势;

37、由单个宽而深的虚设沟槽组成的虚设沟槽结构,虚设沟槽由薄介电膜覆盖并填充有导电材料,该导电材料连接到器件的发射极触点;

38、在虚设沟槽结构底部的接触区,其中所述薄介电膜被局部去除,并且接触区形成在所述半导体器件中;

39、第二导电类型的ct植入区,直接位于虚设沟槽底部的接触区域下方;

40、上述结构,在纵向方向上排列成条纹,其中所述虚设沟槽和栅极沟槽结构可以在水平方向上以任何组合排列,在任意两个所述虚设沟槽和栅极沟槽结构之间存在p-阱区。

41、优选地,所述栅极沟槽结构中的源极区在纵向上任一比例中断。

42、优选地,所述虚设沟槽的槽底部的接触区在纵向方向上以任意比例中断。

43、优选地,使用硅的局部氧化(locos)工艺,在半导体衬底表面虚设沟槽区域形成凹陷,使得虚设沟槽在半导体器件内比栅极沟槽结构更深;

44、或者,不设置虚设沟槽,在凹陷区域中形成接触区。

45、优选地,使用硅的局部氧化(locos)工艺,在半导体衬底的栅极沟槽结构区形成凹陷,使得栅极沟槽结构区在半导体器件内比虚设沟槽更深。

46、优选地,虚设沟槽底部的接触区在金属和半导体之间形成肖特基接触。

47、本发明还提供了一种igbt半导体结构,包括

48、半导体衬底,所述半导体衬底上设有第一导电类型的漂移区;

49、所述漂移区内设有第二导电类型的主体区;

50、所述主体区内嵌设有第一导电类型的源极区;

51、所述主体区下方设有第一导电类型的增强区;

52、半导体衬底背面设有第二导电类型的阳极层;

53、所述阳极层上设有缓冲层;

54、辅助栅极沟槽,其在垂直(y)方向上在器件的顶面上以条纹图案延伸,并且通过电介质层与半导体电隔离,并且连接到器件的栅极接触;

55、栅极沟槽结构,包括栅极沟槽,栅极沟槽包围主体区、源极区和增强区,栅极沟槽内设有介电层,通过介电层与半导体层电隔离,在纵向(y)上垂直于辅助栅极沟槽延伸,并且连接到辅助栅极沟槽;

56、多个栅极沟槽结构,其布置在两个相邻的辅助沟槽之间;

57、第二导电类型的高掺杂区,是电浮动的,即为浮动p-阱,所述浮动p-阱存在于栅极沟槽结构的任一侧,所述浮动p-阱与所述漂移区形成结线;所述结线延伸的最大深度为l1,所述结线延伸的最大深度大于沟槽的深度,所述结线延伸的最大深度位置远离沟槽;在沟槽附近,所述结线在深度l2处显现,该深度与栅极沟槽的底部齐平;l1和l2之间的连接线遵循平滑的s曲线;

58、栅极沟槽结构内的源极触点,该源极触点将半导体材料连接到器件前侧的发射极电势;

59、虚设沟槽结构,包括虚设沟槽,虚设沟槽内设有介电层,虚设沟槽包围所述主体区和增强区,虚设沟槽的介电层连接到器件的发射极接触,并且在器件的垂直(x)方向上延伸;

60、虚设沟槽结构内的接触区,其将半导体材料连接到器件顶侧上的发射极电势;

61、在垂直(x)方向上布置的多个虚设沟槽结构和栅极沟槽结构,其中虚设沟槽结构和栅极沟槽结构可以以任何组合交替,并且其中在相邻虚设沟槽结构和栅极沟槽结构之间存在浮动p-阱。

62、优选地,在一些栅极沟槽结构中可以省略源极区,或者在单个栅极沟槽结构内源极区不连续的情况下,或者其任何组合。

63、优选地,当在垂直方向上观察时,栅极沟槽结构之间没有浮动p-阱,而是沿着辅助沟槽的长度延伸间隔的栅极沟槽。

64、优选地,虚设沟槽结构内的接触区在垂直方向上以任意比率中断。

65、优选地,栅极沟槽结构中的增强层与虚设沟槽结构的增强区具有不同的深度;或者在栅极沟槽结构或虚设沟槽结构中省略增强层。

66、优选地,使用硅的局部氧化(locos)工艺,使得半导体衬底的表面栅极沟槽结构的区域中形成凹陷。

67、优选地,使用硅的局部氧化(locos)工艺,使得半导体衬底的表面虚设沟槽结构的区域中形成凹陷。

68、优选地,虚设沟槽中的接触区在发射极电极和半导体材料之间形成肖特基接触。

69、本发明还提供了一种基于如上述中任一项所述的igbt半导体结构的制造方法,包括如下步骤:

70、使用掺杂有第一导电类型材料的半导体衬底;

71、使用掩膜覆盖在所述半导体衬底上,在半导体衬底正面的p-阱区注入第二导电类型掺杂剂,形成浮动p-阱;

72、经第一高温处理,使得所述浮动p-阱向所述半导体衬底内扩散,第一高温处理时间持续t1min;

73、在所述半导体衬底正面采用掩膜工艺,对所述半导体衬底进行极性刻蚀,获得栅极沟槽和虚设沟槽,其中,所述栅极沟槽和浮动p-阱区边缘之间的间隙为δpa,虚设沟槽边缘与浮动p-阱区边缘之间的间隙δpd;

74、在半导体衬底正面注入第一导电类型材料,形成第一导电类型的增强层;

75、经第二高温处理,第二高温处理时间持续t2min,驱动浮动p-阱区和所述的增强层继续渗透,使得浮动p-阱区底部形成s形;

76、从所述半导体衬底的正面注入第二导电类型材料,形成体层;

77、经第三高温处理,第三高温处理时间持续t3min,驱动浮动p-阱、所述增强层和所述主体区继续渗透,获得最终期望的图形;

78、使用掩膜工艺,在所述半导体衬底正面形成源极区和源极触点,在所述半导体衬底正面沉积金属层;

79、对所述半导体衬底的背面进行打磨,打磨后,在所述半导体衬底背面依次设置阳极层和缓冲层;

80、采用退火工艺处理阳极层和缓冲层,激活阳极层和缓冲层;

81、在缓冲层上沉积金属层。

82、优选地,δpd和t1的选择方式使得在虚设沟槽蚀刻之后;p-阱注入的掺杂剂保留在虚设沟槽之间并部分补偿掺杂剂。

83、优选地,δpa和t1的选择方式使得在栅极沟槽蚀刻之后;p-阱注入的掺杂剂保留在栅极沟槽之间并部分补偿掺杂剂。

84、优选地,增强层在纵向上的位置是变化。

85、本发明提供的igbt半导体结构及其制造方法与现有技术相比具有以下进步:

86、1、本发明提供的igbt半导体结构,栅极沟槽和虚设沟槽之间的距离可以用于调节空穴路径的电阻,可以减少虚设沟槽结构中的载流子限制,从而调节载流子限制的效率,同时在栅极沟槽结构中保持相同,有利于提高设备的静态和动态性能。

87、2、本发明提供的igbt半导体结构,浮动p-阱区底部形成s形,有助于在静态和动态阻塞情况下形成平滑的电场,提高了栅极沟槽底部的保护,而且,减少局部长峰值和不必要的载流子生成(动态雪崩)。栅极沟槽底部是电场最容易导致局部击穿、雪崩载流子产生和热载流子注入栅极氧化物的地方。

88、3、本发明的虚设沟槽由单个大虚设沟槽代替,虚设沟槽在底部连接到半导体,与漂移区导电类型相反的高掺杂区直接放置在接触下方,以避免集电极发射极短路,提高了空穴提取效率。减少栅极沟槽结构经理的场峰值问题,避免将常移动到不太敏感的发射极虚设偏置的虚设沟槽。

89、4、本实施例的辅助栅极沟槽的设计,可以实现相邻的两个栅极沟槽结构之间的距离变得很小。

- 还没有人留言评论。精彩留言会获得点赞!