一种基于多晶硅膜的N沟道JFET管及制备方法与流程

本发明涉及高性能硅基半导体结型场效应器件,具体是一种基于多晶硅膜的n沟道jfet管及制备方法。

背景技术:

1、结型场效应管jfet是一种利用pn结电场效应来控制电流的一种半导体器件,它是通过改变垂直于导电沟道的电场强度e,来控制沟道的导电能力,从而调制通过沟道的电流id。由于场效应晶体管的工作电流仅由多数载流子输运,故又称之为单极型场效应晶体管。从参与导电的多数载流子来划分,分为电子作为载流子的n沟道器件和空穴作为载流子的p沟道器件。结型场效应管是一种电压控制器件,通过输入电压的改变控制输出电流,而双极型晶体管为电流控制器件。结型场效应管的直流输入阻抗很高,一般可达109-1015ω。结型场效应管噪声低,因而结型场效应管特别适合于要求高灵敏度、低噪声的场合,如检测各种微弱信号的仪器、仪表、医疗器械等。结型场效应管热稳定性好。因为结型场效应管是一种多子器件,且可有正的、负的及正负交叉的零温度系数工作点。只要在设计电路时使器件工作在零温度系数工作点附近,即可消除温度的影响。结型场效应管抗辐射能力强,这也因为结型场效应管是多子器件。这一特点使其持别适用于航天器等承受强烈核辐射、宇宙射线辐射的装备中。

2、现有的jfet管结构与制备方法,所制备的器件主要缺点是:1)器件栅区pn结电流漏电ig大;2)器件栅区电极电阻rg高;3)器件源端寄生串联电阻rs大。所制备的器件噪声大,器件特征频率ft、最高振荡fmax低,高频特性差,器件单位跨导小。

技术实现思路

1、对于现有存在的一些问题,本发明的目的在于提供一种基于多晶硅膜的n沟道jfet管及制备方法,以解决上述背景技术中提出的问题。

2、为实现上述目的,本发明提供如下技术方案:

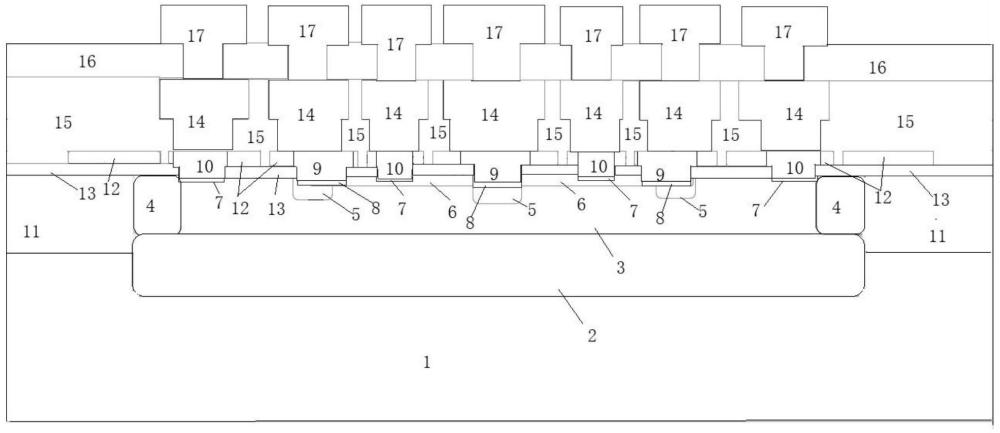

3、第一方面,本发明公开了一种基于多晶硅膜的n沟道jfet管,包括原始硅片,所述原始硅片晶圆片表面上掺杂形成p型隐埋层;

4、原始硅片上外延生长掺磷的n型外延层;

5、n型外延层上掺杂形成p-型区;

6、p-型区内光刻掺杂形成n-型源漏区和n型沟道区;

7、n型外延层上光刻掺杂形成p型连接区;

8、p-型区内光刻刻蚀设有n型源漏区,p-型区内光刻掺杂设有多晶硅栅隐埋区;

9、n型外延层上表面依次沉积设置氧硅介质膜和多晶硅膜;

10、氧硅介质膜为热氧化与沉积的复合介质膜;

11、n型多晶硅杂质区光刻掺杂设有n型多晶硅膜,p型多晶硅杂质光刻掺杂设有p型多晶硅膜;

12、多晶硅膜上表面设有沉积氧化硅介质膜;

13、沉积氧化硅介质膜溅射沉积设有第一金属铝;

14、沉积氧化硅介质膜上表面沉积设有氧化硅-氮硅复合介质区;

15、氧化硅-氮硅复合介质区溅射沉积设有第二金属铝。

16、作为本发明进一步的方案:所述p型连接区设置在p-型区的外围。

17、作为本发明进一步的方案:所述n型多晶硅膜设置在n型源漏区上方。

18、作为本发明进一步的方案:所述p型多晶硅膜设置在多晶硅栅隐埋区上方。

19、第二方面,本发明还公开了一种基于多晶硅膜的n沟道jfet管的制备方法,其方法步骤如下:

20、s1、准备原始硅片衬底晶圆片;原始硅片的型号为n<100>,ρ:5~7ωcm,硅衬底片厚度:675±25μm;

21、s2、原始硅片表面高温生长热二氧化硅膜;

22、s3、在原始硅片的晶圆片表面选择性形成一定深度和杂质浓度分布的p型隐埋层;

23、s4、外延生长n型外延层;在具有p型杂质区的原始硅片硅晶圆表面,外延生长一定厚度和电阻率的掺磷n型外延层;

24、s5、在硅晶圆n型外延层表面高温热生长二氧化硅层;950度干氧氧化,在n型外延层表面生长一定厚度二氧化硅层;

25、s6、在硅晶圆的n型外延层形成p-型区;

26、s7、湿法腐蚀二氧化硅晶圆表面高温热生长二氧化硅层;湿法腐蚀二氧化硅,1020度干氧氧化,在硅晶圆表面生长一定厚度二氧化硅介质膜;

27、s8、n-型源漏区的形成;用n型管源/漏区光掩膜,通过光刻与磷杂质的注入,在p-型区内,形成n-型源漏区;

28、s9、n型沟道区的形成;用n型沟道区光掩膜,通过光刻与磷杂质的注入,在p-型区内,形成n型沟道区;

29、s10、隐埋层p型连接区的形成;用p型连接区光掩膜,通过光刻与硼杂质的注入,形成隐埋层p型连接区;

30、s11、lpcvd沉积氮硅膜;

31、s12、n-型源漏区、n型沟道区及隐埋层p型连接区的高温退火;在1130度氮气保护下,进行n-型源漏区、n型沟道区及隐埋层p型连接区高温退火与再分布;

32、s13、氮硅层的预去除;用氮硅预蚀光掩膜,去表面的氮硅膜层;

33、s14、多晶硅下的隐埋区形成;用n型源/漏隐埋接触区光掩膜,通过光刻与刻蚀,形成n型源漏区;用多晶硅栅隐埋区光掩膜,通过光刻与杂质注入,形成多晶硅栅隐埋区;

34、s15、lpcvd沉积氧硅介质膜和多晶硅膜;用lpcvd沉积氧硅介质膜和多晶硅膜,氧硅介质膜为热氧化与沉积的复合介质膜;

35、s16、多晶硅膜的掺杂、多晶硅膜的图形化、源的n杂质注入及氧硅介质膜的沉积与致密化;

36、s17、jfet管夹断电压vp测试与调节;基于jfet管vp测试,提取器件夹断电压vp初始数值,应用高温下栅掺杂区杂质前向扩散推进效应,调节器件n型有效沟道深度2a,逐次降低vp,达到vp设计值;

37、s18、多晶硅接触孔;用多晶硅接触孔区光掩膜,通过光刻、刻蚀与湿法腐蚀,去除多晶硅接触孔区介质层,形成与第一金属铝互连接触窗口;

38、s19、沉积第一金属铝、第一金属铝的图形化;溅射沉积第一金属铝;用第一金属铝光掩膜,通过光刻与金属刻蚀,实现第一金属铝图形化;

39、s20、沉积金属层间绝缘介质层、互连通孔;pecvd沉积金属层间二氧化硅/氮化硅/二氧化硅绝缘介质层,形成沉积的氧化硅-氮硅复合介质区;用金属层间互连通孔光掩膜,通过光刻与复合介质的等离子刻蚀,形成第一金属铝与第二金属铝间的互连孔;

40、s21、沉积第二金属铝以及第二金属铝的图形化。

41、作为本发明再进一步的方案:所述步骤s3具体为透过氧化的热二氧化硅膜,利用p型隐埋层光掩膜,通过光刻与杂质的注入,在n型衬底硅表面,选择性植入一层硼杂质;用lpcvd沉积二氧化硅膜,硅晶圆在1150度氮气保护下,进行退火与硼杂质的扩散和再分布,在硅晶圆表面形成一定深度和杂质分布的p型隐埋层。

42、作为本发明再进一步的方案:所述步骤s6具体为在硅晶圆n型外延层表面,用p型区光掩膜,通过光刻与杂质的注入,形成p-型区;在n型外延层表面,选择性植入一层硼杂质;用lpcvd沉积二氧化硅,硅晶圆在1180度氮气保护下,进行退火与硼杂质的扩散和再分布,实现硼杂质的扩散与推进并穿透n型外延层。

43、作为本发明再进一步的方案:所述步骤s16具体为n型多晶硅杂质区光刻、杂质注入,形成n型多晶硅膜;p型多晶硅杂质区光刻、杂质注入,p型多晶硅膜;用多晶硅光掩膜,通过光刻与多晶硅刻蚀,实现多晶硅膜的图形化;源端n+连接区光刻与杂质注入;lpcvd沉积二氧化硅膜并高温下致密形成沉积氧化硅介质膜。

44、作为本发明再进一步的方案:所述步骤s21具体为溅射沉积第二金属铝;用第二金属铝光掩膜,通过光刻与金属刻蚀,实现第二金属铝图形化;对其进行合金化。

45、与现有技术相比,本发明的有益效果是:

46、本发明的器件的设计参数gm,对器件的相关噪声有不同的影响,提高跨导gm,可降低等效输入噪声电压en,跨导gm增大,又将使噪声优值f0增大。

47、本发明设计高频、低噪声、高输入阻抗和高单位跨导的jfet管,就是在满足器件单位跨导及基础工艺能力的条件下,通过器件有源区版图布局、器件掺杂纵向结深与杂质浓度纵向分布、器件源/漏和器件的栅金属电极的布局布线,有效降低jeft管栅电极漏电流ig,减小栅极电极电阻rg和器件源端串联电阻rs。

- 还没有人留言评论。精彩留言会获得点赞!