一种半导体器件外延结构的制备方法与流程

本发明属于微电子和第三代半导体材料,具体涉及一种半导体器件外延结构的制备方法。

背景技术:

1、随着高压开关和高速射频电路的发展,氮化镓高电子迁移率晶体管(gan hemt)成为该领域研究的重点。常规的gan hemt器件均为耗尽型,阈值电压<0v,需要使用负的开启电压。在功率、射频及微波芯片设计时,其负栅压的电源设计增加了设计成本;增强型hemt的阈值电压为正值,实际应用中只需要一个正的偏压即可使其工作或夹断。这样可以消除负偏压的电路设计,使电路简单化,减少电路设计的复杂性和制备的成本,对大规模功率微波射频电路应用来说,其意义十分重大。对于功率开关电路,增强型hemt器件保证在驱动电路失效时,hemt器件处于关断状态,从而对功率开关系统提供了失效保护。

2、有几种方法可以实现常关型hemt器件,如氟离子注入、具有mis栅极、p-gan栅极等的部分或全部凹陷的algan等。在上述方法中,p-gan栅极已被证明是最可靠的,目前正被使用在商业产品中,在较薄的(例如)algan势垒层顶部形成p-gan层(p-algan或p-inaln)可以有效地耗尽二维电子气(2deg),从而实现常关操作。这种二维电子气(2deg)耗尽效应在很大程度上取决于algan势垒层的厚度,al%组分以及algan势垒层顶部的p-gan中mg的掺杂浓度,并且随着algan势垒层的厚度(>20nm)和/或al%(>20%)的增加而逐渐减弱。因此,要获得理想的阈值电压vth(例如1~2v),必须同时调整algan势垒层的厚度和al%。

3、因此,现有方案中,较为普遍的一种实现p-gan基增强型hemt的方法是将势垒层设计为12nm-15nm,阈值电压约为2v左右,但是,由于势垒层的厚度比较薄会导致p-gan中的mg原子容易扩散到沟道层中,进而使器件的导通电阻增大,影响hemt器件的工作效率。而在p-gan基增强型hemt器件中,为了有效的减少p-gan中的mg原子扩散到沟道层的数量,通常采用的手段是将势垒层变厚,但是,势垒层变厚,会导致p-gan层的跨导栅控能力变弱从而使阈值电压的值向负向移动,从而使阈值电压变小,甚至变负,从而失去其常关型特性。因此需要在两者之间进行平衡。

4、现有技术的主要问题:由于要得到vth偏正(1~2v的开关电压),需降低势垒层的厚度同时降低势垒层中的al%组分或者是提高p-gan层中mg的掺杂浓度;但调整后带来了三个问题:1.势垒层厚度变薄,使在势垒层上面的p-gan层在生长过程中mg很容易扩散到2deg沟道层中,从而降低2deg的浓度,增加ron,降低器件性能;2.势垒层变薄和al%组分降低,使2deg的浓度降低,增加导通电阻影响gan的器件性能,同时由于厚度变薄,该材料层的晶体质量变差,也使势垒层的可靠性变差;3.提高p-gan层中的mg浓度,会导致mg更加容易扩散到沟道层,从而影响器件性能。

5、目前业内,针对势垒层做了大量的工作,比如采用合金势垒层(一层或多层aln层)或者不同组分浓度的alingan(al和in的组分变化)交替形成的超晶格势垒层,其两种思路的核心思想即提高势垒层的厚度,但是势垒层的厚度增加会导致p-gan层的跨导栅控能力变弱,使得在沟道层的电子不易被控制,从而会形成漏电,也就是说由于势垒层变厚之后,p-gan层所生成的能带中的价带很难把沟道层中的gan的价带拉高,使其高于费米能级。如果低于费米能级,那么该器件性能就变成了常开型,也就是阈值电压变负。

6、以上背景技术内容的公开仅用于辅助理解本发明的发明构思及技术方案,其并不必然属于本专利申请的现有技术,在没有明确的证据表明上述内容在本专利申请的申请日以前已经公开的情况下,上述背景技术不应当用于评价本技术的新颖性和创造性。

技术实现思路

1、鉴于此,为了克服现有技术的缺陷,本发明的目的是提供一种半导体器件外延结构的制备方法,得到的半导体器件的外延结构,能够在保证vth变化不大或者有所提升的前提下,可以采用更厚的势垒层和更高的al%组分,且能更加有效的抑制上层mg的扩散和更好发挥器件性能。

2、为了达到上述目的,本发明采用以下的技术方案:

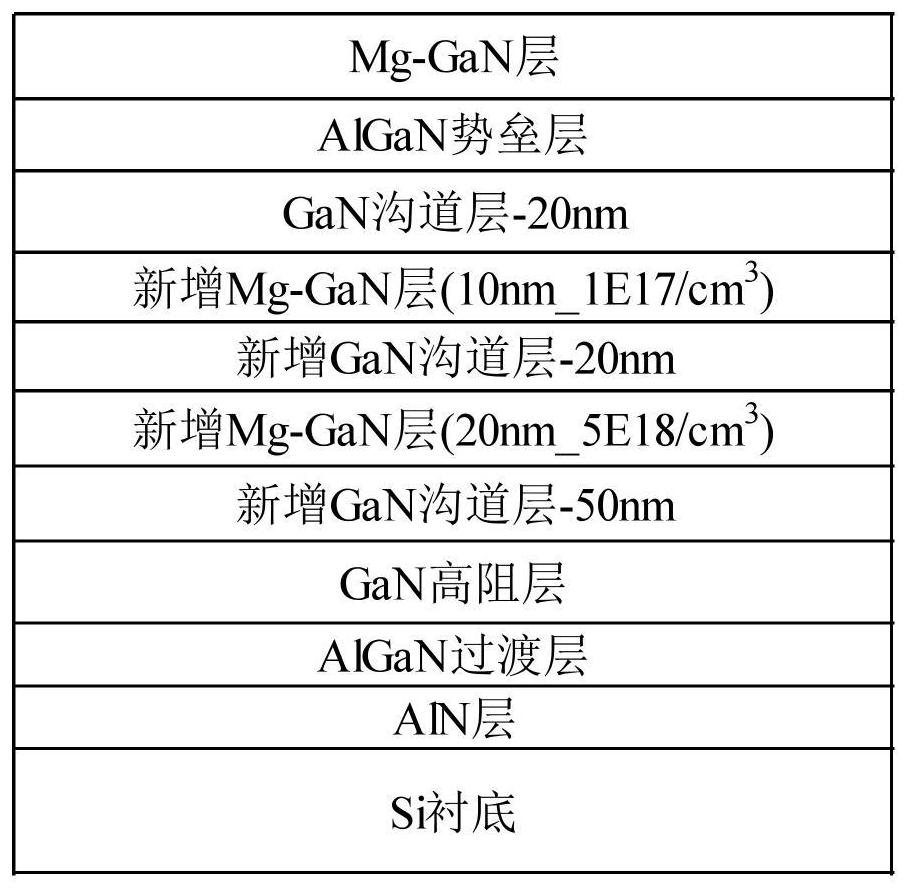

3、一种半导体器件的外延结构,依次包括衬底、aln层、过渡层、高阻层、沟道层、势垒层和p-gan层,所述沟道层和高阻层之间设置有一层或多层的掺杂有mg的新增p-gan层,所述沟道层和高阻层之间设置有一层或多层的新增沟道层,最靠近所述沟道层的一层为所述新增p-gan层,最靠近所述高阻层的一层为所述新增沟道层。

4、本发明的半导体器件的外延结构,重新设计了势垒层下方的结构,在gan沟道层下方增加一层或者多层掺杂低浓度mg的p-gan层,在保证vth变化不大或者有所提升的前提下,可以采用更厚的势垒层(>20nm)和更高的al%组分(>20%),更加有效的抑制上层p-gan层中mg的扩散和更好发挥器件性能。

5、根据本发明的一些优选实施方面,所述沟道层的厚度大于20nm。

6、根据本发明的一些优选实施方面,所述沟道层和高阻层之间设置有一层掺杂有mg的新增p-gan层,所述掺杂有mg的新增p-gan层与所述高阻层之间设置有一层新增沟道层。

7、根据本发明的一些优选实施方面,所述沟道层和高阻层之间设置有多层掺杂有mg的新增p-gan层和多层新增沟道层;所述掺杂有mg的新增p-gan层和所述新增沟道层交替设置;且最靠近所述沟道层的一侧为掺杂有mg的新增p-gan层,最靠近所述高阻层的一侧为新增沟道层。

8、根据本发明的一些优选实施方面,靠近所述高阻层的新增p-gan层中mg的掺杂浓度大于靠近所述沟道层的新增p-gan层中mg的掺杂浓度。其主要目的:一、避免靠近势垒层的过高浓度的mg形成并有可能扩散到沟道层里面去,从而影响器件性能;二、通过多层不同浓度的p-gan层可以更加有效的吸引住或者耗尽沟道层中的电子,同时也能在外延层中形成内建的pn结,消耗材料中的电荷使外延层材料的耐电压性能更好。

9、根据本发明的一些优选实施方面,所述新增p-gan层中mg的掺杂浓度为1e17/cm3~5e18/cm3。

10、根据本发明的一些优选实施方面,靠近所述高阻层的新增p-gan层的厚度大于靠近所述沟道层的新增p-gan层的厚度。

11、根据本发明的一些优选实施方面,所述新增p-gan层的厚度为10nm~20nm。

12、根据本发明的一些优选实施方面,靠近gan高阻层的新增gan沟道层的厚度大于靠近gan沟道层的新增gan沟道层的厚度。

13、本发明还提供了一种如上所述的半导体器件的外延结构的制备方法,包括如下步骤:

14、在衬底上依次生长aln层、过渡层、高阻层、一层或多层的掺杂有mg的新增p-gan层、一层或多层的新增沟道层、沟道层、势垒层和p-gan层;所述新增p-gan层和新增沟道层交替设置。

15、根据本发明的一些优选实施方面,生长所述新增p-gan层和新增沟道层时的制备参数为:n2氛围,温度为900~1000℃,压力为100~200mbar,v/iii比为5000~10000。制备得到的gan表面平整度为0.5nm以下的粗糙度。而现有的制备方法很难达到0.5nm以下的表面粗糙度;表面粗糙度越小,说明外延层表面越平整,也从侧面说明外延层质量变好,同时对势垒层下面的2deg的迁移率提高有很大的帮助。

16、本发明还提供了一种包括如上所述的外延结构的半导体器件。

17、本发明的主要原理:在hemt器件结构中,二维电子气的产生是由于势垒层algan和gan沟道层之间产生压电极化和algan层本身的自发极化,从而在gan沟道层上表面几纳米的区域形成浓度很高的电子气(2deg),因此正常情况下该器件是处于导通状态。通过在势垒层的上方生长一层p-gan层,形成pn结电场从而把沟道层中的电子吸引住,从而形成器件的关断。这个pn结电场中间隔着势垒层,也就导致了该势垒层不能太厚同时al%组分的浓度不能太高,势垒层太厚或al%组分太高都会导致器件无法关断。本发明主要是在势垒层的下方采用新的结构,在gan沟道层下方增加一层或者多层低浓度的p-gan(空穴),来帮助势垒层上方的p-gan进行对2deg电子的吸引,同时也能提高外延层的击穿电压,其原理为:本征gan沟道层主要为n型材料,通过在gan沟道层中引入低浓度的mg-gan层,可以在其沟道层内部形成pn结,降低沟道层中的电子浓度,从而提高器件耐压。

18、由于采用了以上的技术方案,相较于现有技术,本发明的有益之处在于:本发明的半导体器件外延结构的制备方法,制备得到的gan的粗糙度0.5nm以下。同时在gan沟道层下方增加多层掺杂低浓度mg的p-gan层,能够在保证vth变化不大或者有所提升的前提下,可以采用更厚的势垒层和更高的al%组分,更加有效的抑制上层p-gan层中mg的扩散和更好发挥器件性能,同时由于势垒层的厚度加厚,其晶体质量变好,也能进一步提升器件的栅稳定型,器件更加可靠。

- 还没有人留言评论。精彩留言会获得点赞!