半导体结构及其制备方法、电子设备与流程

本技术涉及集成电路,特别是涉及一种半导体结构及其制备方法、电子设备。

背景技术:

1、随着集成电路技术的发展,器件的关键尺寸日益缩小,单个芯片所包含的器件种类及数量随之增加,使得工艺生产中的任何微小差异都可能对器件性能造成影响。

2、为了尽可能降低产品的成本,人们希望在有限的衬底上做出尽可能多的器件单元。自从摩尔定律问世以来,业界提出了各种半导体结构设计和工艺优化,以满足人们对当前产品的需求。

技术实现思路

1、基于此,本技术提供一种半导体结构及其制备方法、电子设备。

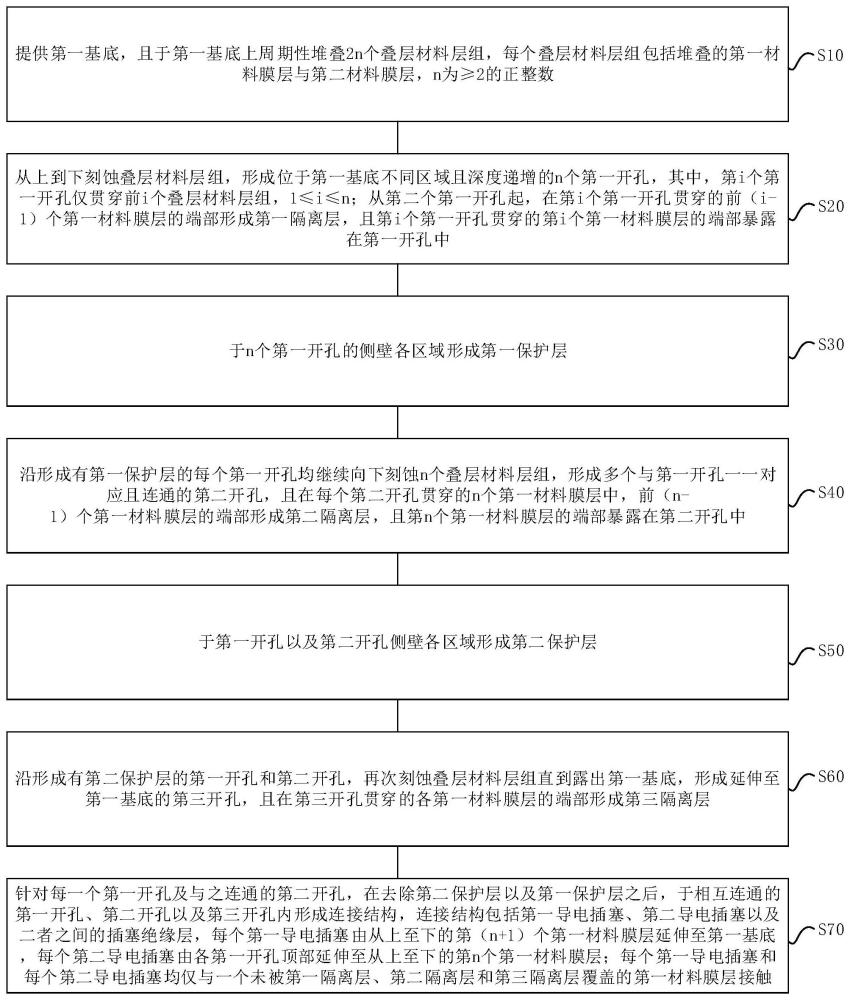

2、一种半导体结构的制备方法,包括:

3、提供第一基底,于所述第一基底上周期性堆叠2n个叠层材料层组,每个所述叠层材料层组包括第一材料膜层与第二材料膜层,n为≥2的正整数;

4、刻蚀所述叠层材料层组形成深度递增的n个第一开孔,其中,第i个所述第一开孔仅贯穿在靠近所述第一基底的方向上的第1~第i个所述叠层材料层组,1≤i≤n;每个第一开孔内露出的各第一材料膜层中,最后一个第一材料膜层暴露出,其他第一材料膜层的端部设置有第一隔离层;

5、从每个所述第一开孔内继续向下刻蚀n个叠层材料层组,形成与所述第一开孔连通的第二开孔,每个所述第二开孔内露出的各第一材料膜层中,最后一个第一材料膜层暴露出,其他第一材料膜层的端部设置有第二隔离层;

6、在每个所述第二开孔内继续向下刻蚀叠层材料层组直到露出所述第一基底,形成与所述第二开孔连通的第三开孔,且在所述第三开孔内露出的各第一材料膜层的端部设置有第三隔离层;

7、于所述第二开孔内形成延伸到所述第一基底的第一导电插塞,于所述第一开孔内形成与所述第一导电插塞相绝缘的第二导电插塞。

8、一些实施例中,2n个所述第一材料膜层为2n个牺牲材料层,2n个所述第二材料膜层为2n个绝缘材料层,形成所述第一导电插塞和所述第二导电插塞之后,还包括:

9、将所述2n个叠层材料层组中的所述2n个所述第一材料膜层替换为2n个导电层,在靠近所述第一基底的方向,所述2n个导电层依次包含第1~第n个导电层,以及第n+1~第2n个导电层;

10、所述第1~第n个导电层与各所述第二导电插塞一一对应连接;

11、所述第n+1~第2n个导电层与各所述第一导电插塞一一对应连接。

12、一些实施例中,2n个所述第一材料膜层为2n个导电层,2n个所述第二材料膜层为2n个绝缘材料层;

13、于所述第一基底上周期性堆叠2n个叠层材料层组,包括:于所述第一基底上交替形成2n个所述导电层和2n个所述绝缘层材料层;

14、在靠近所述第一基底的方向,所述2n个导电层依次包含第1~第n个导电层,以及第n+1~第2n个导电层;

15、所述第1~第n个导电层与各所述第二导电插塞一一对应连接;

16、所述第n+1~第2n个导电层与各所述第一导电插塞一一对应连接。

17、一些实施例中,形成所述第一隔离层,包括:

18、在靠近所述第一基底的方向各向异性刻蚀所述叠层材料层组,形成深度递增的n个第一初始孔,其中,第i个所述第一初始孔仅贯穿在靠近所述第一基底的方向上第1~第(i-1)个所述叠层材料层组;

19、通过湿法刻蚀回刻所述第一初始孔暴露出的各第一材料膜层,形成第一横向凹槽;

20、仅在各所述第一横向凹槽中填充所述第一隔离层。

21、一些实施例中,形成所述n个第一开孔,包括:

22、沿各所述第一初始孔继续向下刻蚀一个所述叠层材料层组,形成n个所述第一开孔。

23、一些实施例中,所述仅在各所述第一横向凹槽中填充所述第一隔离层,包括:

24、于所述第一初始孔以及所述第一横向凹槽内沉积第一隔离材料层;

25、通过各向异性刻蚀去除所述第一横向凹槽之外的第一隔离材料层,保留所述第一横向凹槽内的第一隔离材料层作为所述第一隔离层。

26、一些实施例中,形成所述第二开孔和所述第二隔离层,包括:

27、形成所述第一开孔后,形成位于所述第一开孔侧壁的第一保护层,所述第一保护层遮盖所述第一开孔暴露出的所述第一材料膜层和所述第一隔离层;

28、在所述第一开孔内继续向下刻蚀数量为(n-1)个所述叠层材料层组形成第二初始孔;

29、对所述第二初始孔暴露出的各第一材料膜层进行横向刻蚀,形成第二横向凹槽;

30、于所述第二横向凹槽内形成第二隔离层;

31、沿所述第二初始孔继续向下刻蚀一个所述叠层材料层组,形成所述第二开孔。

32、一些实施例中,形成所述第三开孔和所述第三隔离层,包括:

33、在所述第二开孔的侧壁形成第二保护层,所述第二保护层遮盖所述第二开孔暴露出的所述第一材料膜层和所述第二隔离层;

34、在所述第二开孔内向下刻蚀剩余的所述叠层材料层组,形成延伸至所述第一基底的第三开孔;

35、沿所述第三开孔对所述第三开孔暴露出的各第一材料膜层进行横向刻蚀,形成第三横向凹槽;

36、于所述第三开孔内的各所述第三横向凹槽内形成第三隔离层。

37、一些实施例中,于所述第二开孔内形成延伸到所述第一基底的第一导电插塞,于所述第一开孔内形成与所述第一导电插塞相绝缘的第二导电插塞,包括:

38、于每个所述第一开孔、对应的所述第二开孔以及所述第三开孔内沉积第一插塞材料层;

39、在靠近所述第一基底的方向上,将每个所述第一插塞材料层回刻至第(n+1)个所述第一材料膜层形成所述第一导电插塞;

40、于所述第一导电插塞的顶部形成插塞绝缘材料层;

41、在靠近所述第一基底的方向上,将所述插塞绝缘材料层回刻至第(n+1)个所述第二材料膜层,形成插塞绝缘层;

42、于每个所述第一开孔、第二开孔内以及所述插塞绝缘材料层上沉积第二插塞材料层,所述第二插塞材料层填充满所述第一开孔。

43、本技术实施例提供一种半导体结构,包括:

44、第一基底;

45、堆叠结构,包括堆叠于所述第一基底上的2n个周期性分布的叠层组,每个所述叠层组包括导电层与绝缘隔离层,n为≥2的正整数;

46、所述2n个周期性分布的叠层组包括:在靠近所述第一基底的方向依次分布的第1~第n个导电层以及第n+1~第2n个导电层;

47、位于所述第一基底上不同区域的n个通孔,n个所述通孔分别贯穿所述堆叠结构并露出所述第一基底;每个所述通孔内包含从靠近所述第一基底的方向依次分布的第一导电插塞、插塞绝缘层、第二导电插塞;

48、每个所述第一导电插塞由第(n+1)个所述导电层延伸至第2n个所述导电层且仅与其中一个所述导电层电连接;

49、每个所述第二导电插塞由第1个所述导电层延伸至第n个所述导电层且仅与其中一个导电层电连接。

50、一些实施例中,还包括:

51、隔离层,位于所述通孔的侧壁,所述隔离层用于将不与所述第一导电插塞和第二导电插塞连接的各导电层与第一导电插塞和第二导电插塞隔离。

52、一些实施例中,所述堆叠结构的导电层包括沿第一方向延伸的位线。

53、一些实施例中,所述半导体结构还包括第二基底;

54、所述第一基底上设置有第一外围电路,所述通孔露出所述第一基底上的所述第一外围电路;

55、所述第二基底上设置有第二外围电路;

56、所述第一导电插塞与所述第二基底上的所述第二外围电路连接;

57、所述第二导电插塞与所述第一基底上的所述第一外围电路连接。

58、一些实施例中,所述导电层与位线连接,所述第一外围电路和所述第二外围电路包括感应放大电路。

59、本技术实施例还提供一种半导体结构,包括:

60、多条信号线,周期性堆叠于第一基底上相互绝缘且沿第一方向延伸,沿靠近第一基底的方向,所述多条信号线依次包含第1~第n条信号线以及第n+1至m条信号线;

61、第一外围电路,位于所述第一基底中且位于所述多条信号线的下方;

62、第二外围电路,位于第二基底上且位于所述多条信号线的上方;

63、所述多条信号线中,所述第1~第n条信号线与所述第二外围电路连接,所述第n+1至m条信号线与所述第一外围电路连接;

64、其中,所述m、n均为正整数。

65、一些实施例中,包括:

66、多个通孔,在所述第一方向上间隔分布,每个通孔均贯穿所述多条信号线且露出所述第一外围电路;

67、每个所述通孔内先后填充有相互绝缘的第一导电插塞和第二导电插塞,各所述第一导电插塞从所述第一外围电路延伸到第m+1条信号线,第二导电插塞从所述第二外围电路延伸到所述第一导电插塞的上方,且通过第一导电插塞的顶部的插塞绝缘层与所述第一导电插塞绝缘;

68、每个所述第二导电插塞仅与所述第1~第n条信号线中的其中一条信号线电连接;每个所述第一导电插塞仅与所述第n+1至m条信号线中的一条信号线电连接。

69、一些实施例中,所述半导体结构包含存储结构,所述信号线包括位线或字线。

70、一些实施例中,每一个所述通孔中仅有两条信号线与第一导电插塞和第二导电插塞电连接,每个通孔中与第一导电插塞和第二导电插塞电连接的两个连接区域间隔n条信号线。

71、一些实施例中,周期性堆叠的所述多条信号线为2n条。

72、一些实施例中,所述第一基底和所述第二基底均为硅基底,所述第二基底与所述第一基底键合连接。

73、本技术一些实施例还提供一种电子设备,包括:任意一个实施例所述的半导体结构。

74、上述半导体结构及其制备方法、电子设备可以有效简化半导体结构及其制备方法。

- 还没有人留言评论。精彩留言会获得点赞!