混合键合方法、三维集成电路及电子设备

本技术涉及半导体,尤其是涉及一种混合键合方法、三维集成电路及电子设备。

背景技术:

1、

2、为满足高性能芯片的应用需求,先进封装互连技术不断地向高密度、高可靠方向发展。目前,主流应用的先进封装互连技术为sn基钎料软钎焊工艺,其具有连接温度低(250~300℃)、成本低等优势。然而,软钎焊工艺也面临着诸多局限性,例如回流过程中易产生外溢效应,无法实现窄节距互连;其接头载流能力弱,易出现电迁移失效;界面反应易生成空洞和脆性相,导致机械可靠性降低等。

3、cu-cu混合键合(hybrid bonding,hb)由于无sn元素的使用避免了上述问题的出现。cu-cu混合键合技术是将cu/sio2打磨出极其光滑的表面,当表面足够光滑时,不同界面之间将会产生范德华力,稍微施加压力或高温就可以实现永久键合,cu-cu、sio2-sio2、cu-sio2界面之间都可以同时键合,故称为混合键合。cu-cu混合键合技术具有实现窄节距互连、优异的导电、导热性能,良好的抗电迁移能力和热机械可靠性,使得cu-cu混合键合技术可满足高密度、高可靠性互连,未来最有可能获得大规模应用。然而,cu-cu混合键合也面临诸多挑战,如铜的熔点高(1083℃)、自扩散速率低,难以实现低温键合,通常cu-cu混合键合的温度需要在350℃~400℃甚至更高,以增加二者的机械连接强度,减小二者的连接图案的键合界面的接触电阻。由于集成电路中的电子器件在高温环境下的稳定性较差,退火处理过程中的高温可能导致cu的氧化及电子器件的性能退化。因此,如何实现cu-cu低温键合对于实现高密度、高可靠的先进封装技术意义重大。

技术实现思路

1、本技术的一些实施例提供了一种混合键合方法、三维集成电路及电子设备,旨在实现三维集成电路在混合键合过程中的cu-cu低温键合。

2、为达到上述目的,本技术的实施例采用如下技术方案:

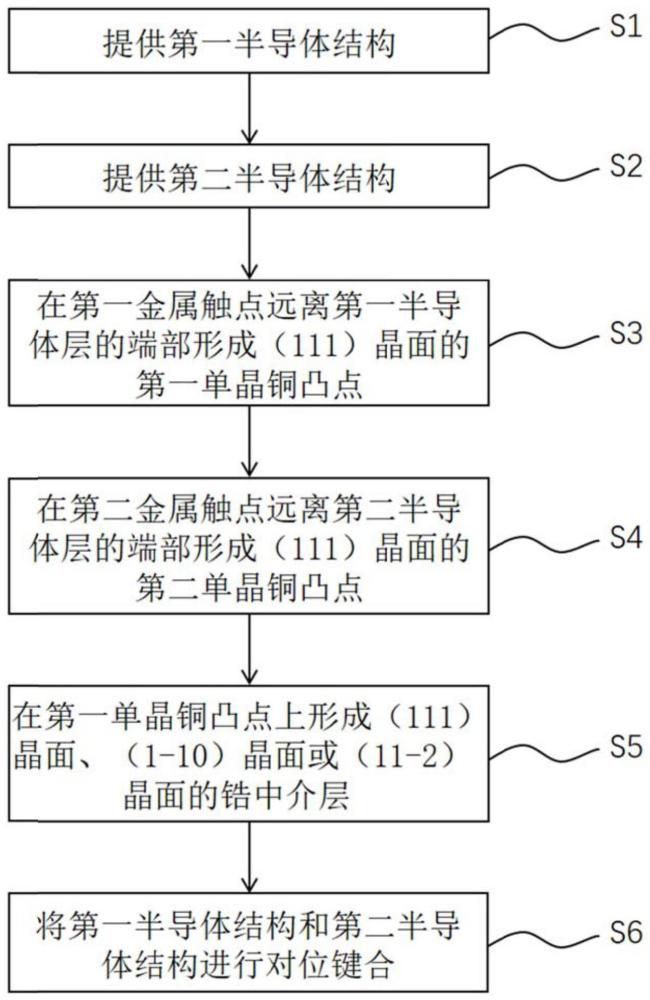

3、第一方面,本技术提供一种混合键合方法,应用于三维集成电路的制造,所述方法包括:

4、提供第一半导体结构,所述第一半导体结构包括第一半导体层、设置在所述第一半导体层上的多个第一金属触点以及填充在多个所述第一金属触点之间的第一介电质层;

5、提供第二半导体结构,所述第二半导体结构包括第二半导体层、设置在所述第二半导体层上的多个第二金属触点以及填充在多个所述第二金属触点之间的第二介电质层;

6、在所述第一金属触点远离所述第一半导体层的端部形成(111)晶面的第一单晶铜凸点;

7、在所述第二金属触点远离所述第二半导体层的端部形成(111)晶面的第二单晶铜凸点;

8、在所述第一单晶铜凸点上形成(111)晶面、(1-10)晶面或(11-2)晶面的锆中介层;以及

9、所述锆中介层形成后,将所述第一半导体结构和所述第二半导体结构进行对位键合,使得所述第一单晶铜凸点和所述第二单晶铜凸点一一对中接触键合,且所述第一介电质层和所述第二介电质层接触键合。

10、在一些实施例中,所述在所述第一金属触点远离所述第一半导体层的端部形成(111)晶面的第一单晶铜凸点,包括:

11、形成覆盖所述第一介电质层的第一掩膜层,所述第一掩膜层位于所述第一介电质层远离所述第一半导体层的一侧,所述第一掩膜层具有第一开口,所述第一开口暴露所述第一金属触点的设定区域;以及

12、在所述第一开口内形成(111)晶面的第一单晶铜凸点。

13、在一些实施例中,所述在所述第一单晶铜凸点上形成(111)晶面、(1-10)晶面或(11-2)晶面的锆中介层,包括:

14、将含有所述第一掩膜层和所述第一单晶铜凸点的所述第一半导体结构和单晶锆靶材放入磁控溅射生长腔内并抽真空到超高真空;

15、在超高真空下对所述第一半导体结构进行烘烤;

16、烘烤之后在所述第一单晶铜凸点远离所述第一半导体层的一端形成111)晶面、(1-10)晶面或(11-2)晶面的锆中介层;以及

17、去除所述第一掩膜层。

18、在一些实施例中,所述磁控溅射生长腔的参数设置包括:

19、溅射真空度为10-4~10-2pa;

20、溅射功率为400~600w;

21、溅射时间为5~10min;以及

22、烘烤温度为200~300℃。

23、在一些实施例中,所述在所述第二金属触点远离所述第二半导体层的端部形成(111)晶面的第二单晶铜凸点,包括:

24、形成覆盖所述第二介电质层的第二掩膜层,所述第二掩膜层位于所述第二介电质层远离所述第二半导体层的一侧,所述第二掩膜层具有第二开口,所述第二开口暴露所述第二金属触点的设定区域;

25、在所述第一开口内形成(111)晶面的第一单晶铜凸点;以及

26、去除所述第二掩膜层。

27、在一些实施例中,所述锆中介层的厚度为1~3nm。

28、在一些实施例中,所述第一单晶铜凸点和所述第二单晶铜凸点的厚度不小于5nm。

29、在一些实施例中,所述第一半导体结构和所述第二半导体结构的键合参数包括:

30、键合真空度为10-6~10-5pa;

31、键合温度为200~300℃;

32、压强为25~40mpa;以及

33、保温保压时长为0.5~1h。

34、在一些实施例中,所述第一半导体层为晶圆或芯片,所述第二半导体层为晶圆或芯片。

35、在一些实施例中,所述第一介电质层的材料为氧化硅或氮化硅,所述第二介电质层为氧化硅或氮化硅。

36、在一些实施例中,所述第一金属触点和所述第二金属触点均为铜触点。

37、第二方面,本技术提供一种三维集成电路,采用上述的混合键合方法制得,所述三维集成电路包括:

38、第一半导体结构,所述第一半导体结构包括第一半导体层、设置在所述第一半导体层上的多个第一金属触点以及填充在多个所述第一金属触点之间的第一介电质层,每个所述第一金属触点远离所述第一半导体层的端部设置有(111)晶面的第一单晶铜凸点;

39、第二半导体结构,所述第二半导体结构包括第二半导体层、设置在所述第二半导体层上的多个第二金属触点以及填充在多个所述第二金属触点之间的第二介电质层,每个所述第二金属触点远离所述第二半导体层的端部设置有(111)晶面的第二单晶铜凸点;以及锆中介层;

40、其中,所述第一半导体结构和所述第二半导体结构对位贴合,使得所述第一单晶铜凸点与所述第二单晶铜凸点一一对应键合,且所述第一介电质层与所述第二介电质层键合;所述锆中介层扩散融合在每组一一对应的第一单晶铜凸点和第二单晶铜凸点的键合接触面。

41、第三方面,本技术提供一种电子设备,包括:

42、电路板;以及

43、上述的三维集成电路,所述三维集成电路与所述电路板电连接。

44、综上所述,本技术至少具有以下有益效果:本技术的上述实施例所提供的混合键合方法,通过在第一单晶铜凸点和第二单晶铜凸点之间引入(111)晶面、(1-10)晶面或(11-2)晶面的锆中介层,利用锆中介层能够增大第一单晶铜凸点和第二单晶铜凸点的相互扩散程度,降低第一单晶铜凸点和第二单晶铜凸点键合所需的温度,实现低温cu-cu混合键合,尽可能避免了高温所导致的cu的氧化及电子器件性能退化的问题,提高了集成电路键合的质量和产品可靠性。另外,同时降低了cu-cu混合键合时键合温度的控制难度,降低了工艺成本。

- 还没有人留言评论。精彩留言会获得点赞!