具有双层场板的双沟槽SGT器件及制备方法

本发明涉及功率半导体技术,具体涉及一种具有双层场板的双沟槽sgt器件及制备方法。

背景技术:

1、功率半导体器件在电子产业中具有广泛的应用前景,随着新能源、光伏等领域的发展,市场需求将持续增长。其中各种垂直型双扩散金属氧化物半导体器件(vdmos)由于将电流路径为纵向,使得电流密度得到极大的提升,当前受到广泛应用。在此基础上,屏蔽栅vdmos(shield gate trench vdmos,简称sgt)应运而生。sgt在槽内引入分立的屏蔽栅电极,根据屏蔽栅极和控制栅极的相对位置差异可分为上下结构和左有结构两种。sgt结构中屏蔽栅极可以作为场板来降低体内漂移区电场,从而提高漂移区浓度以降低其电阻,在相同击穿电压下获得比普通沟槽m0sfet更低的导通电阻,从而突破传统硅器件比导通电阻和击穿电压之间的极限。

2、sgt能在相同的击穿电压下获得更低的比导、更小的寄生电容,是一种较为理想的功率器件,适用于开关和线性应用,是当前中低压mos领域主流的电子电力器件。屏蔽栅极结构降低了控制栅极和漏极的正对面积,有效减小了密勒电容,提高了器件栅极抗漏极电压震荡的能力,也降低了器件的开关损耗,提高了sgt的开关速度。当器件处于反向阻断状态时,屏蔽栅接源极电位,屏蔽栅通过电荷耦合效应对漂移区进行辅助耗尽,优化了器件内纵向电场分布,降低了纵向电场的峰值,提高了器件的击穿电压。sgt运用了电荷耦合效应,不仅有传统槽栅vdmos结构的pn结垂直耗尽区域,而且引入了水平耗尽。从而可以将sgt mo的内部电场分布从三角形分布优化为近似矩形分布。同时,与普通的vdmos相比,屏蔽栅接源极电位使得sgt的输出电容更大,随着sgt越来越广泛的被用于开关电路中,较大的输出电容造成转换过程中的关断时间延长,影响开关速度、增大开关损耗,制约了系统整体性能的提升。

技术实现思路

1、鉴于以上所述现有技术的缺点,本发明的目的在于提供一种具有双层场板的双沟槽sgt器件。

2、为实现上述发明目的,本发明技术方案如下:

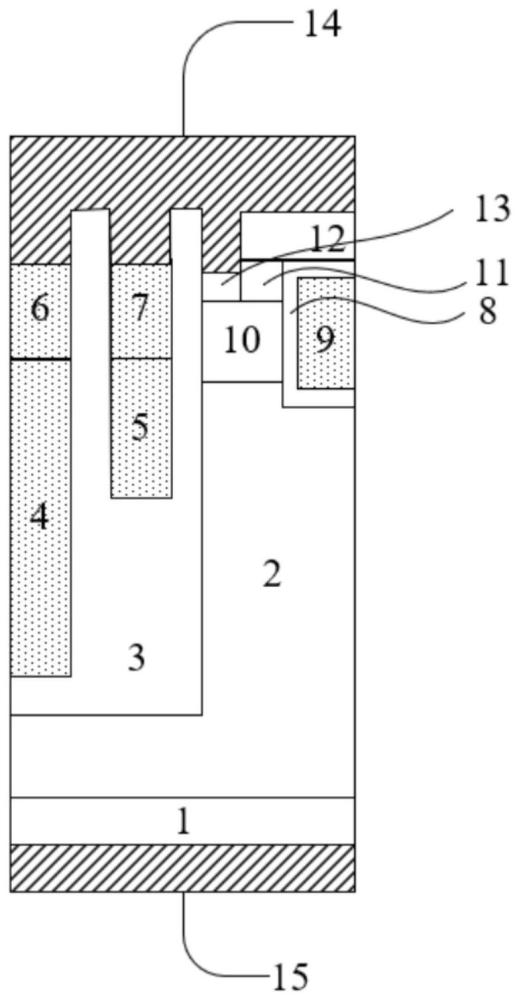

3、一种具有双层场板的双沟槽sgt器件,包括n型衬底1、n型外延层2、屏蔽栅沟槽、控制栅沟槽、体区10和底层金属15;

4、其中,所述n型外延层2位于n型衬底1的上表面;所述屏蔽栅沟槽、控制栅沟槽分别位于n型外延层2的左上表面和右上表面;

5、所述屏蔽栅沟槽填充屏蔽栅绝缘介质3,内部有第一场板和第二场板;所述第一场板由p型多晶硅a6和轻掺杂n型多晶硅a4构成;所述p型多晶硅a6在所述轻掺杂n型多晶硅a4的上方,p型多晶硅a6和轻掺杂n型多晶硅a4相互接触、上下相连;所述第二场板由p型多晶硅b7和轻掺杂n型多晶硅b5构成;所述p型多晶硅b7在所述轻掺杂n型多晶硅b5的上方,p型多晶硅b7和轻掺杂n型多晶硅b5相互接触、上下相连;所述第二场板在第一场板的右侧,二者通过绝缘介质相隔离;

6、所述控制栅沟槽填充控制栅绝缘介质8,控制栅绝缘介质8内部有n型掺杂的控制栅多晶硅9;所述屏蔽栅绝缘介质3所在的沟槽深度大于所述控制栅绝缘介质8所在的沟槽深度;所述屏蔽栅沟槽、控制栅沟槽分立于体区10的两侧;所述体区10的上表面有p型掺杂的欧姆接触区13、n型掺杂的源区11;所述欧姆接触区13在n型掺杂的源区11的左侧,欧姆接触区13与屏蔽栅沟槽右侧面接触,源区11与控制栅绝缘介质8左侧面接触;所述p型多晶硅a6、p型多晶硅b7、欧姆接触区13、n型掺杂的源区11通过顶层金属14直接接触相连,器件表面除了p型多晶硅a6、p型多晶硅b7、源区11、欧姆接触区13的其余部分通过表面绝缘介质层12与顶层金属14相隔离;所述底层金属15在器件的下表面。

7、作为优选方式,所述顶层金属14和底层金属15的材料选自铝、铝铜合金、或铜。

8、作为优选方式,所述屏蔽栅绝缘介质3和控制栅绝缘介质8的材料是二氧化硅。

9、作为优选方式,所述第二场板的深度小于第一场板的深度,即p型多晶硅a6和n型多晶硅a4的深度总和,小于p型多晶硅b7和轻掺杂n型多晶硅b5深度的总和。

10、作为优选方式,所有的n型区均与所有的p型区对换,对换后成为一种相反导电类型的器件。

11、作为优选方式,整个器件的材料是体硅、或碳化硅、或砷化镓或锗硅。

12、作为优选方式,轻掺杂的掺杂浓度小于1e18。

13、本发明的第二个目的是提供一种具有双层场板的双沟槽sgt器件的制备方法,包括如下步骤:

14、(1)、单晶硅准备及外延生长:选用重掺杂的n型衬底1,晶向为<100>,在n型衬底1上生长一定厚度和掺杂浓度的n型外延层2;

15、(2)、刻蚀屏蔽栅沟槽:通过刻蚀硅形成容纳屏蔽栅绝缘介质3、第一场板和第二场板的屏蔽栅沟槽;

16、(3)、在屏蔽栅沟槽内形成屏蔽栅绝缘介质3,采取淀积或者热生长的方式;

17、(4)、在屏蔽栅沟槽中刻蚀绝缘介质,形成后续淀积轻掺杂n型多晶硅b5和p型多晶硅b7的沟槽;

18、(5)、淀积轻掺杂n型多晶硅a4和轻掺杂n型多晶硅b5,轻掺杂n型多晶硅a4和轻掺杂n型多晶硅b5的表面低于器件表面;

19、(6)、淀积重掺杂的p型多晶硅a6和重掺杂的p型多晶硅b7,最后使用化学机械抛光,保证重掺杂的p型多晶硅a6、重掺杂的p型多晶硅b7的表面与器件表面持平;

20、(7)、刻蚀硅,形成控制栅沟槽;

21、(8)、热生长形成控制栅绝缘介质8;

22、(9)、淀积多晶硅,在控制栅绝缘介质8上淀积多晶硅,形成n型掺杂的控制栅多晶硅9;

23、(10)、注入p型杂质形成体区10;

24、(11)、通过光刻露出源区对应的位置,注入n型杂质形成源区11;

25、(12)、在器件表面淀积表面绝缘介质层12作为隔离;

26、(13)、在需要形成接触的位置,即第一场板、第二场板和欧姆接触区13的表面,通过光刻暴露出表面,刻蚀对应位置的绝缘介质层,并且在欧姆接触孔注入p型杂质;

27、(14)、在器件表面淀积顶层金属14作为源极接触,在器件底部淀积底层金属15作为漏极接触。

28、作为优选方式,所述的制备方法中:重掺杂的掺杂浓度大于1e18,轻掺杂的掺杂浓度小于1e18。

29、下面从两个方面说明本发明的工作原理:

30、(1)器件的正向导通

31、本发明所提供的一种具有双层场板的双沟槽sgt器件,其正向导通时电极的连接方式为:n型掺杂的控制栅多晶硅9作为控制栅接栅电位,顶层金属14接零电位,底层金属15接漏极高电位。当栅电位增加至大于阈值电压时,在体区10靠近控制栅绝缘介质8的一侧形成反型层沟道,在底层金属15高电位作用下,形成一条从源区11经由反型层、n型外延层2、n型衬底1到达底层金属15的电流通路,产生正向电流、器件正向导通。

32、(2)器件的反向阻断

33、本发明所提供的一种具有双层场板的双沟槽sgt器件,其反向阻断时电极的连接方式为:n型掺杂的控制栅多晶硅9接零电位,顶层金属14接零电位,底层金属15接漏极高电位。由于底层金属15接高电位,体区10和n型外延层2形成反向偏置的pn结,由该pn结承担反向耐压;同时第一场板和第二场板接零电位使得n型外延层2靠近屏蔽栅绝缘介质3的一层产生耗尽层。与传统的sgt相比,反偏状态下第一场板中p型多晶硅a6和轻掺杂n型多晶硅a4形成的多晶硅pn结反向偏置,第二场板中p型多晶硅b7和轻掺杂n型多晶硅b5形成的多晶硅pn结反向偏置,耗尽区向轻掺杂n型多晶硅a4和轻掺杂n型多晶硅b5一侧扩展形成pn结耗尽区电容,与原有的输出电容部分串联,从而使得整体的输出电容得到下降。

34、本发明的有益效果为:相比于传统sgt,本发明所提供的sgt结构具有双层场板结构,当器件处于反向阻断状态时,受到第二场板耗尽的漂移区区域较浅,受到第一场板耗尽的漂移区区域更深,由于第二场板处的绝缘介质层厚度远远小于第一场板对应的绝缘介质层厚度,因此可以抬升第二场板对应深度处的纵向电场,使电场分布更均匀、其形状更加接近于矩形,进一步优化纵向电场的分布、优化导通电阻与击穿电压之间的关系。同时,第一场板由上下相连的p型多晶硅a6和轻掺杂n型多晶硅a4组成,在起到场板作用的同时,内部形成一个多晶硅pn结,当器件处于关态时,该多晶硅pn结处于反向偏置的状态,pn结耗尽区将向下耗尽轻掺杂n型多晶硅a4,从而引入多晶硅pn结耗尽区电容,该电容与原有的输出电容部分串联,器件整体的输出电容减小。同理,第二场板中的p型多晶硅b7和轻掺杂n型多晶硅b5具有相似功能。

- 还没有人留言评论。精彩留言会获得点赞!