半导体结构及其制备方法与流程

本技术涉及半导体,尤其涉及一种半导体结构及其制备方法。

背景技术:

1、随着半导体存储器件的发展,具有高密度的数据存储单元的半导体存储器件的需求也在持续增长,因此,具有垂直堆叠多个数据存储单元层的三维存储器成为研究的热点。

2、三维存储器包括衬底及堆叠设置在衬底上的数个叠层结构。例如,在衬底上堆叠设置有第一叠层结构和第二叠层结构,位于上部的第一叠层结构包括第一贯穿结构;位于下部的第二叠层结构包括第二贯穿结构,且第一贯穿结构的顶部与第二贯穿结构的底部接触并电连接。

3、然而,当前上述三维存储器,其第一贯穿结构与第二贯穿结构电连接可靠性差,降低了三维存储器的良率。

技术实现思路

1、鉴于上述问题,本技术实施例提供一种半导体结构及其制备方法,其能够提升三维存储器的良率。

2、为了实现上述目的,本技术实施例提供如下技术方案:

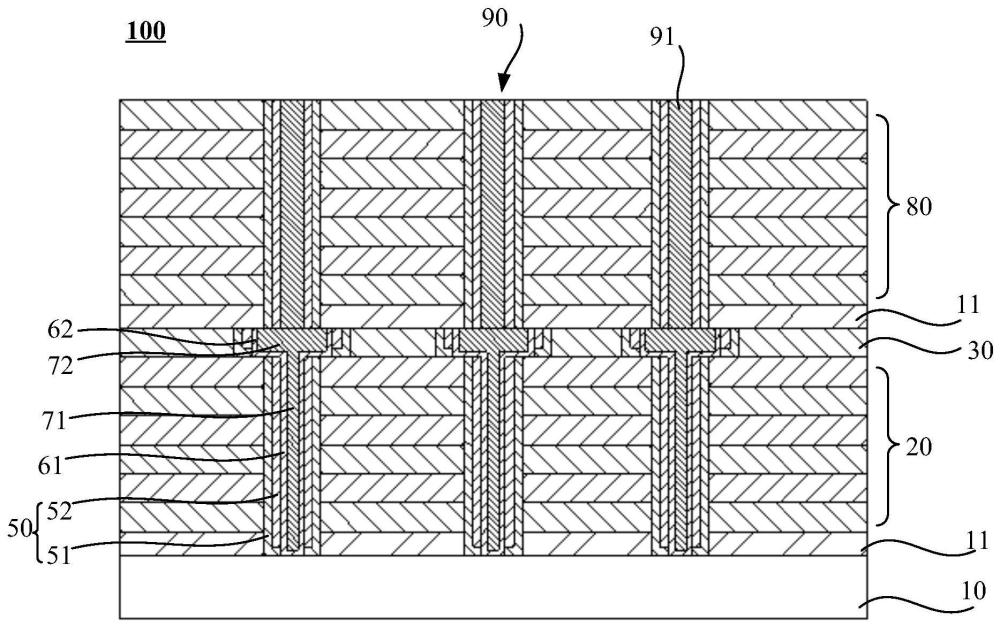

3、本技术实施例的第一方面提供一种半导体结构,其包括:衬底;第一堆叠层,设置于所述衬底之上;第一贯穿结构,设置在所述第一堆叠层内,所述第一贯穿结构包括第一侧壁结构和设置于所述第一侧壁结构上的第一阻障层;隔离层,设置于所述第一堆叠层之上;接触垫,设置于所述隔离层内,所述接触垫完全覆盖所述第一贯穿结构;第二侧壁结构,设置于所述接触垫与所述隔离层之间;第二阻障层,设置于所述接触垫的侧壁和底面上;第二贯穿结构,设置于所述接触垫上并至少部分接触所述接触垫;其中,所述接触垫的底部尺寸大于所述第一贯穿结构的顶部尺寸。

4、在一种可选的实施例中,所述第一阻障层分别与所述第一侧壁结构和部分所述衬底接触;所述第二阻障层分别与所述接触垫、所述第二侧壁结构和部分所述第一堆叠层接触。

5、在一种可选的实施例中,所述第一阻障层和所述第二阻障层为一体结构。

6、在一种可选的实施例中,所述第一贯穿结构还包括第一导电插塞,所述接触垫至少部分接触所述第一导电插塞。

7、在一种可选的实施例中,所述接触垫与所述第一导电插塞为一体结构。

8、在一种可选的实施例中,所述第一阻障层与所述接触垫的部分底面和所述第一导电插塞接触。

9、在一种可选的实施例中,所述第二贯穿结构还包括第二导电插塞,所述接触垫至少部分接触所述第二导电插塞。

10、在一种可选的实施例中,所述第一堆叠层包括交替设置的介电层和导电层。

11、在一种可选的实施例中,所述第一侧壁结构和所述第二侧壁结构包括相同的材料层。

12、在一种可选的实施例中,所述第一侧壁结构和所述第二侧壁结构包括依次设置的金属氧化物层及第二阻障层。

13、在一种可选的实施例中,所述第一贯穿结构、所述接触垫、所述第二贯穿结构错位排列。

14、在一种可选的实施例中,所述半导体结构还包括:第二堆叠层,包括交替设置的介电层和导电层;所述第二贯穿结构位于所述第二堆叠层内。

15、本技术实施例的第二方面提供一种半导体结构的制备方法,包括:

16、提供衬底;

17、在所述衬底上形成第一堆叠层及覆盖所述第一堆叠层的隔离层;

18、对所述隔离层、所述第一堆叠层进行刻蚀,分别在所述第一堆叠层内形成第一沟道孔;以及在所述隔离层内形成与所述第一沟道孔连通的凹槽,所述凹槽的底部宽度大于所述第一沟道孔的顶部宽度;

19、在所述第一沟道孔和所述凹槽内形成侧壁层;

20、对所述侧壁层进行蚀刻,形成设置在所述第一沟道孔中的第一侧壁结构和设置在所述凹槽中的第二侧壁结构;

21、在所述凹槽及所述第一沟道孔内形成阻障材料层,且所述阻障材料层覆盖所述第一侧壁结构、所述第二侧壁结构及暴露于所述凹槽内的部分所述第一堆叠层;

22、在所述凹槽内及所述第一沟道孔内分别形成接触垫和第一导电插塞,所述第一导电插塞、部分所述阻障材料层和所述第一侧壁结构构成第一贯穿结构,所述接触垫完全覆盖所述第一贯穿结构,且所述接触垫的底部尺寸大于所述第一贯穿结构的顶部尺寸;

23、在所述第一堆叠层上形成第二堆叠层,所述第二堆叠层具有与部分所述接触垫接触的第二贯穿结构。

24、在一种可选的实施例中,所述对所述隔离层、所述第一堆叠层进行刻蚀还包括:

25、在所述隔离层上形成第一掩膜图案;

26、利用所述第一掩膜图案对所述隔离层、所述第一堆叠层进行刻蚀,并形成第一沟道孔;

27、对所述第一掩膜图案进行刻蚀并形成第二掩膜图案;

28、利用所述第二掩膜图案对所述隔离层进行刻蚀,以在所述隔离层内形成与所述第一沟道孔连通的凹槽。

29、在一种可选的实施例中,所述对所述侧壁层进行蚀刻还包括:

30、对位于所述第一沟道孔的底部的部分所述侧壁层进行刻蚀,以使部分所述衬底暴露于所述第一沟道孔内;

31、对位于所述凹槽的底部的部分所述侧壁层进行刻蚀,以使部分所述第一堆叠层暴露于所述凹槽内,并形成互不接触的所述第一侧壁结构和所述第二侧壁结构。

32、在一种可选的实施例中,所述在所述凹槽及所述第一沟道孔内形成阻障层阻障材料层,包括:在所述凹槽和所述第一沟道孔内沉积形成所述阻障材料层,所述阻障层阻障材料层覆盖第一侧壁结构、第二侧壁结构、部分暴露于所述沟道孔内的所述衬底以及部分暴露于所述凹槽内的所述第一堆叠层。

33、在一种可选的实施例中,所述阻障材料层还包括覆盖所述第一侧壁结构的第一阻障层和覆盖所述第二侧壁结构的第二阻障层。

34、在一种可选的实施例中,所述在所述第一沟道孔和所述凹槽内形成侧壁层还包括:在所述第一沟道孔和所述凹槽内依次沉积形成金属氧化物层及第三阻障层,所述金属氧化物层及所述第三阻障层构成所述侧壁层。

35、在一种可选的实施例中,所述第一贯穿结构、所述接触垫、所述第二贯穿结构错位排列。

36、在一种可选的实施例中,所述第一导电插塞与所述第一阻障层及所述接触垫接触。

37、在一种可选的实施例中,所述第二贯穿结构还包括第二导电插塞,所述接触垫至少部分接触所述第二导电插塞。

38、与相关技术相比,本技术实施例提供的半导体结构及其制备方法,具有以下优点:

39、本技术提供的半导体结构及其制备方法,其中半导体结构包括第一堆叠层、第一贯穿结构和第二贯穿结构,第一贯穿结构设置于第一堆叠层内,且第一贯穿结构的顶部具有完全覆盖其的接触垫,且接触垫的底部尺寸大于第一贯穿结构的顶部尺寸。

40、进一步地,接触垫的周围设置有第二阻障层,通过第二阻障层与第一侧壁结构、第二侧壁结构及部分第一堆叠层隔离。第二贯穿结构位于接触垫的上方,并与接触垫电连接,即第一贯穿结构和第二贯穿结构通过接触垫电连接。

41、相关技术中,三维存储器的第一贯穿结构和第二贯穿结构容易出现错位现象,导致第一贯穿结构与第二贯穿结构接触面积小,甚至两者无接触面积,影响第一贯穿结构和第二贯穿结构的电连接可靠性。

42、然而,本技术实施例提供的半导体结构,接触垫的底部尺寸大于第一贯穿结构的顶部尺寸,可增大第一贯穿结构和第二贯穿结构的接触面积,提升第一贯穿结构与第二贯穿结构电连接可靠性差,进而提高三维存储器的良率。

43、除了上面所描述的本公开实施例解决的技术问题、构成技术方案的技术特征以及由这些技术方案的技术特征所带来的有益效果外,本公开实施例提供的半导体结构及其制备方法所能解决的其他技术问题、技术方案中包含的其他技术特征以及这些技术特征带来的有益效果,将在具体实施方式中作出进一步详细的说明。

- 还没有人留言评论。精彩留言会获得点赞!