一种多面管脚芯片封装方法及封装结构与流程

本技术涉及芯片封装,具体而言,涉及一种多面管脚芯片封装方法及封装结构。

背景技术:

1、现有技术需要利用多面管脚芯片封装方法对多面管脚芯片(顶面、底面和两个相互对称的侧面上均设有管脚的芯片)进行封装,现有的多面管脚芯片封装方法的具体流程为:基于打线设备利用引线将多面管脚芯片的多个面上的管脚引出至同一平面(例如利用引线将底面和两个侧面上的管脚引出至顶面);对完成管脚引出的多面管脚芯片进行表面封装;将完成表面封装的多面管脚芯片贴装到封装基板上。由于现有的多面管脚芯片封装方法需要利用打线设备将多面管脚芯片的多个面上的管脚引出至同一平面,而打线设备的设备成本高,且引线容易断开脱落和对多面管脚芯片的焊盘界面造成永久性损害,因此现有的多面管脚芯片封装方法存在由于需要利用打线设备将多面管脚芯片的多个面上的管脚引出至同一平面而导致多面管脚芯片的封装成本高以及由于引线容易断开脱落和对多面管脚芯片的焊盘界面造成永久性损害而导致多面管脚芯片封装方法得到的封装结构的可靠性低的问题。

2、针对上述问题,目前尚未有有效的技术解决方案。

技术实现思路

1、本技术的目的在于提供一种多面管脚芯片封装方法及封装结构,能够有效地解决由于需要利用打线设备将多面管脚芯片的多个面上的管脚引出至同一平面而导致多面管脚芯片的封装成本高以及由于引线容易断开脱落和对多面管脚芯片的焊盘界面造成永久性损害而导致多面管脚芯片封装方法得到的封装结构的可靠性低的问题。

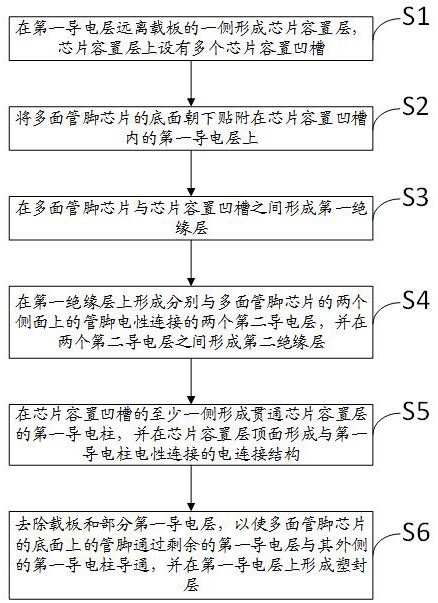

2、第一方面,本技术提供了一种多面管脚芯片封装方法,多面管脚芯片的顶面、底面和两个相互对称的侧面上均设有管脚,多面管脚芯片封装方法包括以下步骤:

3、s1、在第一导电层远离载板的一侧形成芯片容置层,芯片容置层上设有多个芯片容置凹槽;

4、s2、将多面管脚芯片的底面朝下贴附在芯片容置凹槽内的第一导电层上;

5、s3、在多面管脚芯片与芯片容置凹槽之间形成第一绝缘层;

6、s4、在第一绝缘层上形成分别与多面管脚芯片的两个侧面上的管脚电性连接的两个第二导电层,并在两个第二导电层之间形成第二绝缘层;

7、s5、在芯片容置凹槽的至少一侧形成贯通芯片容置层的第一导电柱,并在芯片容置层顶面形成与第一导电柱电性连接的电连接结构;

8、s6、去除载板和部分第一导电层,以使多面管脚芯片的底面上的管脚通过剩余的第一导电层与其外侧的第一导电柱导通,并在第一导电层上形成塑封层。

9、本技术提供的一种多面管脚芯片封装方法,先将多面管脚芯片的底面朝下贴附在芯片容置凹槽内的第一导电层上,并在多面管脚芯片与芯片容置凹槽之间形成第一绝缘层,再在第一绝缘层上形成分别与两个侧面上的管脚电性连接的两个第二导电层,并在两个第二导电层之间形成第二绝缘层,然后在芯片容置凹槽的至少一侧形成第一导电柱,并在芯片容置层顶面形成与第一导电柱电性连接的电连接结构,由于本技术能够通过两个第二导电层分别将多面管脚芯片的两个侧面上的管脚引出至多面管脚芯片的顶面,而本技术还能够通过第一导电层和第一导电柱将多面管脚芯片的底面上的管脚引出至多面管脚芯片的顶面,因此本技术相当于通过第一导电层、第二导电层和第一导电柱将多面管脚芯片的多个面上的管脚引出至同一平面,即本技术无需利用打线设备将多面管脚芯片的多个面上的管脚引出至同一平面,从而有效地解决由于需要利用打线设备将多面管脚芯片的多个面上的管脚引出至同一平面而导致多面管脚芯片的封装成本高以及由于引线容易断开脱落和对多面管脚芯片的焊盘界面造成永久性损害而导致多面管脚芯片封装方法得到的封装结构的可靠性低的问题。

10、可选地,步骤s5包括:

11、s51、在芯片容置凹槽的至少一侧形成贯通芯片容置层的第一导电柱,并在芯片容置层顶面形成分别与第一导电柱、多面管脚芯片的顶面和两个第二导电层电性连接的第一再布线层;

12、s52、在第一再布线层上形成焊球。

13、可选地,步骤s51包括:

14、s511、在芯片容置层顶面形成第一图形化钝化膜层,并在芯片容置凹槽的至少一侧形成第一导电柱;

15、s512、基于第一图形化钝化膜层在芯片容置层顶面和第一导电柱顶面依次形成金属种子层和金属铜层,以形成第一金属布线层;

16、s513、在第一金属布线层上形成第一图形化感光膜层,并基于第一图形化感光膜层对第一金属布线层进行刻蚀,以去除位于第一导电柱、多面管脚芯片的顶面上的管脚和两个第二导电层外的第一金属布线层;

17、s514、去除第一图形化感光膜层,并在第一图形化钝化膜层上形成第二图形化钝化膜层;

18、s515、在第二图形化钝化膜层上形成第三图形化钝化膜层,并基于第三图形化钝化膜层在第一金属布线层上依次形成金属种子层和金属铜层,以形成第二金属布线层。

19、由于金属种子层能够增加金属铜层与接触面之间的结合力,因此该技术方案能够有效地避免出现由于金属铜层与接触面的结合力过小而导致金属铜层脱落的情况。

20、可选地,s511包括:

21、s5111、在芯片容置层顶面形成第一钝化膜层;

22、s5112、基于光刻工艺或激光镭射工艺利用第一预设图案掩膜板对第一钝化膜层进行刻蚀,以在芯片容置层顶面形成第一图形化钝化膜层;

23、s5113、基于刻蚀工艺和电镀工艺利用第一图形化钝化膜层在芯片容置凹槽的至少一侧形成贯通芯片容置层的第一导电柱。

24、可选地,步骤s6包括:

25、s61、去除载板,并基于干法刻蚀工艺或湿法刻蚀工艺对第一导电层进行刻蚀,以去除部分第一导电层和使多面管脚芯片的底面上的管脚通过剩余的第一导电层与其外侧的第一导电柱导通;

26、s62、在第一导电层上形成塑封层。

27、可选地,步骤s5包括:

28、s51’、在芯片容置凹槽的至少一侧形成贯通芯片容置层的第一导电柱,并在芯片容置凹槽的任意一侧形成贯通芯片容置层的第二导电柱;

29、s52’、在芯片容置层顶面形成与第一导电柱和第二导电柱电性连接的电连接结构;

30、步骤s6还包括执行于步骤s61和步骤s62之间的步骤:

31、s63、在第一导电层上形成第四图形化钝化膜层;

32、s64、基于第四图形化钝化膜层形成与第二导电柱电性连接的第三导电层;

33、s65、在第四图形化钝化膜层上形成第五图形化钝化膜层,并基于第五图形化钝化膜层形成与第三导电层电性连接的第四导电层;

34、s66、将常规芯片的有源面朝下贴附到第四导电层上;

35、步骤s62包括:

36、s621、对常规芯片进行塑封,以在第一导电层上形成塑封层。

37、由于现有技术需要利用多个硅通孔转接板才能够将具有不同性能的芯片集成在同一封装结构中,而本技术能够通过第一导电层、第二导电层、第一导电柱、第三导电层、第四导电层和第二导电柱的配合将具有不同性能的芯片集成在同一封装结构中,因此本技术无需使用多个硅通孔转接板,即本技术相当于在无需使用硅通孔转接板的情况下实现三维扇出型封装结构,从而有效地降低三维扇出型封装结构的封装成本和三维扇出型封装结构的封装体积。

38、可选地,步骤s1包括:

39、s11、在第一导电层远离载板的一侧形成粘接胶层;

40、s12、在粘接胶层上形成第二图形化感光膜层;

41、s13、基于第二图形化感光膜层对粘接胶层进行刻蚀,以形成其上设有多个芯片容置凹槽的芯片容置层。

42、可选地,步骤s3包括:

43、s31、在多面管脚芯片与芯片容置凹槽之间的缝隙填充底填胶,以形成第一绝缘层。

44、可选地,多面管脚芯片的左侧面和右侧面均设有管脚,步骤s4包括:

45、s41、在左侧面与芯片容置凹槽之间的缝隙和右侧面与芯片容置凹槽之间的缝隙填充导电胶或导电金属,以在第一绝缘层上形成分别与两个侧面上的管脚电性连接的两个第二导电层;

46、s42、在多面管脚芯片的前侧面与芯片容置凹槽之间的缝隙和多面管脚芯片的后侧面与芯片容置凹槽之间的缝隙填充底填胶,以在两个第二导电层之间形成第二绝缘层。

47、第二方面,本技术还提供了多面管脚芯片封装结构,该多面管脚芯片封装结构由上述第一方面提供的多面管脚芯片封装方法制成。

48、本技术提供的一种多面管脚芯片封装结构,能够通过两个第二导电层分别将多面管脚芯片的两个侧面上的管脚引出至多面管脚芯片的顶面,并通过第一导电层和第一导电柱将多面管脚芯片的底面上的管脚引出至多面管脚芯片的顶面,因此本技术相当于通过第一导电层、第二导电层和第一导电柱将多面管脚芯片的多个面上的管脚引出至同一平面,即本技术无需利用打线设备将多面管脚芯片的多个面上的管脚引出至同一平面,从而有效地解决由于需要利用打线设备将多面管脚芯片的多个面上的管脚引出至同一平面而导致多面管脚芯片的封装成本高以及由于引线容易断开脱落和对多面管脚芯片的焊盘界面造成永久性损害而导致多面管脚芯片封装结构的可靠性低的问题。

49、由上可知,本技术提供的一种多面管脚芯片封装方法及封装结构,先将多面管脚芯片的底面朝下贴附在芯片容置凹槽内的第一导电层上,并在多面管脚芯片与芯片容置凹槽之间形成第一绝缘层,再在第一绝缘层上形成分别与两个侧面上的管脚电性连接的两个第二导电层,并在两个第二导电层之间形成第二绝缘层,然后在芯片容置凹槽的至少一侧形成第一导电柱,并在芯片容置层顶面形成与第一导电柱电性连接的电连接结构,由于本技术能够通过两个第二导电层分别将多面管脚芯片的两个侧面上的管脚引出至多面管脚芯片的顶面,而本技术还能够通过第一导电层和第一导电柱将多面管脚芯片的底面上的管脚引出至多面管脚芯片的顶面,因此本技术相当于通过第一导电层、第二导电层和第一导电柱将多面管脚芯片的多个面上的管脚引出至同一平面,即本技术无需利用打线设备将多面管脚芯片的多个面上的管脚引出至同一平面,从而有效地解决由于需要利用打线设备将多面管脚芯片的多个面上的管脚引出至同一平面而导致多面管脚芯片的封装成本高以及由于引线容易断开脱落和对多面管脚芯片的焊盘界面造成永久性损害而导致多面管脚芯片封装方法得到的封装结构的可靠性低的问题。

- 还没有人留言评论。精彩留言会获得点赞!