封装结构及封装方法与流程

本发明实施例涉及半导体制造领域,尤其涉及一种封装结构及封装方法。

背景技术:

1、当前,半导体封装技术得到快速发展,电子器件封装的集成度越来越高。系统级封装(system in package,sip)是将不同功能的裸电子器件,包括cpu、gpu、存储器等集成在一个封装体内,从而实现整体性的电子器件结构。在系统级封装结构中,多颗射频、模拟电子器件或被动元器件的集成,电子器件及器件间的距离逐渐减小,从而导致系统级封装结构内部的器件之间的电磁干扰(electro-magnetic interference,emi)问题越来越突出,因此分区电磁屏蔽结构被大量应用。

2、现有的分区emi电磁干扰屏蔽技术主要包括利用打线制作笼状屏蔽区域结构,常规的衬底的接地布线层的焊盘设计在芯片周围,作为屏蔽区域的接地点,实现屏蔽功能。由于芯片与衬底之间的高频信号传输需要通过衬底中的布线层进行传输,需要设计多个布线层走线,例如:高频信号线、电源线以及接地布线层等。其中,接地布线层上端通过接地焊盘引出,以实现接地屏蔽功能。

技术实现思路

1、本发明实施例解决的问题是提供一种封装结构及封装方法,有利于保障封装结构的性能。

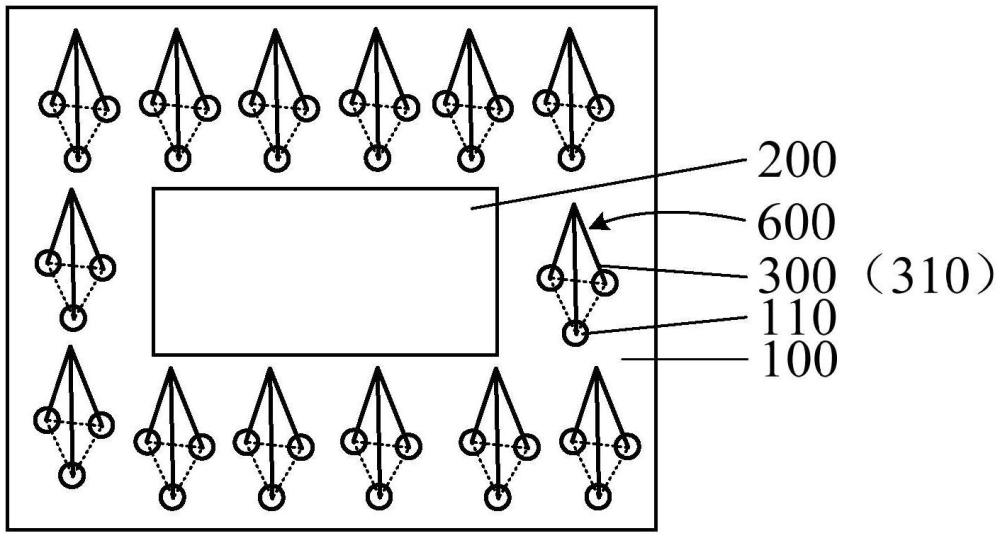

2、为解决上述问题,本发明提供一种封装结构,包括:基板;器件芯片,键合于基板上;多个导电结构,位于基板上且环绕器件芯片,每个导电结构包括多个导电线,导电线的至少一端位于基板上,导电线通过基板接地,多个导电线相交于基板上方,或者,多个导电线的延长线相交于基板上方。

3、可选的,导电线包括第一型导电线,第一型导电线的一端形成于基板上,另一端形成于器件芯片侧部的上方。

4、可选的,每个导电结构包括两个至五个第一型导电线。

5、可选的,每个导电结构包括三个第一型导电线,三个第一型导电线在基板上的一端呈三角状分布;或者,每个导电结构包括三个第一型导电线,三个第一型导电线在基板上的一端呈直线状分布。

6、可选的,导电结构中,三个第一型导电线在基板上的一端呈直线状分布,直线与基板的水平方向具有锐角夹角。

7、可选的,直线与基板的水平方向的夹角为30°至60°。

8、可选的,导电线包括第二型导电线,第二型导电线的两端均形成于基板上。

9、可选的,导电结构中,以第二型导电线所在平面与基板相垂直。

10、可选的,导电结构中,多个第二型导电线的交点高于每个第二型导电线总高度的二分之一。

11、可选的,导电结构中,多个第二型导电线的交点为每个第二型导电线的最高点。

12、可选的,导电线还包括第一型导电线,第一型导电线的一端形成于基板上,另一端形成于器件芯片侧部的上方。

13、可选的,导电结构中,第一型导电线或其延长线经过多个第二型导电线的交点。

14、可选的,导电结构中,第一型导电线或其延长线经过每个第二型导电线的最高点。

15、可选的,第一型导电线在基板上的一端,位于第二型导电线在基板上的端点构成的形状的内部。

16、可选的,导电结构中,第一型导电线垂直于基板。

17、可选的,导电结构中,多个导电线的另一端相交于同一点,或者,多个导电线的延长线相交于同一点。

18、可选的,导电结构中,多个导电线的交点在基板上的投影,位于多个导电线在基板上的端点构成的形状的内部。

19、可选的,导电结构中,多个导电线的交点在基板上的投影,位于多个导电线在基板上的端点构成的形状的中心点。

20、可选的,封装结构还包括:塑封层,位于基板上并覆盖器件芯片和多个导电结构;屏蔽层,覆盖塑封层,并与导电结构电连接。

21、可选的,塑封层露出导电结构;屏蔽层通过覆盖塑封层露出的导电结构与导电结构电连接;或者,塑封层包覆导电结构;屏蔽层还覆盖塑封层和基板的侧壁并通过基板接地,屏蔽层通过基板与导电结构电连接。

22、可选的,封装结构还包括:接地焊垫,位于基板上并环绕器件芯片;导电线位于基板上的端点与接地焊垫电连接。

23、相应的,本发明实施例还提供一种封装方法,包括:提供基板,基板上形成有器件芯片;在基板上形成环绕器件芯片的多个导电结构,每个导电结构包括多个导电线,导电线的至少一端位于基板上,导电线通过基板接地,多个导电线相交于基板上方。

24、可选的,在基板上形成环绕器件芯片的多个导电结构的步骤中,依次形成每个导电结构。

25、可选的,采用打线工艺形成导电线。

26、可选的,采用打线工艺形成导电线的步骤中,采用第一打线模式形成第一型导电线,第一打线模式设置第一型导电线的一端形成于基板上,另一端形成于器件芯片侧部的上方;或者,采用打线工艺形成导电线的步骤中,采用第二打线模式形成第二型导电线,第二打线模式设置第二型导电线的两端均形成于基板上;或者,采用打线工艺形成导电线的步骤中,采用第一打线模式形成第一型导电线,采用第二打线模式形成第二型导电线,第一打线模式设置第一型导电线的一端形成于基板上,另一端形成于器件芯片侧部的上方,第二打线模式设置第二型导电线的两端均形成于基板上。

27、可选的,在基板上形成环绕器件芯片的多个导电结构后,封装方法还包括:形成覆盖器件芯片和多个导电结构的塑封层;平坦化塑封层,以去除部分厚度的塑封层;平坦化塑封层后,形成覆盖塑封层并与导电结构电连接的屏蔽层。

28、可选的,平坦化塑封层的步骤中,塑封层露出导电结构;形成覆盖塑封层并与导电结构电连接的屏蔽层的步骤中,屏蔽层通过覆盖塑封层露出的导电结构与导电结构电连接;或者,平坦化塑封层的步骤中,塑封层包覆导电结构;形成覆盖塑封层并与导电结构电连接的屏蔽层的步骤中,屏蔽层还覆盖塑封层和基板的侧壁并通过基板接地,屏蔽层通过基板与导电结构电连接。

29、与现有技术相比,本发明实施例的技术方案具有以下优点:

30、本发明实施例提供一种封装结构,多个导电结构位于基板上且环绕器件芯片,每个导电结构包括多个导电线,导电线的至少一端位于基板上,导电线通过基板接地,多个导电线相交于基板上方,或者,多个导电线的延长线相交于基板上方;本发明实施例中,多个导电结构位于基板上且环绕器件芯片,且导电线接地,则多个导电结构能够构成保护器件芯片的电磁屏蔽结构(例如,法拉第笼),每个导电结构包括多个导电线,多个导电线相交于基板上方,或者,多个导电线的延长线相交于基板上方,则说明在导电结构的形成过程中,多个导电线能够通过相交而相互支撑,减小导电线发生倾倒而与器件芯片或其他焊线短接的概率,有利于提高每个导电结构的稳固性,从而有利于保障多个导电结构构成的电磁屏蔽结构的屏蔽效果,进而有利于保障封装结构的性能。

31、本发明实施例提供一种封装方法,在基板上形成环绕器件芯片的多个导电结构,每个导电结构包括多个导电线,导电线的至少一端位于基板上,导电线通过基板接地,多个导电线相交于基板上方;本发明实施例中,多个导电结构位于基板上且环绕器件芯片,且导电线接地,则多个导电结构能够构成保护器件芯片的电磁屏蔽结构(例如,法拉第笼),每个导电结构包括多个导电线,多个导电线相交于基板上方,则多个导电线能够通过相交而相互支撑,减小导电线发生倾倒而与器件芯片或其他焊线短接的概率,有利于提高每个导电结构的稳固性,从而有利于保障多个导电结构构成的电磁屏蔽结构的屏蔽效果,进而有利于保障封装结构的性能。

- 还没有人留言评论。精彩留言会获得点赞!