一种用于降低3DNAND晶圆翘曲的方法

本发明涉及半导体器件,尤其涉及一种用于降低3d nand晶圆翘曲的方法。

背景技术:

1、在当今社会生活中,航空航天、消费类电子等不同领域对半导体器件的需求不断增大,尤其是计算机和智能手机等便携式电子设备对存储器容量和性能的需求,存储器近十年来已成为推动全球半导体市场增长的主要动力之一,在半导体产业中的比重也越来越高。3d nand因其存储容量大、成本低的优势被广泛应用于电子设备中。近年来,随着人工智能和物联网的发展,对存储器的容量提出了更大的要求,3d nand堆叠层数不断增加,同时单位比特的成本降低。但是由于高堆叠层数3d nand在制作过程中运用了大量的高应力材料和复杂的工艺过程,会导致应力集中致使晶圆发生严重的翘曲,这样会导致后续键合过程中无法准确对准,降低器件的良率,甚至器件的核心存储功能。

2、目前降低3d nand的晶圆翘曲方法主要集中在优化复杂结构工艺和减小材料应力等方面,存在以下几个问题,一是研发周期长,研发成本高;现有的降低晶圆翘曲的方法主要集中在优化复杂结构工艺和减小材料应力等方面,这需要大量的实验和模拟来优化工艺参数和材料选择,研发周期长,投入成本高。二是无法针对性调控;现有的方法都是在3dnand制作完成前进行的,无法根据3d nand制作完成后的实际翘曲分布情况进行针对性的调控,因为3dnand的翘曲分布受到多种因素的影响,如应力分布、工艺参数、材料特性等,仅在制作前优化这些参数,无法完全消除翘曲,且不同批次、不同位置的翘曲情况可能差异较大,缺乏一种根据实际翘曲情况进行针对性调节的方法。三是可能影响器件性能;一些现有的方法如优化复杂结构和材料,虽然能在一定程度上减小翘曲,但可能会对器件的关键性能参数如电学特性、可靠性等产生负面影响。因为3d nand的结构和材料都是经过严格优化的,为满足器件性能要求,对其进行改变可能带来一些副作用。

技术实现思路

1、有鉴于此,本发明提出了一种用于降低3d nand晶圆翘曲的方法,以解决现有技术中无法根据3d nand制作完成后的实际翘曲分布情况进行针对性的调控的问题。

2、本发明的技术方案是这样实现的:

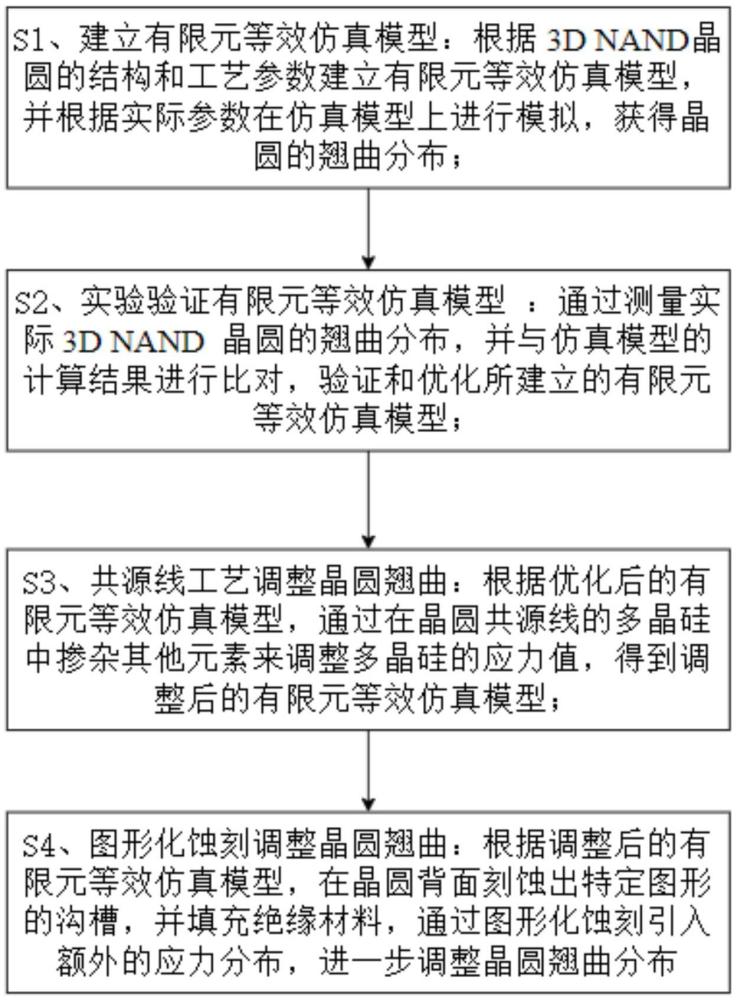

3、本发明提供了一种用于降低3d nand晶圆翘曲的方法,包括以下步骤:

4、s1、建立有限元等效仿真模型:根据3d nand晶圆的结构和工艺参数建立有限元等效仿真模型,并根据实际参数在仿真模型上进行模拟,获得晶圆的翘曲分布;

5、s2、实验验证有限元等效仿真模型:通过测量实际3d nand晶圆的翘曲分布,并与仿真模型的计算结果进行比对,验证和优化所建立的有限元等效仿真模型;

6、s3、共源线工艺调整晶圆翘曲:根据优化后的有限元等效仿真模型,通过在晶圆共源线的多晶硅中掺杂其他元素来调整多晶硅的应力值,得到调整后的有限元等效仿真模型;

7、s4、图形化蚀刻调整晶圆翘曲:根据调整后的有限元等效仿真模型,在晶圆背面刻蚀出特定图形的沟槽,并填充绝缘材料,通过图形化蚀刻引入额外的应力分布,进一步调整晶圆翘曲分布。

8、在以上技术方案的基础上,优选的,步骤s1具体包括以下步骤:

9、s11、获取所述3d nand晶圆的结构参数,基于所述结构参数将所述3dnand晶圆的复杂结构等效为厚度均匀的薄膜层,通过有限元分析软件构建所述3d nand晶圆的等效薄膜-衬底模型;

10、s12、基于所述等效薄膜-衬底模型建立热力耦合模型,根据所述3d nand晶圆的实际热处理工艺参数,在所述有限元分析软件中设置匹配的热处理参数和边界条件;

11、s13、运行基于所述等效薄膜-衬底模型的有限元热-结构耦合仿真计算,模拟所述3d nand晶圆在经历热处理全过程后的晶圆温度场和翘曲变形分布情况;

12、s14、对仿真结果进行后处理和分析,提取3d nand晶圆翘曲的关键特征参数。

13、在以上技术方案的基础上,优选的,步骤s2具体包括以下步骤:

14、s21、使用晶圆翘曲测量设备对实际3d nand晶圆进行翘曲测试,获取晶圆表面的初始实测翘曲分布参数;

15、s22、将步骤s21中获取的初始实测翘曲分布参数与步骤s14中的有限元仿真计算结果进行定量比较,当初始实测翘曲分布参数与仿真结果之间的偏差在预设阈值范围内时,确认建立的有限元等效仿真模型为有效;当初始实测翘曲分布参数与仿真结果之间的偏差超出预设阈值范围时,返回步骤s12,对等效薄膜层的结构参数进行调整。

16、在以上技术方案的基础上,优选的,所述预设阈值为实测翘曲分布参数与仿真计算结果之间的平均偏差百分比不超过10%,且最大偏差百分比不超过20%;

17、平均偏差百分比=(σ|实测值i-仿真值i|/实测值i)/n×100%,

18、最大偏差百分比=max{|实测值i-仿真值i|/实测值i}×100%,

19、式中,i为晶圆表面翘曲测点的编号,取值范围为1至n;n为总测点数;实测值i和仿真值i分别为第i个测点处的实测翘曲值和仿真计算翘曲值。

20、在以上技术方案的基础上,优选的,步骤s3具体包括以下步骤:

21、s31、在步骤s2中的有限元等效仿真模型中引入掺杂元素浓度参数,建立掺杂元素浓度与多晶硅薄膜内应力之间的定量函数关系;

22、s32、将该应力-掺杂浓度函数关系嵌入共源线材料属性定义中,获得不同掺杂条件下晶圆翘曲变形的结果,分析仿真结果,确定掺杂浓度与晶圆翘曲变形之间的关系,识别出最佳掺杂浓度范围;

23、s33、将仿真优化的掺杂浓度结果反馈至步骤s2的有限元等效仿真模型中,获得调整后的有限元等效仿真模型。

24、在以上技术方案的基础上,优选的,步骤s31中,掺杂元素包括砷、磷和硼。

25、在以上技术方案的基础上,优选的,步骤s4具体包括以下步骤:

26、s41、在步骤s3得到的有限元等效仿真模型的正面沉积保护层结构,所述保护层结构为非金属材料;

27、s42、在步骤s3得到的有限元等效仿真模型的背面刻蚀沟槽,通过调整沟槽的参数调整仿真模型的厚度,进而调整晶圆翘曲分布;

28、s43、刻蚀完成后,对蚀刻沟槽进行填充,然后在沟槽表面沉积氮化硅薄膜,完成刻蚀工艺。

29、在以上技术方案的基础上,优选的,步骤s42具体包括:

30、s421、将stoney公式引入仿真模型,建立非均匀薄膜的晶圆翘曲量与薄膜应力、厚度及衬底厚度的定量关系;

31、s422、计算步骤s3得到的调整后的有限元等效仿真模型的晶圆翘曲分布参数,基于所述定量关系确定刻蚀沟槽形状;

32、s423、基于刻蚀沟槽形状和定量关系,通过调节沟槽深度、宽度来实现对仿真模型在x方向和y方向上的翘曲分布的调节。

33、在以上技术方案的基础上,优选的,所述定量关系的表达式为:

34、

35、其中,r为衬底本身的几何半径,σx和σy分别是薄膜在x、y方向上的应力,bow x和bow y分别为晶圆在x、y方向上的翘曲,rx和ry分别为衬底在x、y方向上的曲率半径,σf为薄膜应力,es和vs分别为衬底的弹性模量和泊松比,r为衬底的曲率半径,ts和tf分别为衬底、薄膜厚度。

36、在以上技术方案的基础上,优选的,步骤s42中,刻蚀沟槽的方法为基于组合型刻蚀液进行刻蚀,组合型刻蚀液包括第一刻蚀液和第二刻蚀液,所述第一刻蚀液为磷酸、柠檬酸、草酸中的一种或多种;所述第二刻蚀液含有含氟化合物。

37、本发明的一种用于降低3d nand晶圆翘曲的方法相对于现有技术具有以下有益效果:

38、(1)通过建立有限元等效仿真模型,并通过实验验证优化该模型,为后续的工艺调整提供可靠的计算基础,该方法节省了大量实验时间和测量成本;

39、(2)通过在共源线多晶硅中掺杂其他元素的方式,调整多晶硅的应力状态,从而实现对晶圆翘曲的初步调整;在晶圆背面进行图形化蚀刻,形成特定的沟槽结构,并通过填充绝缘材料来引入额外的应力分布,进一步优化晶圆在x、y两个方向上的翘曲分布,该方法可以有效降低3d nand晶圆的整体翘曲,为后续的工艺流程和设备制造提供更加平整的基底,提高良品率和可靠性;

40、(3)通过有限元仿真模型的建立和实验验证,结合多工艺步骤的协同调控,体现了系统性和针对性,具有较强的工艺可控性和实用性;能够在3d nand器件制作完成之前获取晶圆的翘曲分布,这不同于以往的制造-测量-改善-制造流程,使得在制作过程中能够通过共源线改善工艺;

41、(4)本发明在晶圆背面进行图形化蚀刻和对共源线进行工艺改善都是在3dnand核心功能区之外进行的,能最小化晶圆翘曲调节方案对3d nand器件存储功能的损伤。

- 还没有人留言评论。精彩留言会获得点赞!