半导体结构及半导体结构的制作方法

本发明涉及半导体器件领域,尤其涉及一种半导体结构及半导体结构的制作方法。

背景技术:

1、人工突触器件在智能感知、机器学习和脑机接口等领域具有巨大的潜力,是实现神经形态计算的关键组成部分。然而,随着大数据时代电子数据的快速增长,迫切需要能够提供更快的计算速度和更低的能耗的计算技术。因此,在神经形态计算中制备人工突触阵列来构建高度并行处理和自适应学习的神经网络尤为重要。目前的研究主要集中在单个的人工突触器件上,而制备具有优异电性能和良好均匀性的高密度人工突触阵列仍然具有挑战性。在各种突触器件中,电解栅控突触晶体管(egt)因其高比电容(~1-10μf/cm2)、环境兼容性和低工作电压(<1v)而成为人工突触阵列单元的有利选择。电解质栅控突触晶体管(electrolyte-gated synaptic transistors,egt)由于其低工作电压、高比电容和环境兼容性等优点,在实现神经形态器件或架构中发挥着重要作用。

2、在生物神经系统中,突触是神经元之间传递信号的重要连接点。突触晶体管(synaptic transistor)是一种人工神经元器件,它模仿了生物神经元之间的突触连接。突触晶体管的主要特点是具有可调节的多级电导,依据电导的调整模拟生物中突触权重的调整,类似于生物突触中的突触可塑性。这意味着它可以根据输入信号的强度和频率来调整连接的强度(即电导大小),从而模拟学习和记忆功能。在人工智能和神经网络等领域中发挥作用。

3、在突触晶体管内,电解质材料是一种电子绝缘,离子导电的材料,基于电解质/半导体沟道界面处以及电解质/栅极界面处形成的双电层调制效应,突触晶体管工作时,“写”操作在栅极上,而“读”操作在半导体沟道覆盖的源漏极上。通过施加栅极电压,促使电解质中的离子迁移,从而调制电导。

4、突触晶体管阵列由于其具有多栅/单通道和单栅极/多通道的双电层调制效应有助于实现空间方向识别、声音定位和空间求和等空间相关功能而广泛应用。而基于电解质突触晶体管的突触晶体管阵列的制作过程中,电解质均匀地涂覆在阵列器件表面上。传统的电解质制备方法忽略了电解质的空间相关功能对阵列器件权重更新的影响,从而导致了严重的串扰问题。当对该种制备方法制备的突触晶体管阵列中的一个器件施加栅极电压时,会导致周围器件的电导率发生变化,随着阵列内器件密度的不断拓展,这种串扰问题越来越明显。

技术实现思路

1、本发明解决的技术问题是由于电解质的空间相关功能导致了严重的串扰问题,提供一种半导体结构及半导体结构的制作方法,解决了突触晶体管阵列内串扰的问题。

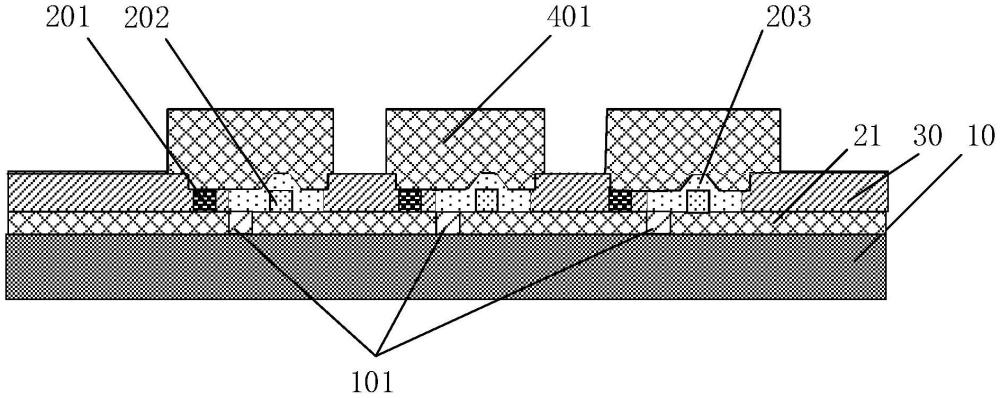

2、为解决上述技术问题,本发明实施例提供一种半导体结构,包括:

3、基板,包括若干器件区;

4、位于所述基板上的沟道层以及与所述沟道层重叠的第一电互连层、第二电互连层和第三电互连层,所述沟道层包括位于各所述器件区上的沟道结构,所述第一电互连层包括位于各所述器件区上的漏电极,所述第二电互连层包括位于各所述器件区上的源电极,所述第三电互连层包括位于各所述器件区上的栅电极,各所述沟道结构与所述漏电极和源电极电连接,且各所述沟道结构与所述栅电极相互分立;

5、位于各所述器件区上的电解质层,所述电解质层位于所述漏电极表面、所述沟道结构表面、所述源电极表面以及所述栅电极表面,不同器件区的所述电解质层之间相互隔离。

6、可选的,各所述漏电极位于所述基板上;各所述源电极与各所述栅电极位于所述漏电极上,且各所述源电极和各所述栅电极,同所述栅电极相互分立;各所述沟道结构位于对应的所述各所述源电极以及各栅电极上。

7、可选的,所述半导体结构,还包括:绝缘层和保护层,所述绝缘层位于所述漏电极与所述栅电极、所述源电极及所述沟道结构之间,且暴露出所述漏电极的表面,所述保护层位于所述绝缘层、所述栅电极、所述源电极以及所述沟道结构上,且暴露出所述漏电极、所述栅电极、所述源电极以及所述沟道结构的表面。

8、本发明实施例还提供了一种半导体结构的制作方法,包括:

9、提供基板,所述基板包括若干器件区;

10、在所述基板上形成沟道层以及与所述沟道层重叠的第一电互连层、第二电互连层和第三电互连层,所述沟道层包括位于各所述器件区上的沟道结构,所述第一电互连层包括位于各所述器件区上的漏电极,所述第二电互连层包括位于各所述器件区上的源电极,所述第三电互连层包括位于各所述器件区上的栅电极,各所述沟道结构与所述漏电极和源电极电连接,且各所述沟道结构与所述栅电极相互分立;

11、在各所述器件区上形成电解质层,所述电解质层位于所述漏电极表面、所述沟道结构表面、所述源电极表面以及所述栅电极表面,不同器件区的所述电解质层之间相互隔离。

12、可选的,在各所述器件区上形成电解质层的方法包括:

13、在所述基板上沉积光敏电解质材料;

14、在形成所述光敏电解质材料之后,对所述光敏电解质材料进行退火,得到均质光敏电解质薄膜;

15、利用图案化掩模版,对所述均质光敏电解质薄膜进行光刻,在各所述器件区上形成电解质层。

16、可选的,对所述光敏电解质材料进行退火时的温度为:40℃~90℃。

17、可选的,所述光敏电解质材料为聚乙烯醇和重氮光敏剂的混合溶液,与壳聚糖聚胺盐的水溶液等比例混合的电解质的材料。

18、可选的,所述聚乙烯醇和重氮光敏剂的混合溶液中,聚乙烯醇与重氮光敏剂的混合比例为:质量比100:1;所述壳聚糖聚胺盐的水溶液中,壳聚糖聚胺盐的浓度为:5wt%~10wt%。

19、可选的,利用图案化掩模版,对所述均质光敏电解质薄膜进行光刻时,选用的显影液为nacl盐溶液;所述nacl盐溶液的浓度为:1wt%~10wt%。

20、可选的,所述光敏电解质材料中还包括:生物电解质材料或有机电解质材料。

21、与现有技术相比,本发明实施例的技术方案具有以下有益效果:

22、本发明技术方案的半导体结构中,通过在基板的各器件区制作若干包括位于各所述器件区上的沟道结构的沟道层、以及与所述沟道层重叠的包括位于各所述器件区上的漏电极第一电互连层、包括位于各所述器件区上的源电极的第二电互连层和位于各所述器件区上的栅电极第三电互连层,并在各所述器件区上制作相互隔离的电解质层,有效回避了电解质空间相关功能,避免了对某一个器件区的器件施加栅极电压导致的周围器件的电导率也发生变化的现象,成功解决了由电解质空间相关功能引起的器件串扰问题,并实现了半导体结构内阵列的可拓展、以及阵列内器件的大密度和高均匀性配置。

23、本发明技术方案的半导体结构的制作方法中,通过在不同器件区上制作相互隔离的所述电解质层,避免了对某一个器件区的器件施加栅极电压导致的周围器件的电导率也发生变化的现象,成功解决了由电解质空间相关功能引起的器件串扰问题,并实现了半导体结构内阵列的可拓展、以及阵列内器件的大密度和高均匀性配置。

- 还没有人留言评论。精彩留言会获得点赞!