一种基于亚微米硅通孔的三维集成方法和三维集成结构

本技术涉及半导体,特别是一种基于亚微米硅通孔的三维集成方法和三维集成结构。

背景技术:

1、随着人工智能、自动驾驶和5g网络等技术的迅猛发展,各个领域对芯片算力的需求急剧增加。然而,集成电路的纳米制程工艺已接近物理极限,通过缩小晶体管尺寸来提升芯片算力变得愈发困难。在此情况下,利用芯粒(chiplet)异质集成来延续和扩展摩尔定律的重要性日益凸显,集成电路正从二维集成向三维集成发展。

2、硅通孔(tsv)作为三维集成的关键技术,能够实现多层堆叠间的最短信号连接,其重要性愈加显著。而随着三维集成电路尺寸的持续缩小和功能的不断增强,tsv技术将持续向微纳米尺度tsv演化,以实现更高的集成度、更快的数据传输速度和更低的功耗。然而,目前的tsv技术缺乏针对亚微米硅通孔的系统性的三维集成结构及对应工艺设计。因此,亟需提出一种基于亚微米硅通孔的三维集成方法和三维集成结构,以实现针对亚微米硅通孔的三维集成工艺。

技术实现思路

1、鉴于上述问题,本技术实施例提供了一种基于亚微米硅通孔的三维集成方法和三维集成结构,以便克服上述问题或者至少部分地解决上述问题。

2、本技术实施例的第一方面,提供了一种基于亚微米硅通孔的三维集成方法,所述方法包括:

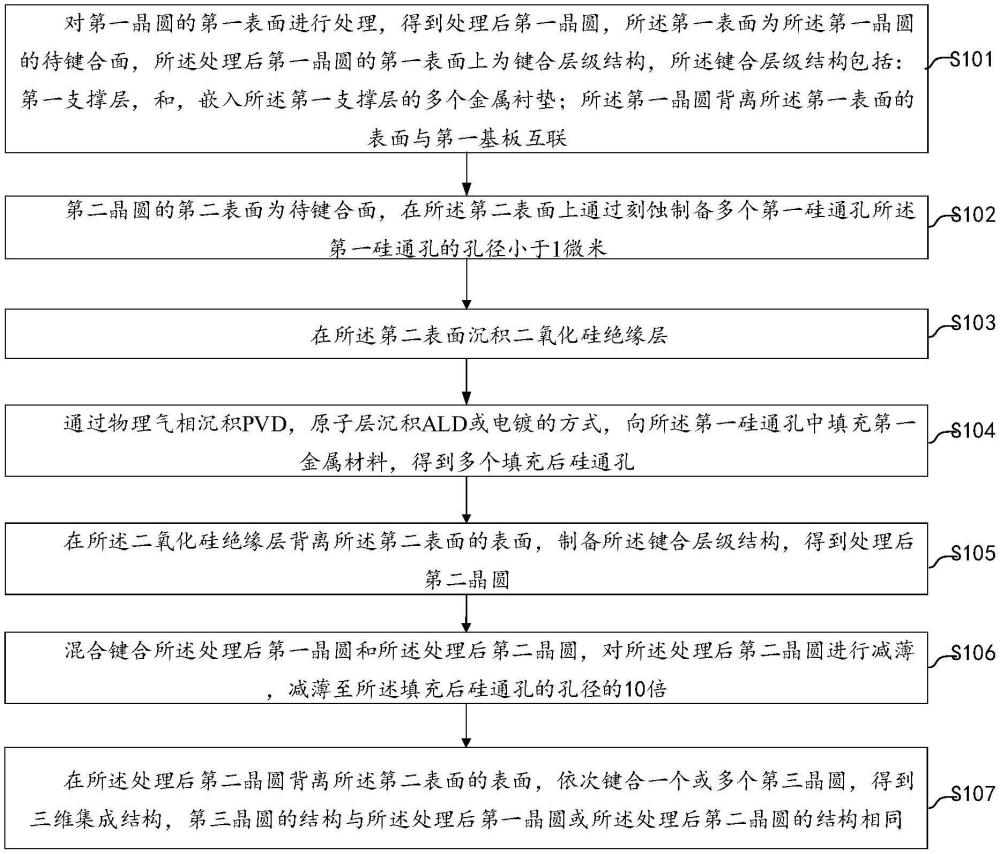

3、对第一晶圆的第一表面进行处理,得到处理后第一晶圆,所述第一表面为所述第一晶圆的待键合面,所述处理后第一晶圆的第一表面上为键合层级结构,所述键合层级结构包括:第一支撑层,和,嵌入所述第一支撑层的多个金属衬垫;所述第一晶圆背离所述第一表面的表面与第一基板互联;

4、第二晶圆的第二表面为待键合面,在所述第二表面上通过刻蚀制备多个第一硅通孔;所述第一硅通孔的孔径小于1微米;

5、在所述第二表面沉积二氧化硅绝缘层;

6、通过物理气相沉积pvd,原子层沉积ald或电镀的方式,向所述第一硅通孔中填充第一金属材料,得到多个填充后硅通孔;

7、在所述二氧化硅绝缘层背离所述第二表面的表面,制备所述键合层级结构,得到处理后第二晶圆;

8、混合键合所述处理后第一晶圆和所述处理后第二晶圆,对所述处理后第二晶圆进行减薄,减薄至所述填充后硅通孔的孔径的10倍;

9、在所述处理后第二晶圆背离所述第二表面的表面,依次键合一个或多个第三晶圆,得到三维集成结构,所述第三晶圆的结构与所述处理后第一晶圆或所述处理后第二晶圆的结构相同。

10、在一种可能的实施方式中,所述对第一晶圆的第一表面进行处理,得到处理后第一晶圆,包括:

11、在所述第一表面上通过热氧化或化学气相沉积cvd的方式制备一层以二氧化硅为材料的第一支撑层;

12、在所述第一支撑层中通过刻蚀制备多个通孔;

13、通过磁控溅射的方式,在所述第一支撑层的表面上沉积种子层;

14、通过电镀的方式,向所述通孔中填充金属铜,直至金属铜完全填充所述通孔,得到多个嵌入所述第一支撑层的所述金属衬垫;

15、通过化学机械抛光cmp的方式,去除所述第一支撑层背离所述第一表面的表面上的多余的金属材料,使所述第一支撑层的表面平整,得到所述键合层级结构。

16、在一种可能的实施方式中,所述在所述第一支撑层中通过刻蚀制备多个通孔,包括:

17、通过光刻的方式,在所述第一支撑层的表面定义再布线rdl图像和芯片线路接点位置pad;

18、根据所述rdl图像和pad,对所述第一支撑层进行等离子体刻蚀,直到暴露所述第一表面,得到多个所述通孔。

19、在一种可能的实施方式中,所述混合键合所述处理后第一晶圆和所述处理后第二晶圆,对所述处理后第二晶圆进行减薄,减薄至所述填充后硅通孔的孔径的10倍,包括:

20、使所述处理后第一晶圆的键合层级结构中嵌入的金属衬垫,与所述处理后第二晶圆的键合层级结构中嵌入的金属衬垫对准,键合所述处理后第一晶圆与所述处理后第二晶圆;

21、采用多步减薄法对所述处理后第二晶圆背离所述第二表面的表面进行减薄,减薄至所述填充后硅通孔的孔径的10倍,所述第一金属材料为钨、铜或钴。

22、在一种可能的实施方式中,所述在所述处理后第二晶圆背离所述第二表面的表面,依次键合一个或多个第三晶圆,包括:

23、将所述处理后第二晶圆背离所述第二表面的表面作为第三表面,在所述第三表面,制备所述键合层级结构;

24、在所述第三表面上的键合层级结构的表面,依次键合一个或多个第三晶圆;

25、在最后一次键合的晶圆背离键合面的表面,制备多个填充第二金属材料的第二硅通孔,使该表面与第二基板进行互联,得到三维集成结构。

26、在一种可能的实施方式中,在当前进行键合的第三晶圆不是最后一个进行键合的晶圆的情况下,该当前进行键合的第三晶圆的结构与所述处理后第二晶圆的结构相同;

27、在当前进行键合的第三晶圆是最后一个进行键合的晶圆的情况下,该当前进行键合的第三晶圆的结构与所述处理后第一晶圆或所述处理后第二晶圆的结构相同。

28、在一种可能的实施方式中,所述依次键合一个或多个第三晶圆,包括:

29、使最上层晶圆背离键合面的表面的键合层级结构中嵌入的金属衬垫,与所述第三晶圆的键合层级结构中嵌入的金属衬垫对准,键合最上层晶圆与所述第三晶圆;采用多步减薄法对所述第三晶圆进行减薄,减薄至所述第三晶圆的填充后硅通孔的孔径的10倍;

30、在所述第三晶圆背离键合面的表面,制备所述键合层级结构;

31、重复上述步骤,直至键合至最后一个第三晶圆。

32、在一种可能的实施方式中,所述二氧化硅绝缘层的厚度小于或等于50nm;所述第一支撑层的厚度为1um~5um。

33、在一种可能的实施方式中,所述第二硅通孔的孔径直径大于10um。

34、本技术实施例第二方面还提供了一种基于亚微米硅通孔的三维集成结构,所述三维集成结构由第一方面所述的基于亚微米硅通孔的三维集成方法制备得到的。

35、本技术实施例第三方面提供了一种基于亚微米硅通孔的三维集成装置,用于执行第一方面所提供的三维集成方法中的步骤,所述装置包括:

36、第一晶圆处理模块,用于对第一晶圆的第一表面进行处理,得到处理后第一晶圆,所述第一表面为所述第一晶圆的待键合面,所述处理后第一晶圆的第一表面上为键合层级结构,所述键合层级结构包括:第一支撑层,和,嵌入所述第一支撑层的多个金属衬垫;所述第一晶圆背离所述第一表面的表面与第一基板互联;

37、第二晶圆第一处理模块,用于在第二表面上通过刻蚀制备多个第一硅通孔;所述第二晶圆的第二表面为待键合面,所述第一硅通孔的孔径小于1微米;

38、第二晶圆第二处理模块,用于在所述第二表面沉积二氧化硅绝缘层;

39、第二晶圆第三处理模块,用于通过物理气相沉积pvd,原子层沉积ald或电镀的方式,向所述第一硅通孔中填充第一金属材料,得到多个填充后硅通孔;

40、第二晶圆第四处理模块,用于在所述二氧化硅绝缘层背离所述第二表面的表面,制备所述键合层级结构,得到处理后第二晶圆;

41、第一键合模块,用于混合键合所述处理后第一晶圆和所述处理后第二晶圆,对所述处理后第二晶圆进行减薄,减薄至所述填充后硅通孔的孔径的10倍;

42、第二键合模块,用于在所述处理后第二晶圆背离所述第二表面的表面,依次键合一个或多个第三晶圆,得到三维集成结构,所述第三晶圆的结构与所述处理后第一晶圆或所述处理后第二晶圆的结构相同。

43、本技术实施例提供的提供了一种基于亚微米硅通孔的三维集成方法,所述方法包括:对第一晶圆的第一表面进行处理,得到处理后第一晶圆,所述第一表面为所述第一晶圆的待键合面,所述处理后第一晶圆的第一表面上为键合层级结构,所述键合层级结构包括:第一支撑层,和,嵌入所述第一支撑层的多个金属衬垫;所述第一晶圆背离所述第一表面的表面与第一基板互联;第二晶圆的第二表面为待键合面,在所述第二表面上通过刻蚀制备多个第一硅通孔;所述第一硅通孔的孔径小于1微米;在所述第二表面沉积二氧化硅绝缘层;通过物理气相沉积pvd,原子层沉积ald或电镀的方式,向所述第一硅通孔中填充第一金属材料,得到多个填充后硅通孔;在所述二氧化硅绝缘层背离所述第二表面的表面,制备所述键合层级结构,得到处理后第二晶圆;混合键合所述处理后第一晶圆和所述处理后第二晶圆,对所述处理后第二晶圆进行减薄,减薄至所述填充后硅通孔的孔径的10倍;在所述处理后第二晶圆背离所述第二表面的表面,依次键合一个或多个第三晶圆,得到三维集成结构,所述第三晶圆的结构与所述处理后第一晶圆或所述处理后第二晶圆的结构相同。

44、本技术提供的三维集成方法,通过在第二晶圆上刻蚀孔径小于1微米的第一硅通孔,在其中填充第一金属材料的方式,制备得到亚微米级的硅通孔tsv。然后通过第一晶圆和第二晶圆上的键合层级结构实现晶圆混合键合,进而依次键合一个或多个第三晶圆(生成多层级的tsv结构),得到三维集成结构,由此实现了基于亚微米硅通孔的三维集成工艺。

45、附图说明

46、为了更清楚地说明本技术实施例的技术方案,下面将对本技术实施例的描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本技术的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动性的前提下,还可以根据这些附图获得其他的附图。

47、图1是本技术实施例提供的一种基于亚微米硅通孔的三维集成方法的步骤流程图;

48、图2是本技术实施例提供的一种三维集成方法中形成的处理后第一晶圆的结构示意图;

49、图3是本技术实施例提供的一种三维集成方法中形成的第一支撑层和通孔的结构示意图;

50、图4是本技术实施例提供的一种三维集成方法中的第二晶圆处理过程的示意图;

51、图5是本技术实施例提供的一种三维集成方法中形成的处理后第二晶圆的结构示意图;

52、图6是本技术实施例提供的一种处理后第一晶圆与处理后第二晶圆的键合结构示意图;

53、图7是本技术实施例提供的一种三维集成方法中形成的减薄后结构示意图;

54、图8是本技术实施例提供的一种三维集成方法中形成的第三表面的键合层级结构;

55、图9是本技术实施例提供的一种三维集成方法中形成的键合第三晶圆的过程示意图;

56、图10是本技术实施例提供的一种三维集成方法中的最后一次键合的晶圆的结构的示意图;

57、图11是本技术实施例提供的一种基于亚微米硅通孔的三维集成结构示意图;

58、图12是本技术实施例提供的另一种基于亚微米硅通孔的三维集成结构示意图;

- 还没有人留言评论。精彩留言会获得点赞!