一种场效应晶体管的制造方法及场效应晶体管与流程

本发明涉及半导体制造领域,具体涉及一种场效应晶体管的制造方法及场效应晶体管。

背景技术:

1、金属-氧化物半导体场效应晶体管(metal-oxide-semiconductor field-effecttransistor,mosfet)因其具有开关速度快、功耗低、栅极易驱动、驱动功率小,输入阻抗高和频率响应快等优点,被广泛的应用在各种电力系统中。在各种高电应力系统中,一方面要求功率mosfet具有更低的导通损耗,另一方面要求器件能够在高压大电流下工作更长的时间,即器件要具有高的可靠性和大的安全工作区(safe operating area,soa)。基于mosfet热不稳定性的表明,其沟道密度越大,体内寄生三极管越容易开启,从而导致电流集中,引起器件内部温度上升,造成安全工作区(soa)缩小。在相关技术中,采用虚拟元胞的结构来降低沟道密度,但这种结构极大地增加了导通电阻,造成了芯片面积的浪费。

2、因此,如何提供一种既不增加导通电阻也不增加成本,同时扩大场效应晶体管安全工作区的制造方法,是目前亟需解决的问题。

技术实现思路

1、鉴于以上所述现有技术的缺点,本发明提供一种场效应晶体管的制造方法及场效应晶体管,以解决上述技术问题中的至少之一。

2、为达到上述目的及其他相关目的,本技术提供的技术方案如下。

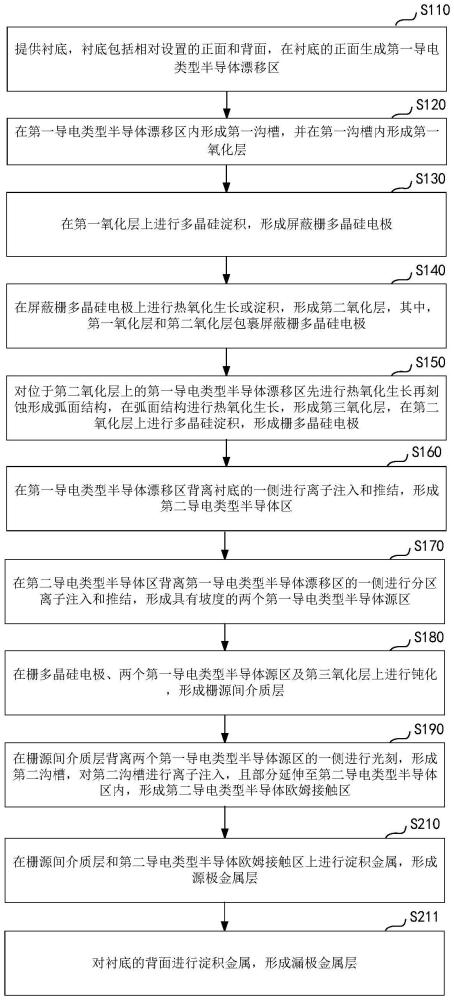

3、第一方面,本技术提供了一种场效应晶体管的制造方法,包括:

4、提供衬底,所述衬底包括相对设置的正面和背面,在所述衬底的正面生成第一导电类型半导体漂移区;

5、在所述第一导电类型半导体漂移区内形成第一沟槽,并在所述第一沟槽内形成第一氧化层;

6、在所述第一氧化层上进行多晶硅淀积,形成屏蔽栅多晶硅电极;

7、在所述屏蔽栅多晶硅电极上进行热氧化生长或淀积,形成第二氧化层,其中,所述第一氧化层和第二氧化层包裹所述屏蔽栅多晶硅电极;

8、将位于所述第二氧化层上的所述第一导电类型半导体漂移区先进行热氧化生长再刻蚀形成弧面结构,在所述弧面结构上进行热氧化生长,形成第三氧化层,在所述第二氧化层上进行多晶硅淀积,形成栅多晶硅电极;

9、在所述第二导电类型半导体区背离所述第一导电类型半导体漂移区的一侧进行分区离子注入和推结,形成具有坡度的两个第一导电类型半导体源区;

10、在所述栅多晶硅电极、两个所述第一导电类型半导体源区及所述第三氧化层上进行钝化,形成栅源间介质层;

11、在所述栅源间介质层背离两个所述第一导电类型半导体源区的一侧进行光刻,形成第二沟槽,对所述第二沟槽进行离子注入,且部分延伸至所述第二导电类型半导体区内,形成第二导电类型半导体欧姆接触区;

12、在所述栅源间介质层和所述第二导电类型半导体欧姆接触区上进行淀积金属,形成源极金属层;

13、对所述衬底的背面进行淀积金属,形成漏极金属层;

14、其中,第一个所述第一导电类型半导体源区的掺杂浓度大于第二个所述第一导电类型半导体源区的掺杂浓度,所述第一氧化层、所述第二氧化层及所述第三氧化层构成绝缘介质层。

15、于本发明的一实施例中,在所述第一导电类型半导体漂移区内形成第一沟槽,并在所述第一沟槽内形成第一氧化层,包括:在所述第一导电类型半导体漂移区上进行掩膜,生成掩膜层;对所述掩膜层进行涂布、曝光、显影,以确定所述第一沟槽的位置;对所述掩膜层和所述第一导电类型半导体漂移区进行刻蚀,得到所述第一沟槽;对所述第一沟槽进行热氧化生长,形成所述第一氧化层。

16、于本发明的一实施例中,在所述第二导电类型半导体区背离所述第一导电类型半导体漂移区的一侧进行分区离子注入和推结,形成具有坡度的两个第一导电类型半导体源区,包括:基于掩模版在所述第二导电类型半导体区上进行开窗,得到离子注入窗口;基于所述离子注入窗口对所述第二导电类型半导体区进行离子注入,形成初始导电类型半导体源区;对所述初始导电类型半导体源区进行推结,形成两个第一导电类型半导体源区。

17、于本发明的一实施例中,所述掩模版上设置有单个窗口;或者所述掩模版上设置有多个窗口,且所述多个窗口的尺寸从左至右增大或减小。

18、第二方面,本技术还提供一种场效应晶体管,该场效应晶体管根据第一方面所述描述的场效应晶体管的制造方法进行制造,包括:

19、漏极金属层以及依次堆叠在所述漏极金属层上的衬底及第一导电类型半导体漂移区;

20、所述第一导电类型半导体漂移区内设置有第一沟槽;

21、所述第一沟槽内设置有栅多晶硅电极、屏蔽栅多晶硅电极及绝缘介质层,所述绝缘介质层包裹部分所述栅多晶硅电极和所述屏蔽栅多晶硅电极,其中,所述栅多晶硅电极设置于所述屏蔽栅多晶硅电极上且通过所述绝缘介质层进行隔离;

22、在所述第一导电类型半导体漂移区背离所述衬底的一侧设置有第二导电类型半导体区;

23、在所述第二导电类型半导体区背离所述第一导电类型半导体漂移区的一侧设置有两个第一导电类型半导体源区、第二导电类型半导体欧姆接触区,其中,一部分所述第二导电类型半导体欧姆接触区介于两个所述第一导电类型半导体源区之间,一部分位于所述第二导电类型半导体区内;

24、两个所述第一导电类型半导体源区、所述栅多晶硅电极及部分所述绝缘介质层上设置有栅源间介质层;

25、所述第二导电类型半导体欧姆接触区和所述栅源间介质层上设置有源极金属层。

26、于本发明的一实施例中,所述屏蔽栅多晶硅电极在水平方向上通过所述绝缘介质层与所述第一导电类型半导体漂移区进行隔离;所述栅多晶硅电极通过所述绝缘介质层与部分所述第一导电类型半导体漂移区、部分所述第二导电类型半导体区及两个所述第一导电类型半导体源区进行隔离,其中所述水平方向为平行于所述漏极金属层的方向。

27、于本发明的一实施例中,所述第二导电类型半导体欧姆接触区上的所述源极金属层在所述水平方向上,一部分介于两个所述第一导电类型半导体源区之间,一部分介于所述栅源间介质层之间。

28、于本发明的一实施例中,两个所述第一导电类型半导体源区与所述第二导电类型半导体区的接触面具有坡度,第一个所述第一导电类型半导体源区的掺杂浓度大于第二个所述第一导电类型半导体源区的掺杂浓度。

29、第三方面,本技术还提供一种场效应晶体管的制造方法,包括:

30、提供衬底,所述衬底包括相对设置的正面和背面,在所述衬底的正面生成第一导电类型半导体漂移区;

31、在所述第一导电类型半导体漂移区内形成具有弧面结构的第三沟槽,并在所述第三沟槽内形成绝缘介质层;

32、在所述绝缘介质层上进行多晶硅淀积,形成栅多晶硅电极;

33、在所述第一导电类型半导体漂移区背离所述衬底的一侧进行离子注入和推结,形成第二导电类型半导体区;

34、在所述第二导电类型半导体区背离所述第一导电类型半导体漂移区的一侧进行分区离子注入和推结,形成具有坡度的两个第一导电类型半导体源区;

35、在所述栅多晶硅电极、两个所述第一导电类型半导体源区及部分所述绝缘介质层上进行钝化,形成栅源间介质层;

36、在所述栅源间介质层背离两个所述第一导电类型半导体源区的一侧进行光刻,形成第二沟槽,对所述第二沟槽进行离子注入,且部分延伸至所述第二导电类型半导体区内,形成第二导电类型半导体欧姆接触区;

37、在所述栅源间介质层和所述第二导电类型半导体欧姆接触区上进行淀积金属,形成源极金属层;

38、对所述衬底的背面进行淀积金属,形成漏极金属层;

39、其中,第一个所述第一导电类型半导体源区的掺杂浓度大于第二个所述第一导电类型半导体源区的掺杂浓度。

40、第四方面,本技术还提供一种场效应晶体管,该场效应晶体管根据第三方面所述描述的场效应晶体管的制造方法进行制造,包括:

41、漏极金属层以及依次堆叠在所述漏极金属层上的衬底及第一导电类型半导体漂移区;

42、所述第一导电类型半导体漂移区内设置有第三沟槽,其中所述第三沟槽的底部与侧壁之间形成所述弧面结构;

43、所述第三沟槽内设置有栅多晶硅电极及绝缘介质层,所述绝缘介质层包裹部分所述栅多晶硅电极;

44、在所述第一导电类型半导体漂移区背离所述衬底的一侧设置有第二导电类型半导体区;

45、在所述第二导电类型半导体区背离所述第一导电类型半导体漂移区的一侧设置有两个第一导电类型半导体源区、第二导电类型半导体欧姆接触区,其中,一部分所述第二导电类型半导体欧姆接触区介于两个所述第一导电类型半导体源区之间,一部分位于所述第二导电类型半导体区内;

46、两个所述第一导电类型半导体源区、所述栅多晶硅电极及部分所述绝缘介质层上设置有栅源间介质层;

47、所述第二导电类型半导体欧姆接触区和所述栅源间介质层上设置有源极金属层。

48、本技术提供一种场效应晶体管的制造方法及场效应晶体管,该制造方法通过离子注入的方式形成第一导电类型半导体源区和第一导电类型半导体源区时,不增加场效应晶体管的造成工艺和成本,使得第一导电类型半导体源区和第一导电类型半导体源区的掺杂浓度不同,因场效应晶体管的沟道密度降低,有效降低了寄生三极管的基极压降,减少寄生三极管开启的风险,增强了场效应晶体管的抗热不稳定性和安全工作区,与具有虚拟元胞的器件相比,其导通电阻明显减小。

49、应当理解的是,以上的一般描述和后文的细节描述仅是示例性和解释性的,并不能限制本发明。

- 还没有人留言评论。精彩留言会获得点赞!