一种用于高压集成电路ESD保护触发电压和维持电压可调型的多通道SCR器件

本发明属高压集成电路(integrated circuits,简称ic)的静电放电(electrostatic discharge,简称esd)保护器件设计领域,具体涉及一种esd保护结构器件,尤指一种改进型横向硅控整流器(modified lateral silicon controlledrectifier,简称mlscr)。

背景技术:

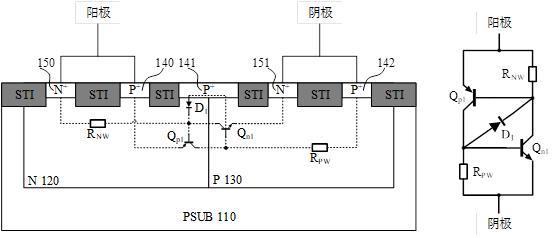

1、esd指两个不同静电电位的物体之间相互接触发生电荷转移的现象,是造成电子元件和ic损坏的主要原因之一。esd破坏具有隐蔽性、潜伏性、随机性和复杂性等特点,随着半导体工艺技术的发展,其导致的ic故障和损坏已经成为日益严重的问题,因此对ic芯片的esd保护方案研究十分重要。

2、在特定的半导体工艺中,esd保护器件在工作时需要满足一定的esd设计窗口,即器件的安全工作范围应该小于被保护电路的最小击穿电压,且大于被保护电路的工作电压。对于有回滞特性的esd保护器件而言,触发电压和维持电压的大小应该在esd设计窗口之内。在高压集成电路的esd保护器件设计当中,esd保护器件的维持电压和触发电压需要满足较高工作电压的需求。esd保护器件在满足合适的设计窗口的同时具有高鲁棒性的特点一直是esd保护器件设计的重点与难点。因此,设计具有可调的触发电压和维持电压、强抗闩锁能力和高鲁棒性等特点的esd保护器件,其意义非凡。

3、有一种传统的带有回滞特性的esd保护器件mlscr,其具有高鲁棒性、结构简单、高面积利用率等特点,很适合用于芯片中的 esd保护。该器件结构如图1所示,包括:

4、p型衬底110,所述p型衬底110上形成第一n型掺杂区120和第一p型掺杂区130;所述第一n型掺杂区与第一p型掺杂区水平相切;

5、在所述第一n型掺杂区120中以第一p型掺杂区130为参考从近往远依次设有第一p型重掺杂区140和第一n型重掺杂150;所述第一n型掺杂区120和所述第一p型掺杂区130之间设有一个横跨两区的第二p型重掺杂区141;在所述第一p型掺杂区130中以第一n型掺杂区120为参考从近往远依次设有第二n型重掺杂区151和第三p型重掺杂区142;

6、所述第一n型重掺杂区150和第一p型重掺杂区140与阳极相连;所述第二n型重掺杂区151和第三p型重掺杂区142与阴极相连;

7、所述第一n型重掺杂区150和第一p型重掺杂区140之间、第一p型重掺杂区140和第二p型重掺杂区141之间、第二p型重掺杂区141和第二n型重掺杂区151之间、第二n型重掺杂区151和第三n型重掺杂区142之间均分别设有浅沟槽隔离。

8、所述器件有一个寄生pnp晶体管、一个寄生npn晶体管、一个寄生反向二极管、两个阱电阻:

9、所述第一寄生pnp晶体管qp1,包括第一p型重掺杂区140、第一n型掺杂区120、第一p型掺杂区130;所述第一寄生npn晶体管qn1,包括第一n型掺杂区120、第一p型掺杂区130、第二n型重掺杂区151;所述第一寄生反向二极管d1,包括第一n型掺杂区120、第二p型重掺杂区141;所述第一阱电阻rnw,包括第一n型掺杂区120阱电阻;所述第二阱电阻rpw,包括第一p型掺杂区130阱电阻。

10、所述器件工作原理:

11、esd事件到达所述器件阳极,esd电压大于所述器件d1的击穿电压时,将会有电流流经rnw、d1、rpw,即电流从阳极到阴极依次流过第一n型重掺杂区150、第一n型掺杂区120、第二p型重掺杂区141、第一p型掺杂区130、第三p型重掺杂区142。随着电流的增大, rnw和rpw的压降增大,使得qn1和qp1开启。qn1和qp1集电极电流的增大,在rnw和rpw上的压降继续增加,qn1和qp1的发射结电压增大,在寄生npn晶体管和寄生pnp晶体管之间耦合形成正反馈,至此scr通道导通。

12、所述传统mlscr通过寄生反向二极管d1的击穿电压能够有效控制触发电压,但是其主要泄放esd电流的方式仍是通过scr通道。scr通道虽然拥有很强的esd电流泄放能力,但由于其两个双极型晶体管之间的正反馈作用,scr通道的维持电压在1.5v左右,该维持电压不能满足高压集成电路的esd保护设计的需求,容易发生闩锁现象,使该器件无法关断并影响电路正常工作,严重时会造成芯片损坏。

13、因此,本发明提出一种能够调控触发电压和维持电压的mlscr器件,该器件拥有更多的触发通道和更多的esd电流泄放通道。不同的触发通道能够对触发电压进行调整,不同的esd电流泄放通道能够对维持电压进行调整,进而使其适用于多种高压电源域下的集成电路esd保护。此外,其多通道的特性同样使其拥有高鲁棒性和高面积利用率等特点。

技术实现思路

1、本发明的目的在于提出一种用于高压集成电路esd保护触发电压和维持电压可调型的多通道scr器件,该器件具有可调的触发电压和维持电压、强抗闩锁能力和高鲁棒性等特点,可适用于多种电源域下的高压集成电路esd保护。本发明采用的技术方案为:

2、一种触发电压和维持电压可调型的多通道mlscr器件,包括:

3、所述器件包括p型硅衬底,所述p型硅衬底上形成第一n型掺杂区;所述第一n型掺杂区上形成第二n型掺杂区、第三n型掺杂区、第一p型掺杂区;所述第一p型掺杂区被第一n型掺杂区、第二n型掺杂区、第三n型掺杂区全包围;

4、所述第二n型掺杂区设有第一p型重掺杂区;所述第二n型掺杂区和第一p型掺杂区之间设有一个横跨两区的第二p型重掺杂区;在所述第一p型掺杂区中以第二p型重掺杂区为参考从近往远依次设有第三p型重掺杂区和第一n型重掺杂区;所述第三n型掺杂区设有第二n型重掺杂区;

5、所述第一p型重掺杂区和第二n型重掺杂区与阳极相连;所述第三p型重掺杂区和第一n型重掺杂区与阴极相连;

6、所述第二p型重掺杂区和第三p型重掺杂区之间、第三p型重掺杂区和第一n型重掺杂区之间、第一n型重掺杂区和第二n型重掺杂区之间均分别设有浅沟槽隔离;

7、所述第一p型掺杂区由一个或多个掺杂剂量不同的p型掺杂区纵向叠加而成,所述第一n型掺杂区、第二n型掺杂区、第三n型掺杂区由一个或多个掺杂剂量不同的n型掺杂区纵向叠加而成。

8、所述器件有两个寄生pnp晶体管、三个寄生npn晶体管、三个阱电阻:

9、所述第一寄生pnp晶体管,包括第一p型重掺杂区、第二n型掺杂区、第二p型重掺杂区、第一p型掺杂区、第三p型重掺杂区;所述第二寄生pnp晶体管,包括第一p型重掺杂区、第二n型掺杂区、第一p型掺杂区;所述第一寄生npn晶体管,包括第二n型重掺杂区、第三n型掺杂区、第一p型掺杂区、第一n型重掺杂区;所述第二寄生横向npn晶体管,包括第二n型掺杂区、第一p型掺杂区、第一n型重掺杂区;所述第三寄生纵向npn晶体管,包括第一n型掺杂区、第一p型掺杂区、第一n型重掺杂区;所述第一阱电阻,包括第一p型阱区阱电阻;所述第二阱电阻,包括以第一n型重掺杂区为参考在第一n型掺杂区中靠近第三n型掺杂区的阱电阻和第三n型掺杂区阱电阻;所述第三阱电阻,包括以第一n型重掺杂区为参考在第一n型掺杂区中靠近第二n型掺杂区的阱电阻和第二n型掺杂区阱电阻。

10、由第一寄生pnp晶体管组成pnp通道;由第一寄生npn晶体管组成npn通道;由第二寄生pnp晶体管、第二寄生横向npn晶体管、第三寄生纵向npn晶体管、第一阱电阻、第二阱电阻、第三阱电阻共同组成scr通道。

11、本发明提供一种用于高压集成电路esd保护触发电压和维持电压可调型的多通道scr器件,所述器件除了继承了传统mlscr器件的高鲁棒性、结构简单、面积利用率高等特点,还具有可调的触发电压和维持电压及强抗闩锁能力等优点。与传统mlscr器件相比,优化了所述器件的触发方式,由pnp通道或npn通道触发,其触发电压可调性可通过调控第一寄生pnp晶体管和第一寄生npn晶体管的bvceo(双极型晶体管共发射极集电结雪崩穿电压)来实现;所述器件的主要esd泄放路径为pnp通路和scr通路,可通过调控pnp通道和scr通道的电流大小之比来调整维持电压,以此避免闩锁效应的发生,并使该器件适用于不同的esd设计窗口。

12、一种优化的触发电压和维持电压可调型的多通道mlscr器件,包括:

13、所述器件包括p型硅衬底,所述p型硅衬底上形成第一n型掺杂区;所述第一n型掺杂区上形成第二n型掺杂区、第三n型掺杂区、第一p型掺杂区;所述第一p型掺杂区被第一n型掺杂区、第二n型掺杂区、第三n型掺杂区全包围;

14、所述第二n型掺杂区设有第一p型重掺杂区;所述第二n型掺杂区和第一p型掺杂区之间设有一个横跨两区的第二p型重掺杂区;在所述第一p型掺杂区中以第二p型重掺杂区为参考从近往远依次设有第三p型重掺杂区和第一n型重掺杂区;所述第三n型掺杂区和第一p型掺杂区之间设有一个横跨两区的第四p型重掺杂区;所述第三n型掺杂区设有第二n型重掺杂区;

15、所述第一p型重掺杂区和第二n型重掺杂区与阳极相连;所述第三p型重掺杂区和第一n型重掺杂区与阴极相连;

16、所述第二p型重掺杂区和第三p型重掺杂区之间、第三p型重掺杂区和第一n型重掺杂区之间、第一n型重掺杂区和第四p型重掺杂区之间均分别设有浅沟槽隔离。

17、所述第一p型掺杂区由一个或多个掺杂剂量不同的p型掺杂区纵向叠加而成,所述第一n型掺杂区、第二n型掺杂区、第三n型掺杂区由一个或多个掺杂剂量不同的n型掺杂区纵向叠加而成。

18、所述器件有两个寄生pnp晶体管、三个寄生npn晶体管、三个阱电阻:

19、所述第一寄生pnp晶体管,包括第一p型重掺杂区、第二n型掺杂区、第二p型重掺杂区、第一p型掺杂区、第三p型重掺杂区;所述第二寄生pnp晶体管,包括第一p型重掺杂区、第二n型掺杂区、第一p型掺杂区;所述第一寄生npn晶体管,包括第二n型重掺杂区、第三n型掺杂区、第四p型重掺杂区、第一p型掺杂区、第一n型重掺杂区;所述第二寄生横向npn晶体管,包括第二n型掺杂区、第一p型掺杂区、第一n型重掺杂区;所述第三寄生纵向npn晶体管,包括第一n型掺杂区、第一p型掺杂区、第一n型重掺杂区;所述第一阱电阻,包括第一p型阱区阱电阻;所述第二阱电阻,包括以第一n型重掺杂区为参考在第一n型掺杂区中靠近第三n型掺杂区的阱电阻和第三n型掺杂区阱电阻;所述第三阱电阻,包括以第一n型重掺杂区为参考在第一n型掺杂区中靠近第二n型掺杂区的阱电阻和第二n型掺杂区阱电阻。

20、由第一寄生pnp晶体管组成pnp通道;由第一寄生npn晶体管组成npn通道;由第二寄生pnp晶体管、第二寄生npn横向晶体管、第三寄生纵向npn晶体管、第一阱电阻、第二阱电阻、第三阱电阻共同组成scr通道。

21、本发明提供一种优化的用于高压集成电路esd保护触发电压和维持电压可调型的多通道scr器件,所述器件除了拥有可调的触发电压和维持电压及强抗闩锁能力等特点外,主要对触发通道进行了优化。所述器件由pnp通道或npn通道触发,其触发电压可调性可通过调控第一寄生pnp晶体管和第一寄生npn晶体管的bvceo来实现;所述器件的主要esd泄放路径为pnp通路和scr通路,可通过调控pnp通道和scr通道的电流大小之比来调整维持电压,以此避免闩锁效应的发生,并使该器件适用于不同的esd设计窗口。相比于优化前的器件,所述优化器件的第一寄生pnp晶体管和第一寄生npn晶体管从结构上更相似,因此二者的bvceo更接近,使器件的触发电压更稳定。

- 还没有人留言评论。精彩留言会获得点赞!