一种高可靠性的通孔型垂直LED芯片及其制作方法与流程

本发明涉及发光二极管,更为具体地说,涉及一种高可靠性的通孔型垂直led芯片及其制作方法。

背景技术:

1、现有的发光二极管包括水平类型和垂直类型。垂直类型的发光二极管通过把半导体结构转移到其它的导电性、导热性更佳的基板上,并移除原始外延生长的衬底的工艺获得,半导体结构至少包括依次层叠的第一型半导体层、有源区及第二型半导体层,第一型半导体层和第二型半导体层的掺杂类型相反,第一型半导体层可以是p型半导体层也可以是n型半导体层。相较于水平类型,可以有效改善外延生长衬底带来的吸光、电流拥挤或散热性差的技术问题。衬底的转移一般采用键合工艺,键合主要通过金属-金属高温高压键合,即在半导体结构的一侧与导电基板之间形成金属键合层。半导体结构的另一侧作为出光侧,出光侧配置有打线电极以提供电流的注入或流出,半导体结构下方的导电基板提供电流的流出或流入,由此形成电流垂直经过半导体结构的发光二极管。

2、现有的通孔型垂直结构led芯片,在形成切割道时半导体结构侧壁会直接裸露pn结,在通过切割道实现led芯片器件的物理分离时,半导体结构侧壁会有钝化层进行保护用来提高可靠性,然而,还是会出现led芯片侧壁漏电的情况,如图1所示,led芯片在通过emmi(微光显微镜)进行漏电检测时,如虚线框内所示漏电点皆在芯粒的侧壁,如图2所示,在emmi的另外一种显示模式下,虚线框内的漏电点更为明显,侧壁漏电会严重影响led芯片的可靠性和稳定性,从而导致led芯片良率降低。

技术实现思路

1、有鉴于此,本发明提供一种高可靠性的通孔型垂直led芯片及其制作方法,以解决现有技术中通孔型垂直led芯片出现侧壁漏电等情况,影响led芯片的可靠性和稳定性。

2、为实现上述目的,本发明采用的技术方案如下:

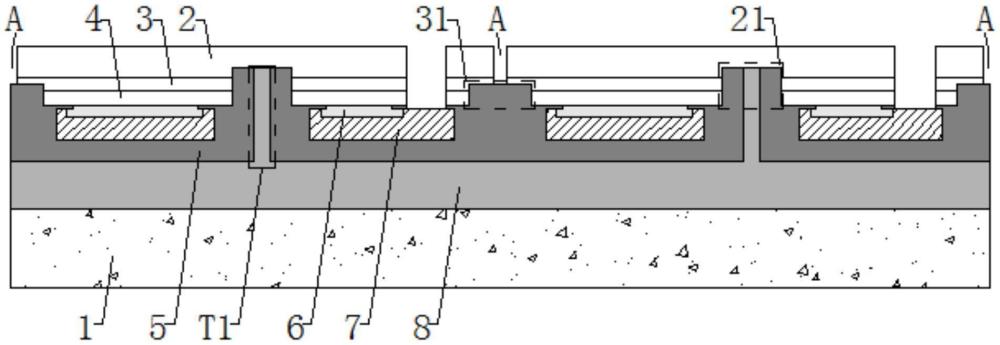

3、一种高可靠性的通孔型垂直led芯片,其特征在于,包括:

4、导电基板;

5、设置于所述导电基板一侧的金属键合层、绝缘结构、集成金属层、欧姆反射层以及外延叠层;所述外延叠层至少包括沿第一方向依次堆叠的第二型半导体层、有源区以及第一型半导体层,其中,所述外延叠层朝向所述导电基板的一侧设有显露所述有源区部分表面的沟道;

6、在各所述沟道之间的所述外延叠层朝向所述导电基板的一侧设有显露所述第一型半导体层部分表面的凹槽,所述第一方向垂直于所述导电基板,并由所述导电基板指向所述外延叠层;

7、所述欧姆反射层层叠于所述第二型半导体层背离所述有源区的一侧表面;

8、所述集成金属层覆盖所述欧姆反射层的裸露面,且所述集成金属层朝向所述外延叠层的一侧具有裸露面以用于外部电连接;

9、所述绝缘结构设置于所述外延叠层朝向所述导电基板的一侧,并覆盖所述沟道、所述集成金属层及所述外延叠层的裸露面,且延伸至所述凹槽的侧壁;图形化所述绝缘结构形成裸露所述凹槽的部分底部的第一通孔;

10、所述金属键合层层叠于所述绝缘结构背离所述外延叠层的一侧表面,并填充所述第一通孔与所述第一型半导体层形成电连接;所述导电基板层叠于所述金属键合层背离所述外延叠层的一侧表面;

11、且,位于所述沟道的绝缘结构在背离所述导电基板的一侧表面具有用于作为切割道的裸露面,所述外延叠层通过所述切割道形成相互间隔排布的若干个子外延叠层。

12、优选地,所述图形化所述绝缘结构还形成裸露所述沟道的部分底部的第二通孔,所述金属键合层填充所述第二通孔,所述切割道显露所述第二通孔内的部分金属键合层,以使所述绝缘结构不在所述切割道的垂直投影范围内。

13、优选地,在所述切割道与各子外延叠层之间设置围坝,且所述围坝通过隔离槽与对应的子外延叠层间隔,所述隔离槽裸露部分所述绝缘结构的表面,所述围坝围绕对应的所述子外延叠层。

14、优选地,所述绝缘结构包括介质膜层和绝缘保护层,所述介质膜层设置于所述第二型半导体层的部分表面,并延伸至所述凹槽的侧壁、所述凹槽的部分底部、所述沟道的侧壁及所述沟道的部分底部,且所述介质膜层包括介质通孔,所述介质通孔显露部分所述第二型半导体层,所述欧姆反射层通过所述介质通孔与所述第二型半导体层形成电连接;

15、所述绝缘保护层覆盖所述集成金属层及各子外延叠层朝向所述导电基板一侧的裸露面。

16、优选地,在所述凹槽和所述沟道的转角处的介质膜层表面设置缓冲金属,且所述缓冲金属通过所述绝缘保护层与所述集成金属层、所述金属键合层间隔设置。

17、本发明还提供了一种高可靠性的通孔型垂直led芯片的制作方法,其特征在于,所述制作方法包括以下步骤:

18、步骤s01、提供一生长衬底,在所述生长衬底的一侧表面形成外延叠层,所述外延叠层包括沿生长方向依次堆叠的第一型半导体层、有源区及第二型半导体层;

19、步骤s02、通过刻蚀所述外延叠层至所述有源区部分表面形成沟道,同时在各所述沟道之间刻蚀所述外延叠层至所述第一型半导体层部分表面形成凹槽;

20、步骤s03、制备绝缘结构,使其覆盖所述凹槽、所述沟道及部分所述第二型半导体层;

21、步骤s04、制备欧姆反射层,使其覆盖裸露的所述第二型半导体层;

22、步骤s05、制备集成金属层,使其覆盖欧姆反射层的裸露面;

23、步骤s06、再次沉积整面所述绝缘结构,使其覆盖所述集成金属层及所述外延叠层的裸露面,并图形化所述绝缘结构使其裸露所述凹槽的部分底部形成第一通孔;

24、步骤s07、蒸镀金属键合层,所述金属键合层层叠于所述绝缘结构背离所述外延叠层的一侧表面,并填充所述第一通孔与所述第一型半导体层形成连接;

25、步骤s08、通过键合工艺,将步骤s07所形成的芯片结构固定于导电基板,且所述导电基板形成于所述金属键合层背离所述外延叠层的一侧表面;

26、步骤s09、剥离所述生长衬底,露出所述第一型半导体层;

27、步骤s10、在所述外延叠层背离所述导电基板的一侧刻蚀,以使位于所述沟道的绝缘结构具有用于作为切割道的裸露面,所述外延叠层通过所述切割道形成相互间隔排布的若干个子外延叠层;

28、同时,蚀刻各所述子外延叠层,形成具有通过裸露所述集成金属层的部分表面而用于外部电连接的开口。

29、优选地,所述图形化所述绝缘结构还形成裸露所述沟道的部分底部的第二通孔,所述金属键合层填充所述第二通孔,所述切割道显露所述第二通孔内的部分金属键合层,以使所述绝缘结构不在所述切割道的垂直投影范围内。

30、优选地,通过刻蚀所述切割道与各子外延叠层之间的部分所述外延叠层,在所述切割道与各子外延叠层之间形成围坝,且所述围坝通过隔离槽与对应的子外延叠层间隔,所述隔离槽裸露部分所述绝缘结构的表面,所述围坝围绕对应的所述子外延叠层。

31、优选地,所述绝缘结构包括介质膜层和绝缘保护层,所述介质膜层设置于所述第二型半导体层的部分表面,并延伸至所述凹槽的侧壁、所述凹槽的部分底部、所述沟道的侧壁及所述沟道的部分底部,且所述介质膜层包括介质通孔,所述介质通孔显露部分所述第二型半导体层,所述欧姆反射层通过所述介质通孔与所述第二型半导体层形成电连接;

32、所述绝缘保护层覆盖所述集成金属层及各子外延叠层朝向所述导电基板一侧的裸露面。

33、优选地,在所述凹槽和所述沟道的转角处的介质膜层表面设置缓冲金属,且所述缓冲金属通过所述绝缘保护层与所述集成金属层、所述金属键合层间隔设置。

34、经由上述的技术方案,从而达到如下效果:

35、1、本发明所提供的一种高可靠性的通孔型垂直led芯片,通过在导电基板一侧设置金属键合层、绝缘结构、集成金属层、欧姆反射层以及外延叠层;其中,外延叠层朝向导电基板的一侧设有显露有源区部分表面的沟道,绝缘结构设置于外延叠层朝向导电基板的一侧,并覆盖沟道、集成金属层及外延叠层的裸露面,通过绝缘结构对沟道进行绝缘,即,对沟道显露的有源区和第二型半导体层进行绝缘,可避免led芯片在形成切割道时侧壁直接裸露pn结被短路造成侧壁漏电的风险,进而提高led芯片可靠性和稳定性。

36、2、进一步地,图形化绝缘结构还形成裸露沟道的部分底部的第二通孔,金属键合层填充第二通孔,切割道显露第二通孔内的部分金属键合层,以使绝缘结构不在切割道的垂直投影范围内,避免在通过切割道实现led芯片器件的物理分离时,因绝缘结构为脆性材质,受切割应力影响出现脱落和断裂的情况,还能让切割面不显露绝缘结构,避免绝缘结构被外界尖锐物品破坏,造成led芯片的漏电,影响led芯片的可靠性和稳定性。

37、3、进一步地,在切割道与各子外延叠层之间设置围坝,通过设置围坝可在通过切割道实现led芯片器件的物理分离时,避免因切割应力影响,相邻的芯片碰撞在一起,造成led芯片崩边崩角的问题,且围坝还可作为切割定位点避免切割切偏,可提高led芯片的可靠性和稳定性。

38、4、进一步地,在凹槽和沟道的转角处的介质膜层表面设置缓冲金属,可使凹槽和沟道的转角处的介质膜层在受到应力时得到缓冲,避免受应力影响造成断裂的情况,比如键合工艺或切割工艺的应力,且缓冲金属通过绝缘保护层与集成金属层、金属键合层间隔设置,可使缓冲金属不导电,避免电流传导至凹槽和沟道的侧壁,而影响led芯片的可靠性和稳定性。

39、5、本发明所提供的一种高可靠性的通孔型垂直led芯片的制作方法,在实现上述led芯片的有益效果的同时,其工艺制作简单、便捷,便于生产化。

- 还没有人留言评论。精彩留言会获得点赞!