半导体结构及其制作方法、半导体器件与流程

本发明涉及半导体,尤其涉及一种半导体结构及其制作方法、半导体器件。

背景技术:

1、随着半导体器件的尺寸越做越小,集成度越来越高,高密度的三维集成芯片结构成为重要研究方向,并通过硅通孔(through glass via,tsv)技术实现多个集成芯片的电性连接。然而,在tsv中填充铜的工艺过程中,由于铜的热膨胀系数远大于硅,会产生较大的热应力,影响芯片的结构和多个芯片之间的电连接性能。

技术实现思路

1、有鉴于此,本技术实施例为解决背景技术中存在的至少一个问题而提供一种半导体结构及其制作方法、半导体器件,能够降低半导体结构中硅第一凹槽周边的应力,提高半导体结构的良率和电连接性能,且工艺步骤简单。

2、为达到上述目的,本技术的技术方案是这样实现的:

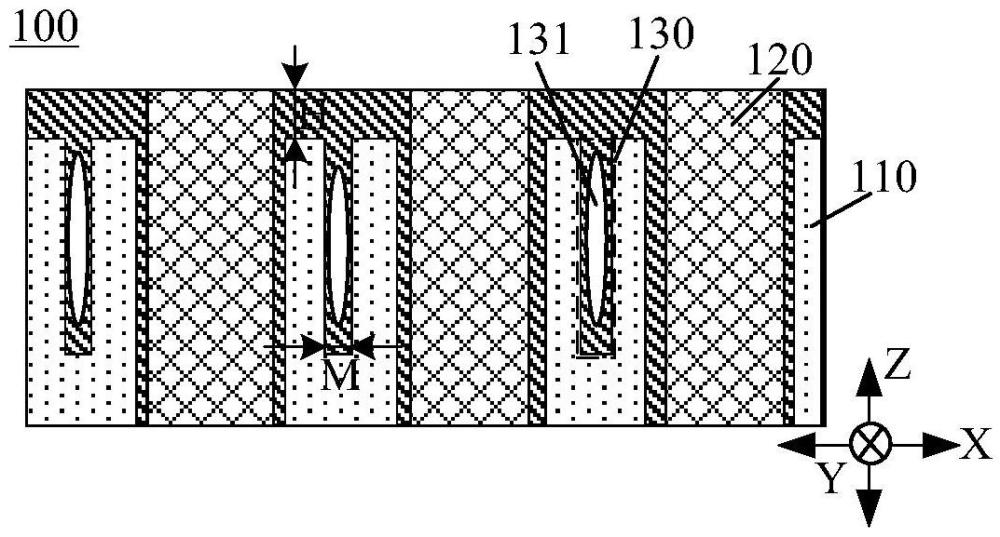

3、一方面,本技术实施例提供了一种半导体结构。所述半导体结构包括:半导体基板,导电柱和应力消除结构。导电柱设置于所述半导体基板内。应力消除结构设置于所述导电柱沿垂直于所述半导体基板厚度方向的至少一侧,;所述应力消除结构包括空腔。

4、在一些示例中,所述应力消除结构的数量包括多个;多个所述应力消除结构沿围绕所述导电柱的方向间隔设置。

5、在一些示例中,所述应力消除结构的数量包括多个。多个所述应力消除结构中每相邻两个所述应力消除结构之间的间距相等;和/或,至少两个所述应力消除结构分别与同一个所述导电柱之间的间距相等。

6、在一些示例中,不同的所述应力消除结构与同一个所述导电柱之间的间距包括第一间距和第二间距;所述第一间距小于所述第二间距。与所述导电柱间隔所述第一间距的所述应力消除结构的所述空腔的体积,大于或等于与所述导电柱间隔所述第二间距的所述应力消除结构的所述空腔的体积。

7、在一些示例中,沿所述半导体基板的厚度方向,与所述导电柱间隔所述第一间距的所述应力消除结构的尺寸,大于或等于与所述导电柱间隔所述第二间距的所述应力消除结构的尺寸。所述应力消除结构沿所述半导体基板的厚度方向的最大尺寸小于所述半导体基板的厚度。

8、在一些示例中,沿垂直于所述半导体基板的厚度方向,与所述导电柱间隔所述第一间距的所述应力消除结构的截面图形的尺寸,大于或等于与所述导电柱间隔所述第二间距的所述应力消除结构的截面图形的尺寸。且所述应力消除结构沿垂直于所述半导体基板的厚度方向的截面图形的最大尺寸,为所述导电柱沿垂直于所述半导体基板的厚度方向的截面图形的尺寸的1/12~1/8。

9、在一些示例中,沿多个所述导电柱的排列方向,相邻两个所述导电柱之间设置至少一列所述应力消除结构,所述一列所述应力消除结构的排列方向与所述相邻两个所述导电柱的排列方向交叉。

10、在一些示例中,所述应力消除结构沿垂直于所述半导体基板的厚度方向的截面形状包括圆形、矩形和弧形中的至少一种。围绕同一个所述导电柱的多个所述应力消除结构,沿垂直于所述半导体基板的厚度方向的截面形状可不同。

11、在一些示例中,所述应力消除结构包括介质层和所述介质层围成的所述空腔。所述介质层的厚度,大于所述应力消除结构沿垂直于所述半导体基板厚度方向的截面形状的尺寸,且两者的差值大于或等于所述应力消除结构沿垂直于所述半导体基板厚度方向的截面形状的最小尺寸的1/5。

12、上述设置在导电柱周围的具有空腔的应力消除结构,空腔的结构属性能够提供一定程度的弹性形变量,且有利于吸收部分热量,从而能够降低因导电柱材料与半导体基板的材料之间的膨胀系数的差异导致的热应力作用,降低导电柱因热应力等因素发生形变的不良影响,提高导电柱的结构稳定性。并且,应力消除结构是一个封闭的实体结构(不是一个开口的凹槽),空腔是位于应力消除结构内部的,在应力消除结构吸收应力作用的情况下,相较于开口的凹槽类型的结构,封闭的应力消除结构通过空腔吸收应力,应力消除结构整体表征的形变程度较小且结构更稳定,有利于提高形成的导电柱的结构稳定性和精度,有利于提高半导体基板的稳定性,进而提高通过导电柱实现不同的半导体结构电性连接的稳定性。

13、另一方面,本技术实施例提供了一种半导体结构的制作方法。所述制作方法包括:提供半导体基板。在所述半导体基板上形成第一凹槽和位于所述第一凹槽至少一侧的第二凹槽;所述第二凹槽的开口的尺寸小于所述第一凹槽的开口尺寸。在所述半导体基板上形成介质层;所述介质层的材料部分填充于所述第二凹槽内,且覆盖所述第二凹槽的开口,在所述第二凹槽内形成具有空腔的应力消除结构。

14、在一些示例中,所述在所述半导体基板上形成介质层,包括:采用沉积工艺形成介质层,所述介质层的部分材料位于所述第一凹槽的侧壁,形成阻挡层。其中,所述介质层的厚度大于所述第二凹槽的开口的尺寸,且两者的差值大于或等于所述第二凹槽的开口的最小尺寸的1/5。

15、在一些示例中,所述在所述半导体基板上形成第一凹槽和位于所述第一凹槽至少一侧的第二凹槽,包括:沿围绕所述第一凹槽的方向,间隔形成多个所述第二凹槽。多个所述第二凹槽中每相邻两个所述第二凹槽之间的间距相等;和/或,至少两个所述第二凹槽分别与同一个所述第一凹槽之间的间距相等。

16、在一些示例中,所述在所述半导体基板上形成第一凹槽和位于所述第一凹槽至少一侧的第二凹槽,包括:在与所述第一凹槽间隔第一间距的区域形成部分所述第二凹槽。在与所述第一凹槽间隔第二间距的区域形成部分所述第二凹槽;所述第一间距小于所述第二间距。

17、其中,与所述第一凹槽间隔所述第一间距的所述第二凹槽的深度,大于或等于与所述第一凹槽间隔所述第二间距的所述第二凹槽的深度;和/或,与所述第一凹槽间隔所述第一间距的所述第二凹槽的开口的尺寸,大于或等于与所述第一凹槽间隔所述第二间距的所述第二凹槽的开口的尺寸;所述第二凹槽的开口的最大尺寸,为所述第一凹槽的开口的尺寸的1/12~1/8。

18、在一些示例中,所述在所述半导体基板上形成第一凹槽和位于所述第一凹槽至少一侧的第二凹槽,包括:沿多个所述第一凹槽的排列方向,在相邻两个所述第一凹槽之间形成至少一列所述第二凹槽,所述一列所述第二凹槽的排列方向与所述相邻两个所述第一凹槽的排列方向交叉。

19、在一些示例中,所述在所述半导体基板上形成介质层之后,所述制作方法还包括:在所述第一凹槽内形成导电材料,形成导电柱。

20、本技术实施例提供的半导体结构的制作方法的有益效果与上述任一示例提供的半导体结构的有益效果相同,在此不再赘述。并且,半导体结构的制作方法中,形成应力消除结构的材料与形成导电柱过程中的某一个介质层的材料相同,可采用同步工艺制作形成,工艺步骤简单,也没有增加额外的工艺成本。

21、又一方面,本技术一些实施例提供了一种半导体器件。所述半导体器件包括至少两个如上述任一示例提供的的半导体结构,且至少两个所述半导体结构通过所述导电柱耦接。

22、本技术实施例提供的半导体器件的有益效果与上述任一示例提供的半导体结构的有益效果相同,在此不再赘述。

23、本技术附加的方面和优点将在下面的描述中部分给出,部分将从下面的描述中变得明显,或通过本技术的实践了解到。

- 还没有人留言评论。精彩留言会获得点赞!