半导体器件及制备方法、功率模块、功率转换电路和车辆与流程

本技术属于半导体,尤其涉及一种半导体器件及制备方法、功率模块、功率转换电路和车辆。

背景技术:

1、在碳化硅金属氧化物半导体场效应管晶体管(sic metal-oxide-semiconductorfield-effect transistor,sic mosfet)中,实际应用中经常有时间出现体二极管续流的情况,然而体二极管由于碳化硅材料特性,开启电压太高,会造成较大的损耗,因此光伏逆变、电机驱动、dcdc转换等具体的半导体应用领域中,通常需要在模块中并联二极管作为反向恢复二极管,从而形成完整回路。但是,并联二极管会造成额外成本并且受限于模块封装形式。

2、另外,因碳化硅晶体材料的特性,以n型衬底晶体管为例,沟槽结构注入形成的p+区域较浅,器件关闭条件下在高温环境应用时漏极电流比较大,另外栅极沟槽拐角处存在电场集中效应,会导致栅氧化层很容易提前击穿。

技术实现思路

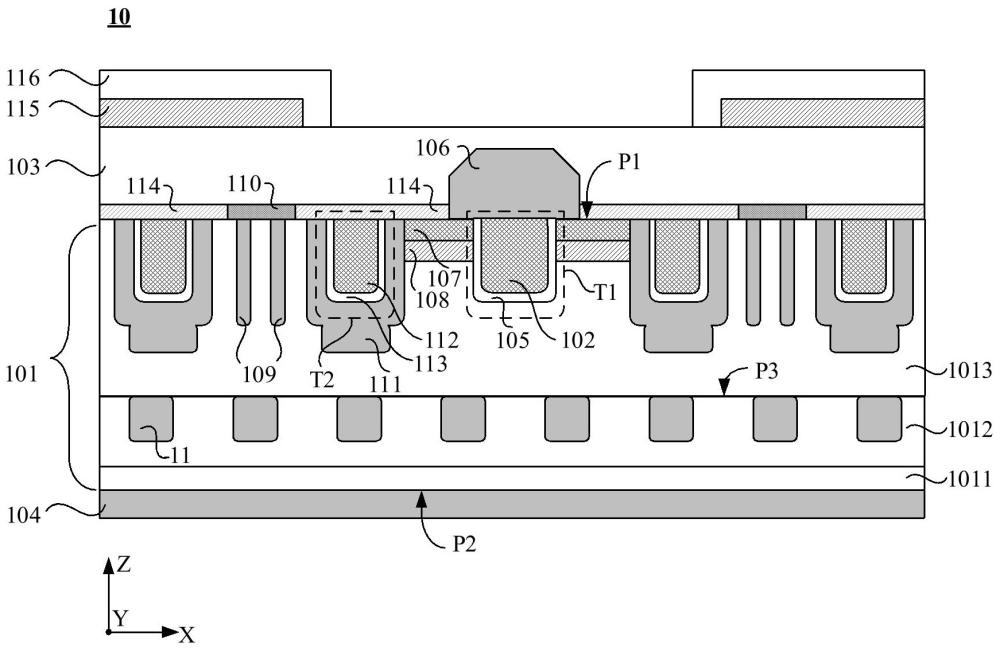

1、本技术实施例提供了一种半导体器件,包括半导体本体、栅极结构、源极和漏极。半导体本体被设置为第一导电类型,并且包括相对设置的第一表面和第二表面,第一表面设置有栅极沟槽,栅极沟槽从第一表面延伸至半导体本体中,栅极结构位于栅极沟槽内。半导体本体还包括被设置为第一导电类型的第一区域,该第一区域设置于第一表面。半导体本体还包括被设置为第二导电类型的阱区,该阱区设置于第一区域远离第一表面的一侧。半导体本体还包括被设置为第二导电类型的第二区域,该第二区域从第一表面延伸至半导体本体中。另外,源极位于第一表面,并且第二区域及至少部分第一表面与源极连接形成肖特基接触。漏极位于第二表面。另外,半导体器件还包括多个第一结构,多个第一结构被设置为第二导电类型,半导体本体还包括位于栅极结构与第二表面之间的第一界面,多个第一结构设置于第一界面靠近第二表面的一侧。

2、在一些实施例中,半导体本体包括依次层叠的衬底、第一外延层和第二外延层,第二外延层的远离衬底一侧的表面为上述第一表面,衬底的远离第二外延层一侧的表面为上述第二表面,第一外延层的远离衬底一侧的表面为第一界面。上述多个第一结构从第一界面延伸至第一外延层中。

3、在一些实施例中,半导体本体还包括位于衬底与第一外延层之间的第三外延层,第三外延层的远离衬底一侧的表面为第二界面。多个第一结构中,一部分第一结构从第一界面延伸至第一外延层中,另一部分第一结构从第二界面延伸至第三外延层中。

4、在一些实施例中,第一区域和第二区域沿第一方向排列,第一方向与第一表面相平行。多个第一结构沿第一方向间隔排列,每个第一结构沿第二方向延伸,第二方向与第一表面相平行,且与第一方向相交叉。或者,多个第一结构包括多行和多列,每行第一结构沿第一方向间隔排列,每列第一结构沿第二方向间隔排列。

5、在一些实施例中,第一区域和第二区域沿第一方向排列,第一方向与第一表面相平行,多个第一结构包括多条第一线型结构和多条第二线型结构,每条第一线型结构沿第一方向延伸,每条第二线型结构沿第二方向延伸。第二方向与第一表面相平行,且与第一方向相交叉,多条第一线型结构与多条第二线型结构交织成网。

6、在一些实施例中,相邻的两个第一结构的间距范围为1μm~8μm。

7、在一些实施例中,沿垂直于第一界面的方向,上述第一结构的深度范围为1μm~5μm。

8、在一些实施例中,第一表面还设置有源极沟槽,源极沟槽从第一表面延伸至半导体本体中。半导体本体还包括被设置为第二导电类型的第三区域,且第三区域设置于源极沟槽的表面。半导体器件还包括源极沟槽结构,源极沟槽结构位于源极沟槽内。上述多个第一结构还位于第三区域的靠近第二表面的一侧。

9、在一些实施例中,沿垂直于第一界面的方向,第一界面与第三区域的距离范围为1μm~3μm。

10、本技术实施例中,半导体本体被设置为第一导电类型,半导体本体还包括被设置为第一导电类型的第一区域、被设置为第二导电类型的阱区和被设置为第二导电类型的第二区域,第二区域与半导体本体构成pn结,并且第二区域及至少部分第一表面与源极连接形成肖特基接触,基于此,在续流的过程中不会发生空穴进入到漂移层的问题,降低了器件双击退化的风险,减少了半导体器件导通压降和反向恢复时间,减少了反向恢复能耗,增强了体二极管的导通性能和抗浪涌电流能力,可以避免外接续流二极管,从而可以降低电路设计复杂度和系统成本,提高碳化硅mosfet器件的可靠性。

11、并且,半导体器件还包括多个被设置为第二导电类型的第一结构,在施加反向偏压时,耗尽层会随着反向偏压的增加逐渐向漂移区下方延伸,当耗尽层延伸至第一结构处时,新的峰值电场将会在第一结构处形成,形成新的耗尽屏蔽层,以提高器件整体的反向特性和栅氧可靠性,从而保证器件长期可靠性。

12、另一方面,本技术实施例还提供了一种半导体器件的制备方法,包括如下步骤s10~步骤s80:

13、步骤s10:在衬底上形成第一外延层,第一外延层被设置为第一导电类型。第一外延层包括远离衬底一侧的第一界面。

14、步骤s20:在第一界面形成多个第一结构,第一结构被设置为第二导电类型。多个第一结构从第一界面延伸至第一外延层中。

15、步骤s30:形成第二外延层,第二外延层被设置为第一导电类型,并且,第二外延层位于第一外延层的远离衬底的一侧,第二外延层包括远离衬底一侧的第一表面,衬底包括远离第二外延层一侧的第二表面。

16、步骤s40:形成第一区域、阱区和栅极沟槽。第一区域位于第一表面,且被设置为第一导电类型。阱区位于第一区域远离第一表面的一侧,且设置为第二导电类型。栅极沟槽从第一表面延伸至第二外延层中。

17、步骤s50:形成第二区域,第二区域从第一表面延伸至第二外延层中,且被设置为第二导电类型。

18、步骤s60:在栅极沟槽内形成栅极结构。

19、步骤s70:在第一表面形成源极,第二区域及至少部分第一表面与源极连接形成肖特基接触。

20、步骤s80:形成漏极,漏极位于衬底的远离第一外延层的一侧。

21、在一些实施例中,在形成栅极沟槽的过程中,还在第一表面形成源极沟槽,源极沟槽从第一表面延伸至第二外延层中。在形成第二区域的过程中,还在源极沟槽的表面形成第三区域,第三区域被设置为第二导电类型,多个第一结构还位于第三区域的靠近第二表面的一侧。在栅极沟槽内形成栅极结构的过程中,还在源极沟槽内形成源极沟槽结构。

22、根据本技术实施例提供的制备方法,在制备半导体器件的过程中形成多个第一结构,制备方法较为简单,没有增加额外的生产成本,多个第一结构可用于提高器件整体的反向特性和栅氧可靠性,从而保证器件长期可靠性。另外,在制备半导体器件的过程中,还在半导体本体上形成第二区域,并且将第二区域及半导体本体的至少部分第一表面与源极连接形成肖特基接触,制备方法较为简单。上述实施例提供的制备方法所制备出的半导体器件,通过第二区域及半导体本体的至少部分第一表面与源极连接形成的肖特基接触,可以减少半导体器件导通压降和反向恢复时间,减少了反向恢复能耗,增强体二极管的导通性能和抗浪涌电流能力,另外,在续流的过程中不会发生空穴进入到漂移层的问题,降低了器件双击退化的风险,避免外接续流二极管,从而降低电路设计复杂度和系统成本,提高碳化硅mosfet器件的可靠性。

23、另一方面,本技术实施例还提供一种功率模块,该功率模块包括基板以及如上述任一实施例的半导体器件,基板用于承载半导体器件。

24、又一方面,本技术实施例还提供一种功率转换电路,该功率转换电路用于电流转换、电压转换、功率因数校正中的一个或多个。功率转换电路包括电路板以及如上述任一实施例的半导体器件,半导体器件与电路板电连接。

25、又一方面,本技术实施例还提供一种车辆,该车辆包括负载以及如上述实施例的功率转换电路,功率转换电路用于将交流电转换为直流电、将交流电转换为交流电、将直流电转换为直流电或者将直流电转换为交流电后,输入到负载。

26、上述功率模块、功率转换电路和车辆具有与上述一些实施例中提供的半导体器件相同的结构和有益技术效果,在此不再赘述。

- 还没有人留言评论。精彩留言会获得点赞!