一种基于孔径补偿的封装系统及其补偿方法、系统与流程

本发明涉及半导体封装,具体涉及一种基于孔径补偿的封装系统及其补偿方法、系统。

背景技术:

1、半导体装置内积体电路一般是制作在一晶圆上,再切割成个别的小晶粒。基于大量生产以降低成本的需求,晶圆的尺寸由早期的四寸、六寸逐渐往八寸、十二寸甚至于十六寸发展。又,完成积体电路之后,常需要作晶背研磨再切割成晶粒,晶粒之厚度得以降低以符合高密度或薄型封装之规格要求。晶圆的良率对半导体装置的工作性能影响至关重要。但是,晶圆在生产堆叠过程中容易形成边缘弯曲的问题,由此将导致晶圆上的缺陷也随之增多。

2、参见申请公布号为cn108110043a的专利申请晶圆弯曲度的优化方法,其公开了一种晶圆弯曲度的优化方法,其方法为:提供晶圆,晶圆的正面形成有晶面sin,晶圆的背面形成有晶背sin,晶面sin和晶背sin是在同一炉管工艺中形成的;对晶圆的正面进行处理以在正面形成耐酸液腐蚀的保护层;在保护层的保护下,使用酸液去除晶背sin的至少一部分。该方法通过调整晶圆的弯曲度,进而期望通过降低调节晶圆弯曲度提高后续键合等工艺步骤的质量。

3、但是,申请人注意到,虽然传统的方案虽然在晶圆的加工工艺上作出了优化,可随着半导体技术的不断发展,尤其是当半导体装置的晶圆层数达到一定数量,且晶圆上的电路结构越来越复杂化之后,仍然非常容易在边缘上产生弯曲进而引起缺陷。

4、因此,目前继续一种能够减小堆叠过程中弯曲缺陷的方法。

技术实现思路

1、本发明的目的在于提供一种基于孔径补偿的封装系统及其补偿方法、系统,部分地解决或缓解现有技术中的上述不足,能够通过有限性区域分类进行孔径的差异化设置。

2、为了解决上述所提到的技术问题,本发明具体采用以下技术方案:

3、本发明的第一方面,在于提供一种基于孔径补偿的封装系统,包括:

4、母片,所述母片上间隔地设置有多个传输接口,所述传输接口用于与堆叠其上的晶粒的通孔电连接,且相邻两层所述晶粒之间通过所述通孔电连接;

5、设置在所述母片上的第一堆叠部,其中,所述第一堆叠部包括:多层第一晶粒层,一层晶粒层包括:多个间隔分布的所述晶粒;且所述第一晶粒层包括:沿所述母片的边缘布置的第一边缘区,以及沿所述母片的中心区布置的第一中心区,其中,所述第一边缘区设置有至少一列第一边缘晶粒,所述第一中心区设置有至少一列第一中心晶粒,以及所述第一边缘区和所述第一中心区之间间隔地排列有多列第一间隔晶粒;

6、所述第一边缘晶粒、所述第一间隔晶粒以及所述第一中心晶粒的第一通孔尺寸d1、第二通孔尺寸d2、第三通孔尺寸d3满足第一补偿规则,且所述第一补偿规则包括:d1≥d2,d1>d3;

7、设置在所述第一堆叠部上的第二堆叠部,其中,所述第二堆叠部包括:多层第二晶粒层,所述第二晶粒层包括:沿所述母片的边缘布置的第二边缘区,以及沿所述中心区布置的第二中心区,其中,所述第二边缘区设置有至少一列第二边缘晶粒,所述第二中心区设置有至少一列第二中心晶粒,以及所述第二边缘区和所述第二中心区之间间隔地排列有多列第二间隔晶粒;

8、所述第二边缘晶粒、所述第二间隔晶粒以及所述第二中心晶粒的第四通孔尺寸d4、第五通孔尺寸d5、第六通孔尺寸d6满足第二补偿规则,且所述第二补偿规则包括:d4≥d5,d4>d6。

9、在一些实施例中,所述第一通孔尺寸d1、所述第二通孔尺寸d2、所述第三通孔尺寸d3还满足以下第三补偿规则:

10、(d1-d3)/d3<10%;

11、(d2-d3)/d3<5%。

12、在一些实施例中,所述第四通孔尺寸d4、所述第五通孔尺寸d5、所述第六通孔尺寸d6还满足以下第四补偿规则:

13、(d4-d6)/d6<10%;

14、(d5-d6)/d6<5%。

15、在一些实施例中,中心区的半径r≤75mm。

16、在一些实施例中,d2>d3,和/或,d5>d6。

17、在一些实施例中,所述第一堆叠部和所述第二堆叠部满足第五补偿规则,所述第五补偿规则包括:d1≤d4。

18、本发明另一方面还提供了一种基于孔径补偿的补偿方法,所述补偿方法应用于如任意一项实施例所述的一种基于孔径补偿的封装系统,对应地,所述方法包括:

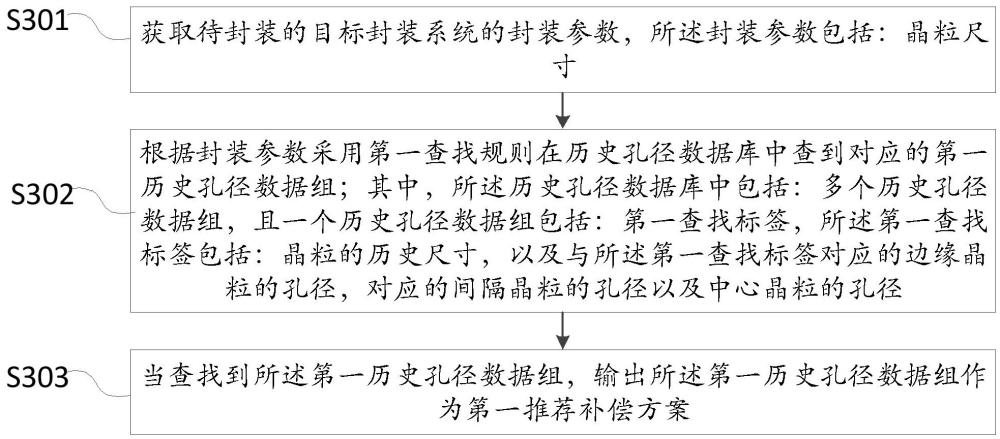

19、s301,获取待封装的目标封装系统的封装参数,所述封装参数包括:晶粒尺寸;

20、s302,根据所述封装参数采用第一查找规则在历史孔径数据库中查到对应的第一历史孔径数据组;其中,所述历史孔径数据库中包括:多个历史孔径数据组,且一个历史孔径数据组包括:第一查找标签,所述第一查找标签包括:晶粒的历史尺寸;以及与所述第一查找标签对应的边缘晶粒的通孔尺寸,对应的间隔晶粒的通孔尺寸以及中心晶粒的通孔尺寸;对应地,所述第一查找规则要求所查到的所述第一历史孔径数据组的所述晶粒尺寸与所述历史尺寸之间的差值满足以下模型:|r1-r2|/f≤h;其中,r1为所述晶粒尺寸,r2为所述历史尺寸,f为参考尺寸,所述参考尺寸为r1或r2,h为预设的查找差异阈值;

21、s303,当查找到所述第一历史孔径数据组,输出所述第一历史孔径数据组作为第一推荐补偿方案。

22、在一些实施例中,所述历史孔径数据组还包括:第二查找标签,所述第二查找标签包括以下一种或多种类型:所述母片的历史尺寸,所述晶粒的历史厚度;对应地,所述封装参数还包括以下一种或多种:所述母片的实际尺寸,所述晶粒的实际厚度;对应地,在s303之前,还包括步骤:

23、s304,根据所述封装参数采用第二查找规则在历史孔径数据库中查到对应的第二历史孔径数据组;其中,所述第二查找规则要求所查到的所述第二历史孔径数据组在满足所述第一查找规则的基础上,进一步地满足以下要求:

24、|母片的历史尺寸-母片的实际尺寸|/母片的参考尺寸≤母片差值阈值,其中,所述母片的参考尺寸为所述母片的历史尺寸或所述母片的实际尺寸;

25、和/或,|晶粒的历史厚度-晶粒的实际厚度|/晶粒的参考厚度≤厚度差值阈值,其中,所述晶粒的参考厚度为所述晶粒的历史厚度或所述晶粒的实际厚度;

26、s305,当查找到所述第二历史孔径数据组,输出所述第二历史孔径数据组作为第二推荐补偿方案。

27、在一些实施例中,仅在检索到所述第一历史孔径数据组时,才将在所述第一历史孔径数据组中进一步查找所述第二历史孔径数据组。

28、本发明还提供了另一种基于孔径补偿的补偿系统,所述补偿系统应用于如任意一项实施例所述的一种基于孔径补偿的封装系统,对应地,所述补偿系统包括:

29、封装参数获取模块,用于获取待封装的目标封装系统的封装参数,所述封装参数包括:晶粒尺寸;

30、查找模块,用于根据所述封装参数采用第一查找规则在历史孔径数据库中查到对应的第一历史孔径数据组;其中,所述历史孔径数据库中包括:多个历史孔径数据组,且一个历史孔径数据组包括:第一查找标签,所述第一查找标签包括:晶粒的历史尺寸;以及与所述第一查找标签对应的边缘晶粒的通孔尺寸,对应的间隔晶粒的通孔尺寸以及中心晶粒的通孔尺寸;对应地,所述第一查找规则要求所查到的所述第一历史孔径数据组的所述晶粒尺寸与所述历史尺寸之间的差值满足以下模型:|r1-r2|/f≤h;其中,r1为所述晶粒尺寸,r2为所述历史尺寸,f为参考尺寸,所述参考尺寸为r1或r2,h为预设的查找差异阈值;

31、推荐模块,用于当查找到所述第一历史孔径数据组,输出所述第一历史孔径数据组作为第一推荐补偿方案。

32、有益技术效果:

33、本发明提供了一种基于边缘、间隔区域、中心区域三分类的有限分级,所实现的孔径差异化设置方案。这种差异设置能够通过增强边缘区间的刚性强度,以通过局部的强度调节提升半导体器件的整体良率(即通过边缘的局部调节,减小半导体器件的整体变形程度),从而在控制弯曲变形的基础上,减小调节压力。

34、换言之,针对大尺寸、大厚度的半导体器件,本发明通过对应力较大的边缘区域,以及受边缘区域拉伸的中间区域进行有限性的区域分类,并针对该有限区域设置孔径的梯度式差异调节。

35、进一步地,针对这一梯度式差异调节,本发明还提供了一种快速设置差异方案的多重查询机制。具体地,本发明通过标准化数据库的建立,以及对晶粒尺寸、晶粒厚度以及半导体尺寸(即母片的大小)等关键因素进行查询优先级区别设置,本发明能够利用标准化数据库快速查询得到参考的孔径设置方案。

36、值得说明的是,针对孔径的设置,本发明从区域分类,以及孔径的具体设置值等两个维度进行限制,通过限定性的区域分类模式构建出一个通用性的标准化数据库(换言之,通过区域性的限定方案对变量进行控制,以使得数据库的通用性更强,查询结果更为可靠)。进而,在长期的半导体堆叠加工过程中,不同的梯度孔径设置数值的重复性较强(或者说,通用性较高),由此,这种具有通用性的有限梯度调节方案,对于孔径加工工艺所带来的压力也相对较小。例如,从工厂的实际应用阶段来说,仅需要设置少量的孔径加工线,且孔径尺寸的增量也相对有限,这也使得孔径加工更容易实施,且不会因为孔径增大反而过多地增大晶粒的缺陷或影响晶粒的刚性强度。

37、因此,这种基于有限性的梯度调节设置方案,与标准数据库的建立相协同,能够在增大晶粒的孔径尺寸,和控制大孔径加工过程中所可能产生更多缺陷等两方面之间进行良好的平衡。

38、并且,针对这些孔径差异化设置方案,本发明还提供了一种能够考虑孔径差异因素,对修正研磨厚度进行预测的模型预测方法。由此,通过在单一层上对晶粒的孔径进行有限性梯度设置,以及通过在不同层之间对层的研磨厚度进行有限梯度设置两方面进行协同处理,能够进一步地减小数值差异程度。也即是说,两重手段的协调能够确实边缘孔径无需过大,上层晶粒研磨厚度无需过小,从而避免梯度化调节反而对晶粒的加工工艺带来新的压力,使得调节过程中引入过多的缺陷。

- 还没有人留言评论。精彩留言会获得点赞!