操作电路的制作方法

[0001]

本发明有关于一种操作电路,特别是有关于一种具有静电放电(electrostatic discharge;esd)保护功能的操作电路。

背景技术:

[0002]

因静电放电(electrostatic discharge;esd)所造成的组件损害对集成电路产品来说已经成为最主要的可靠度问题之一。尤其是随着尺寸不断地缩小至深次纳米的程度,金氧半导体的栅极氧化层也越来越薄,集成电路更容易因静电放电现象而遭受破坏。

技术实现要素:

[0003]

本发明提供一种操作电路,其耦接于一输入输出垫与一接地端之间,并包括一核心电路、一n型晶体管、一静电放电保护电路以及一控制电路。n型晶体管根据一特定节点的电压位准,决定是否导通核心电路与接地端之间的一路径。静电放电保护电路耦接于输入输出垫与核心电路之间,用以避免一静电放电电流流经核心电路,并包括一检测电路以及一释放组件。检测电路检测一静电放电事件是否发生在输入输出垫,用以产生一检测信号。释放组件根据检测信号提供一释放路径,用以释放静电放电电流。控制电路根据检测信号,控制特定节点的电压位准。

附图说明

[0004]

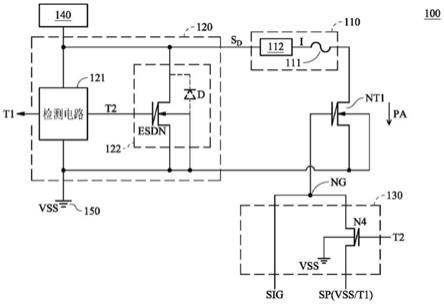

图1为本发明的操作电路的一可能示意图。

[0005]

图2为本发明的操作电路的另一可能示意图。

[0006]

图3为本发明的操作电路的另一可能示意图。

[0007]

图4为本发明的检测电路的一可能实例。

[0008]

图5为本发明的检测电路的另一实施架构。

[0009]

附图标号:

[0010]

100、200、300:操作电路;

[0011]

110、210、310:核心电路;

[0012]

111:保险丝;

[0013]

112:内部电路;

[0014]

120、220、320:静电放电保护电路;

[0015]

121、400、500:检测电路;

[0016]

122、222、322:释放组件;

[0017]

130、230、330:控制电路;

[0018]

140、240、340、440、540:输入输出垫;

[0019]

150、250、350、450、550:接地端;

[0020]

410、520:电阻;

[0021]

420、510:电容;

[0022]

430、530:反相器;

[0023]

i:操作电流;

[0024]

ng:特定节点;

[0025]

nd1~nd4:节点;

[0026]

t1、t2:检测信号;

[0027]

vss:接地位准;

[0028]

nt1~nt3、esdn、n0~n4:n型晶体管;

[0029]

p0~p4:p型晶体管;

[0030]

d:寄生二极管;

[0031]

sp:预设位准;

[0032]

sig:特定信号;

[0033]

pa:路径;

[0034]

s

d

:驱动信号。

具体实施方式

[0035]

为让本发明的目的、特征和优点能更明显易懂,下文特举出实施例,并配合所附附图,做详细的说明。本发明说明书提供不同的实施例来说明本发明不同实施方式的技术特征。其中,实施例中的各组件的配置为说明之用,并非用以限制本发明。另外,实施例中附图标号的部分重复,为了简化说明,并非意指不同实施例之间的关联性。

[0036]

图1为本发明的操作电路的一可能示意图。如图所示,操作电路100包括一核心电路110、一n型晶体管nt1、一静电放电保护电路120以及一控制电路130。核心电路110由控制电路130所控制。图1仅显示控制电路130的一部分架构,其中该部分架构与本发明有关,但并非用以限制本发明。控制电路130仍可能具有其它硬件架构,为方便说明,图1省略了控制电路130的其它硬件架构。本发明并不限定核心电路110的架构。任何会受到静电放电电流影响的电路均可作为核心电路110。

[0037]

在一可能实施例中,核心电路110包括一保险丝(fuse)111及一内部电路112。内部电路112用以程序化保险丝111。本发明并不限定保险丝111与内部电路112之间的连接关系。在本实施例中,内部电路112耦接于静电放电保护电路120与保险丝111之间,并且保险丝111耦接于内部电路112与n型晶体管nt1之间。在其它实施例中,保险丝111耦接于静电放电保护电路120与内部电路112之间,并且内部电路112耦接于保险丝111与n型晶体管nt1之间。

[0038]

当静电放电事件未发生时,内部电路112可能通过输入输出垫140接收一驱动信号s

d

,并根据驱动信号s

d

,产生一电流i,用以程序化(programming)保险丝111。当保险丝111被程序化时,保险丝111可能由一第一状态切换至一第二状态。举例而言,当电流i流过保险丝111时,保险丝111可能由一短路(short)状态切换至一开路(open)状态。在另一可能实施例中,保险丝111可能由开路状态切换至短路状态。

[0039]

然而,当输入输出垫140发生一静电放电事件时,内部电路112可能会受到来自输入输出垫140的静电放电电流的伤害。另外,内部电路112可能因静电放电电流的影响,而误

程序化保险丝111。由于保险丝111的状态被不正常地改变,故可能造成内部电路112误动作。在本实施例中,当静电放电事件发生时,经由控制电路130的动作,便可避免保险丝被误程序化。

[0040]

n型晶体管nt1根据一特定节点ng的电压位准,决定是否导通核心电路110与接地端150之间的路径pa。举例而言,当特定节点ng的电压位准为一高位准(如5v)时,n型晶体管nt1导通,故路径pa被导通。因此,核心电路110通过路径pa耦接接地端150。然而,当特定节点ng的电压位准为一低位准(如0v)时,n型晶体管nt1不导通,故路径pa不导通。因此,核心电路110电性未连接至接地端150。

[0041]

在本实施例中,n型晶体管nt1的栅极(gate)耦接特定节点ng,其漏极(drain)耦接核心电路110,其源极(source)及基极(bulk)耦接接地端150。当一静电放电事件发生在输入输出垫140时,n型晶体管nt1不导通,使得静电放电电流不会流过核心电路110。

[0042]

静电放电保护电路120耦接于输入输出垫140与核心电路110之间,用以避免静电放电电流流经核心电路110。本发明并不限定静电放电保护电路120的架构。任何可避免静电放电电流流入核心电路110,并在静电放电事件未发生时,不影响核心电路110动作的电路架构,均可作为静电放电保护电路120。在本实施例中,静电放电保护电路120包括一检测电路121以及一释放组件122。

[0043]

检测电路121检测一静电放电事件是否发生在输入输出垫140,用以产生一检测信号t2。举例而言,当一静电放电事件发生在输入输出垫140,并且接地端150接收到一接地位准vss时,检测信号t2为一特定位准(如一高位准)。当静电放电事件未发生时,检测信号t2不为特定位准(如为一低位准)。

[0044]

在其它实施例中,检测电路121还产生另一检测信号t1。检测信号t1为检测信号t2的反相信号。举例而言,当检测信号t1为一高位准时,检测信号t2为一低位准。当检测信号t1为一低位准时,检测信号t2为一高位准。本发明并不限定检测电路121的架构。稍后将通过图4及图5说明检测电路121的可能实施方式。

[0045]

释放组件122根据检测信号t2提供一释放路径,用以释放静电放电电流。举例而言,当一静电放电事件发生在输入输出垫140,并且接地端150接收接地位准vss时,检测信号t2为一特定位准。因此,释放组件122导通,用以将静电放电电流从输入输出垫140释放至接地端150。当静电放电事件未发生时,释放组件122不导通。

[0046]

本发明并不限定释放组件122的种类。在一可能实施例中,释放组件122为一n型晶体管esdn。n型晶体管esdn的栅极耦接节点nd2,其第一源/漏极耦接输入输出垫140,其第二源/漏极与基极耦接接地端150。

[0047]

当一静电放电事件发生在输入输出垫140,并且接地端150接收接地位准vss时,n型晶体管esdn导通。此时,如果输入输出垫140接收一正静电放电电压时,n型晶体管esdn将静电放电电流由输入输出垫140释放至接地端150。如果输入输出垫140接收到一负静电放电电压时,n型晶体管esdn的漏极与基极间的寄生二极管d将静电放电电流由接地端150释放至输入输出垫140。

[0048]

控制电路130根据检测信号t2,控制特定节点ng的电压位准。举例而言,当检测信号t2为一特定位准时,表示发生静电放电事件,故控制电路130设定特定节点ng的位准等于一预设位准sp。在一可能实施例中,预设位准sp等于接地位准vss。在另一可能实施例中,预

设位准sp等于检测信号t1的位准。然而,当检测信号t2不为特定位准时,表示未发生静电放电事件,故控制电路130提供一特定信号sig予特定节点ng。

[0049]

在本实施例中,控制电路130包括一n型晶体管n4。n型晶体管n4的栅极接收检测信号t2,其漏极耦接特定节点ng,其源极接收预设位准sp,其基极接收接地位准vss。当检测信号t2为特定位准时,n型晶体管n4导通,用以传送预设位准sp至特定节点ng。当检测信号t2不为特定位准时,n型晶体管n4不导通,用以停止传送预设位准sp至特定节点ng。此时,控制电路130传送特定信号sig予特定节点ng。在一可能实施例中,特定信号sig由一信号产生电路(未显示)所产生。

[0050]

图2为本发明的操作电路的另一可能示意图。操作电路200包括一核心电路210、一n型晶体管nt2、一静电放电保护电路220以及一控制电路230。静电放电保护电路220耦接输入输出垫240及接地端250。接地端250接收一接地位准vss。由于图2的核心电路210、n型晶体管nt2及静电放电保护电路220的特性与图1的核心电路110、n型晶体管nt1及静电放电保护电路120的特性相似,故不再赘述。

[0051]

在本实施例中,图2的控制电路230比图1的控制电路130多了一p型晶体管p4。如图所示,p晶体管p4并联n型晶体管n4,并根据检测信号t1设定特定节点ng的电压位准。由于检测信号t2为检测信号t1的反相信号,故当n型晶体管n4导通时,p型晶体管p4也导通。因此,n型晶体管n4及p型晶体管p4传送特定位准sp至特定节点ng。当n型晶体管n4不导通时,p型晶体管p4也不导通。因此,n型晶体管n4及p型晶体管p4停止传送特定位准sp至特定节点ng。

[0052]

在本实施例中,p型晶体管p4的栅极接收检测信号t1,其第一源/漏极耦接特定节点ng,其第二源/漏极接收特定位准sp,其基极接收一操作电压vdd。在一可能实施例中,操作电压vdd高于接地位准vss。

[0053]

图3为本发明的操作电路的另一可能示意图。操作电路300包括一核心电路310、一n型晶体管nt3、一静电放电保护电路320以及一控制电路330。静电放电保护电路320耦接输入输出垫340及接地端350。接地端350接收一接地位准vss。由于图3的核心电路310、n型晶体管nt3及静电放电保护电路320的特性与图1的核心电路110、n型晶体管nt1及静电放电保护电路120的特性相似,故不再赘述。

[0054]

图3的控制电路330比图2的控制电路230多了一n型晶体管n3以及一p型晶体管p3。n型晶体管n3耦接于特定节点ng与一信号产生电路(未显示)之间,根据检测信号t1,决定是否传送特定信号sig至特定节点ng。如图所示,n型晶体管n3的栅极接收检测信号t1,其第一源/漏极耦接特定节点ng,其第二源/漏极接收特定信号sig,其基极接收接地位准vss。

[0055]

p型晶体管p3并联n型晶体管n3,并根据检测信号t2,决定是否传送特定信号sig至特定节点ng。如图所示,p型晶体管p3的栅极接收检测信号t2,其第一源/漏极耦接特定节点ng,第二源/漏极接收特定信号sig,其基极接收操作电压vdd。

[0056]

在本实施例中,由于检测信号t2为检测信号t1的反相信号,故当n型晶体管n3导通时,p型晶体管p3也导通。因此,n型晶体管n3及p型晶体管p3传送特定信号sig至特定节点ng。当n型晶体管n3不导通时,p型晶体管p3也不导通。因此,n型晶体管n3及p型晶体管p3停止传送特定信号sig至特定节点ng。

[0057]

在其它实施例中,当n型晶体管n4导通时,n型晶体管n3不导通。因此,特定节点ng的位准等于接地位准vss。当n型晶体管n4不导通时,n型晶体管n3导通。因此,特定节点ng的

位准等于特定信号sig。

[0058]

图4为本发明的检测电路的一可能实例。如图所示,检测电路400包括一电阻410、一电容420以及一反相器(inverter)430。电阻410耦接于输入输出垫440与节点nd1之间。电容420耦接于节点nd1与接地端450之间。在本实施例中,电容420为一n型晶体管n0。如图所示,n型晶体管n0的栅极耦接节点nd1。n型晶体管n0的源极、漏极与基极均耦接接地端450。在一可能实施例中,接地端450接收一接地位准vss。

[0059]

当一静电放电事件发生在输入输出垫440,并且接地端450接收接地位准vss时,由于电容420的特性,节点nd1为一低位准,约等于接地位准vss。然而,当静电放电事件未发生在输入输出垫440时,如果输入输出垫440接收一第一操作电压(如5v),并且接地端450接收接地位准vss时,节点nd1为一高位准(如5v)。在本实施例中,节点nd1的位准作为一检测信号t1。

[0060]

反相器430反相检测信号t1的位准,用以产生检测信号t2。因此,检测信号t2(如称为第一检测信号)为检测信号t1(如称为第二检测信号)的反相信号。在本实施例中,反相器430包括一p型晶体管p1以及一n型晶体管n1。

[0061]

p型晶体管p1的栅极耦接节点nd1。p型晶体管p1的第一源/漏极与基极耦接输入输出垫440。p型晶体管p1的第二源/漏极)耦接节点nd2。n型晶体管n1的栅极耦接节点nd1。n型晶体管n1的第一源/漏极耦接节点nd2。n型晶体管n1的第二源/漏极与基极耦接接地端450。在本实施例中,节点nd2的电压位准作为检测信号t2。

[0062]

在一正常模式下(未发生静电放电事件),输入输出垫440接收一第一操作电压(如5v),接地端450接收一第二操作电压(如0v),其中第一操作电压大于第二操作电压。此时,检测信号t1约等于第一操作电压。因此,n型晶体管n1导通,使得检测信号t2约等于第二操作电压。

[0063]

在一保护模式下(发生静电放电事件),输入输出垫440接收一静电放电电压,接地端450接收一接地位准(如0v)。此时,检测信号t1约等于接地位准。因此,p型晶体管p1导通,使得检测信号t2为高位准(即特定位准)。此时,检测电路400外部的一释放组件(如图1的释放组件122)被导通,用以将静电电流由输入输出垫440释放至接地端450,以避免静电电流流入核心电路。

[0064]

图5为本发明的检测电路的另一实施架构。如图所示,检测电路500包括一电容510、一电阻520以及一反相器530。电容510耦接于输入输出垫540与节点nd3之间。在本实施例中,电容510为一p型晶体管p0。p型晶体管p0的栅极耦接节点nd3。p型晶体管p0的源极、漏极与基极耦接输入输出垫540。电阻520耦接于节点nd3与接地端550之间。在本实施例中,节点nd3的电压位准作为检测信号t2。

[0065]

反相器530反相检测信号t2的电压位准,用以产生检测信号t1。在本实施例中,反相器530包括一p型晶体管p2以及一n型晶体管n2。p型晶体管p2的栅极耦接节点nd3,其第一源/漏极与基极耦接输入输出垫540,其第二源/漏极耦接节点nd4。n型晶体管n2的栅极耦接节点nd3,其第一源/漏极耦接节点nd4,其第二源/漏极与基极耦接接地端550。

[0066]

在一正常模式下(未发生静电放电事件),输入输出垫540接收一第一操作电压(如5v),接地端550接收一第二操作电压(如0v),其中第一操作电压大于第二操作电压。此时,检测信号t2约等于第二操作电压。因此,p型晶体管p2导通,使得检测信号t1约等于第一操

作电压。

[0067]

在一保护模式下(发生静电放电事件),输入输出垫540接收一静电放电电压,接地端550接收一接地位准(如0v)。此时,检测信号t2为一高位准(如称一特定位准)。因此,n型晶体管n2导通,使得检测信号t1为低位准。

[0068]

除非另作定义,在此所有词汇(包含技术与科学词汇)均属本发明所属技术领域中具有通常知识者的一般理解。此外,除非明白表示,词汇于一般字典中的定义应解释为与其相关技术领域的文章中意义一致,而不应解释为理想状态或过分正式的语态。

[0069]

虽然本发明已以较佳实施例揭露如上,然其并非用以限定本发明,任何所属技术领域中具有通常知识者,在不脱离本发明的精神和范围内,当可作些许的更动与润饰。举例来,本发明实施例所系统、装置或是方法可以硬件、软件或硬件以及软件的组合的实体实施例加以实现。因此本发明的保护范围当视前附的权利要求书所界定者为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1