单晶圆电池保护电路、电池充放电电路及便携式电子设备的制作方法

[0001]

本实用新型涉及电池充放电技术领域,尤指一种单晶圆电池保护电路、电池充放电电路及便携式电子设备。

背景技术:

[0002]

随着近年来移动终端功能的不断增加,移动终端的性能也在飞速提升,这对终端电池也提出了更大的要求。有的应用电池需要做得很小,有的应用电池需要做得成本很低,而传统的电池保护方案通常占版面积很大,成本很高,已经越来越不适应新的市场需求。

[0003]

传统的电池保护方案是由分立器件达成的。需要一个控制电路芯片以及一个包含有两个n型功率mos管的芯片。控制电路芯片通过控制这两个功率mos管的栅极电压来实现对电池的充放电控制。控制电路芯片是用cmos工艺做成,而功率mos管芯片通常用一种垂直结构的dmos或umos管做成。由于cmos和dmos/umos是两种完全不同的工艺,因此控制电路芯片和两个功率mos管芯片通常来自于两个不同的供应商,是两个独立的芯片。另外这种分离器件方案的充放电外围电路需要两个电阻以及一个电容。

[0004]

为了缩小上述分离器件电池保护的方案面积以及降低方案成本,在中国专利cn103474967a中,我司提出了单晶圆电池保护电路及充放电电路。这种单晶圆电池保护电路将传统方案的控制电路芯片,两个功率mos管芯片以及外围的一个电阻都集成到一个半导体衬底上,外围充放电电路只需一个电阻及一个电容。我司提出的单晶圆电池保护方案不但将控制电路芯片与两个功率mos管芯片集成到一个半导体衬底上,进一步地,我司将传统方案的两个功率mos管结构合并成一个功率mos管以进一步缩小方案面积降低方案成本。

[0005]

目前,为了将电路面积做到最小以及成本做到最低,通常选用5vcmos工艺来实现。而5v cmos工艺mos管击穿电压在8v至12v之间。由于电池保护电路在充放电以及生产测试过程中可能会产生高达16v的尖峰电压以及直流高电压,用5v cmos工艺做成的单晶圆电池保护电路会被尖峰电压或者直流高电压击穿从而造成单晶圆电池保护电路的损坏。

[0006]

一种直观的解决办法是选用击穿电压更高的半导体工艺来增加单晶圆电池保护电路的耐压值,使其能够承受16v尖峰电压以及直流高电压,但是这样做会增加工艺层数以及大大增加半导体器件在芯片上所占用的面积,使保护电路的成本大大上涨。

[0007]

有鉴于此,本实用新型提供了一种单晶圆电池保护电路、电池充放电电路及便携式电子设备,以解决上述单晶圆电池保护电路被直流高电压和尖峰电压损坏的问题。

技术实现要素:

[0008]

本实用新型的目的是提供一种单晶圆电池保护电路、电池充放电电路及便携式电子设备,在电池生产测试过程以及充放电使用时,可使单晶圆电池保护电路免受直流高电压和尖峰电压的损坏,延长充放电电路和电池的使用寿命。

[0009]

本实用新型提供的技术方案如下:

[0010]

本实用新型提供了一种单晶圆电池保护电路,包括:基本保护电路、钳压电路、栅

极衬底控制电路、过温保护电路和充放电控制mos管;

[0011]

所述充放电控制mos管的源极和漏极的一端连接至电池负极,所述充放电控制mos管的源极和漏极的另一端连接至充电器负极或负载;所述充放电控制mos管的栅极和衬底分别连接至所述栅极衬底控制电路;

[0012]

所述过温保护电路,分别与所述基本保护电路和所述栅极衬底控制电路耦接,用于检测所述单晶圆电池保护电路所集成芯片的温度,并同所述基本保护电路共同控制导通所述栅极衬底控制电路;

[0013]

所述钳压电路连接所述栅极衬底控制电路,用于钳制所述栅极衬底控制电路的供电电压。

[0014]

本方案中的电池保护电路涉及非常多的半导体器件,在电池生产测试过程以及充放电使用时可能被尖峰电压或直流高电压损坏。例如5vcmos工艺mos管的击穿电压在8v至12v之间,若生产测试过程及充放电使用时产生的尖峰电压超过这个击穿电压,就会将mos管损坏。一般直观的解决办法是将mos管的耐压值提高,如此会增加工艺层数以及增大mos管在芯片上的面积,提高芯片的成本。本方案为了在保证成本以及芯片面积的前提下保护器件不受尖峰电压或直流高电压损坏,加入了钳压电路,将电压钳制在一定的范围内,即便在生产测试过程中及充放电使用时有尖峰电压或直流高电压,也会被钳压电路将电压钳制在安全电压范围,保证保护电路不被损坏。

[0015]

在电池保护电路的生产测试过程中,首先将电池保护芯片以及电阻电容做成电池保护板,然后将电池保护板与电芯连接到一起成为带保护功能的电池。在所述电池的生产测试过程中会经常用到诸如保护板测试仪,综合测试仪,分容柜等测试设备。保护板测试仪用于检测保护板是否合格,综合测试仪用于检测带保护功能的电池是否合格,分容柜用于检测带保护功能的电池的容量大小。这些测试设备在测试过程中经常会产生高达16v的尖峰电压或直流高电压,因此,传统电池保护方案需要将充电控制mos管mc和放电控制mos管md的击穿电压做到16v以上,以防止带保护功能的电池在生产测试过程中被16v的尖峰电压或直流高电压击穿。

[0016]

理论上,单晶圆电池保护电路需要将充放电控制mos管的源极和漏极的击穿电压同时做到16v以上,才能保证带保护功能的电池在生产测试过程中不被测试设备产生的高达16v的尖峰电压或直流高电压击穿。但是将充放电控制mos管的击穿电压做到16v以上,成本会很高。

[0017]

采用本实用新型的钳压电路,充放电控制mos管的耐压只需12v,也就是传统5v cmos工艺的击穿电压,即可防止带保护功能的电池在生产测试过程中及充放电使用时不被高达16v的尖峰电压或直流高电压击穿。

[0018]

本实用新型还提供了一种电池充电电路,包括上述的单晶圆电池保护电路、充电器、电池以及rc滤波电路,其中:

[0019]

所述第一电阻的一端与所述基本保护电路的供电电压端连接,所述第一电阻的另一端与所述电池的正极连接;

[0020]

所述第一电容的一端与所述基本保护电路的供电电压端连接,所述第一电容的另一端与所述电池的负极连接;

[0021]

所述充电器的正极与所述电池的正极连接,为所述电池提供充电电压。

[0022]

本实用新型还提供了一种电池放电电路,包括上述的单晶圆电池保护电路、rc滤波电路、电池以及负载,其中:

[0023]

所述第一电阻的一端与所述基本保护电路的供电电压端连接,所述第一电阻的另一端与所述电池的正极连接;

[0024]

所述第一电容的一端与所述基本保护电路的供电电压端连接,所述第一电容的另一端与所述电池的负极连接;

[0025]

所述电池的正极与所述负载的正极连接,为所述负载提供电源,所述负载的负极通过充放电控制mos管与所述电池的负极连接。

[0026]

本申请还提供了一种便携式电子设备,包括单晶圆以及上述的单晶圆电池保护电路。其中,便携式电子设备可以为具有锂电池的设备,例如手机、玩具、移动电源、电子烟、蓝牙耳机(tws)等。

[0027]

通过本实用新型提供的一种单晶圆电池保护电路、电池充放电电路及便携式电子设备,能够带来以下至少一种有益效果:

[0028]

本实用新型中,利用钳压电路,将栅极衬底控制电路的供电电压gvdd与vss端之间的电压钳制在预设范围内。提高电池保护电路芯片在生产测试过程中以及充放电使用时的耐压,防止电池保护电路中的器件损坏。其中,过温保护电路用于检测单晶圆电池保护电路所集成芯片的温度,并同基本保护电路共同控制导通栅极衬底控制电路。

附图说明

[0029]

下面将以明确易懂的方式,结合附图说明优选实施方式,对一种提高抗尖峰电压能力的单晶圆电池保护电路及充放电电路的上述特性、技术特征、优点及其实现方式予以进一步说明。

[0030]

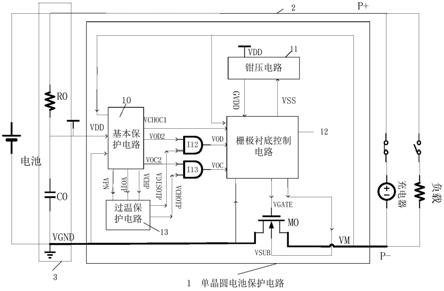

图1是传统分立器件电池保护电路的充电及放电电路结构图;

[0031]

图2是现有单晶圆电池保护电路的充电及放电电路结构图;

[0032]

图3是现有单晶圆电池保护方案技术中栅极衬底控制电路的一种电路图;

[0033]

图4是本实用新型一种提高抗尖峰电压能力的单晶圆电池保护电路及充放电电路结构图的一实施例;

[0034]

图5是图4中的基本保护电路的结构图;

[0035]

图6是图4中的过温保护电路的电路图;

[0036]

图7是图4中的栅极衬底控制电路的一种电路图;

[0037]

图8是图4中的栅极衬底控制电路的另一种电路图;

[0038]

图9是本实用新型一实施例中的钳压电路的一种电路图;

[0039]

图10是本实用新型一实施例中的钳压电路的另一种电路图;

[0040]

图11是本实用新型一实施例中的钳压电路的另一种电路图;

[0041]

图12是本实用新型一实施例中的钳压电路的另一种电路图。

具体实施方式

[0042]

为了更清楚地说明本实用新型实施例或现有技术中的技术方案,下面将对照附图说明本实用新型的具体实施方式。显而易见地,下面描述中的附图仅仅是本实用新型的一

些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图,并获得其他的实施方式。

[0043]

为使图面简洁,各图中只示意性地表示出了与本实用新型相关的部分,它们并不代表其作为产品的实际结构。另外,以使图面简洁便于理解,在有些图中具有相同结构或功能的部件,仅示意性地绘示了其中的一个,或仅标出了其中的一个。在本文中,“一个”不仅表示“仅此一个”,也可以表示“多于一个”的情形。

[0044]

图1为传统的分立器件电池保护方案的充放电电路。控制电路a通过控制两个功率mos管(mc和md)的栅极电压来实现对电池的充放电控制。控制电路a是用cmos工艺做成,而功率mos管(mc和md)通常用一种垂直结构的dmos或umos管做成。由于cmos和dmos/umos是两种完全不同的工艺,因此控制电路a和两个功率mos管(mc和md)通常来自于两个不同的供应商,是两个独立的芯片,外围电路需要两个电阻r0和rvm以及一个电容c0。

[0045]

图2为单晶圆电池保护方案技术中电池保护电路的内部框图及充放电电路。当电池保护电路进入过充电压保护、充电过流保护或充电过温保护时,电池保护电路的充电通路被关闭,充电器的电压完全由外部充电电路提供。电池保护电路内部的基本保护电路、过温保护电路、逻辑控制单元i12、逻辑控制单元i13是电池供电,没有高电压,电路不会被高压打坏。但栅极衬底控制电路在充电保护时的供电电压为充电器电压,在生产测试过程中以及充电器接入过程中,这个电压可能达到16v的高压,则会损坏栅极衬底控制电路,同时还可能会损坏充放电控制mos管m0。

[0046]

图3是现有单晶圆电池保护方案技术中栅极衬底控制电路的电路图。

[0047]

参照图3所示,包括输出vgate的栅极控制电路和输出vsub的衬底控制电路,由于栅极控制电路的低电平vss电压和vgnd电压不是完全一样的电位,栅极控制电路输入的vod电压、voc电压、vchoc1电压的低电位是vgnd电压、需要转换成vss电压。vod电压、voc电压、vchoc1电压都需要一个电平转换电路,下面以vod电压的电平转换电路为例说明。

[0048]

mos管m7、m8、m9、m10、逻辑控制单元i6完成vod电压的低电平转换。当vod电压为高电平vdd时,晶体管m7截至、晶体管m8导通,vodp电压为高电平vdd;当vod电压为低电平vgnd时,晶体管m7导通、晶体管m8截至,vodp电压为低电平vss,完成从vgnd电平到vss电平的转换。同理voc电压转换成vocp电压、vchoc1电压转换成vchoc1p电压、vchoc1n电压。当vodp电压、vocp电压都为高电平时,vgate端输出为高电平vdd,当vodp电压、vocp电压中有一个为低电平vss时,vgate端输出为低电平vss。当vocp为高电平,vgoc为低电平、vgocb为高电平、mos管m1导通、mos管m2截止、输出vsub电压等于vgnd电压;当vocp为低电平,vgoc为高电平、vgocb为低电平、mos管m1截止、mos管m2导通、输出vsub电压等于vm电压。vchoc1电压为高时,vchoc1p电压为高,vchoc1n电压为低,mos管m19导通、mos管m20截止,vss电压等于vgnd电压;vchoc1电压为低时,vchoc1p电压为低,vchoc1n电压为高,mos管m19截止、mos管m20导通,vss电压等于vm电压。

[0049]

上面描述中当vchoc1p电压为低电平时,vss电压等于vm电压,则vdd电压与vss电压之间的压差为vdd电压与vm电压之间压差,在生产测试过程及充放电使用时vdd与vm之间电压可能会产生高达16v的尖峰电压或直流电压,而5v cmos工艺mos管击穿电压在8v至12v之间,低于产生的尖峰电压或直流电压,则现有栅极衬底控制电路会被损坏或击穿。

[0050]

基于上述分析结论,本实用新型提供一种新的电池保护电路。图4是本实用新型一

实施例中的单晶圆电池保护电路及充放电电路的结构图。图5是图4中的基本保护电路的结构图。图6是图4中的过温保护电路的电路图。图7是图4中的栅极衬底控制电路的一种电路图,图8是图4中的栅极衬底控制电路的另一种电路图。如图7、图8所示,栅极衬底控制电路包括栅极控制部分和衬底控制部分,栅极控制部分和衬底控制部分具有共用电路。参照图4至图7所示,相对于图2中的电池保护电路与图3中的栅极衬底控制电路,增加了钳压电路以及改进了栅极衬底控制电路。图4中,当电池保护电路进入过充电压保护、充电过流保护或充电过温保护时,电池保护电路的充电通路被关闭,充电器的电压完全由外部充电电路提供。参照图7所示,改进后的栅极衬底控制电路的正电源端为钳压电路的输出电压gvdd、电池保护电路进入过充电压保护、充电过流保护或充电过温保护时,负电源端vss电压为vm,除此之外负电源端vss电压为vgnd。栅极衬底控制电路的供电电压为gvdd与vm之间的电压或gvdd与vgnd之间的电压,该供电电压被钳位,低于栅极衬底控制电路内部所有mos管的击穿电压,栅极衬底控制电路不会损坏。

[0051]

参照图4所示,电池充放电电路2包括电池、rc滤波电路3、单晶圆电池保护电路1、充电器以及负载,电池与rc滤波电路3、充电器、负载并联连接;其中单晶圆电池保护电路1、充电器、电池、rc滤波电路3组成电池充电电路;单晶圆电池保护电路1、rc滤波电路3、电池、负载组成电池放电电路。

[0052]

电池充电电路包括单晶圆电池保护电路1、充电器、电池、rc滤波电路3,其中:rc滤波电路3中第一电阻r0的一端与基本保护电路10的供电电压vdd端连接,第一电阻r0的另一端与电池的正极连接;rc滤波电路3中第一电容c0的一端与基本保护电路10的供电电压vdd端连接,第一电容c0的另一端与电池的负极连接;充电器的正极在充电时与电池的正极连接,为电池提供充电电压,充电器的负极通过充放电控制mos管m0与电池的负极连接。

[0053]

电池放电电路包括单晶圆电池保护电路1、rc滤波电路3、电池、负载,其中:rc滤波电路3中第一电阻r0的一端与基本保护电路10的供电电压vdd端连接,第一电阻r0的另一端与电池的正极连接;rc滤波电路3中第一电容c0的一端与基本保护电路10的供电电压vdd端连接,第一电容c0的另一端与电池的负极连接;电池的正极与负载的一端连接,为负载提供电源,电池的负极通过充放电控制mos管m0与负载的另一端连接。

[0054]

单晶圆电池保护电路1包括:基本保护电路10、钳压电路11、栅极衬底控制电路12、过温保护电路13、第一逻辑控制单元i12、第二逻辑控制单元i13、充放电控制mos管m0;基本保护电路10的供电电压vdd输入端连接至第一电阻r0和第一电容c0之间;基本保护电路10的输出端耦接栅极衬底控制电路12。过温保护电路13的输入端与基本保护电路10连接;基本保护电路10的输出端分别与过温保护电路13的输出端通过第一逻辑控制单元i12、第二逻辑控制单元i13耦接栅极衬底控制电路12;钳压电路11耦接供电电压vdd,钳压电路11与栅极衬底控制电路12耦接。充放电控制mos管m0的源极和漏极的一端连接至电池负极,充放电控制mos管m0的源极和漏极的另一端连接至充电器或负载的负极,例如充放电控制mos管m0的源极连接充电器的负极,充放电控制mos管m0的漏极连接电池的负极;充放电控制mos管m0的栅极和衬底分别连接至栅极衬底控制电路12;充放电控制mos管m0的源极连接基本保护电路10和栅极衬底控制电路12,充放电控制mos管m0的漏极连接基本保护电路10和栅极衬底控制电路12。

[0055]

本实施例的单晶圆电池保护电路1通过基本保护电路10检测电池的充放电情况,

向栅极衬底控制电路12发送控制信号,使栅极衬底控制电路12根据控制信号控制充放电控制mos管m0的导通情况,从而对电池的充放电进行控制。单晶圆电池保护电路1通过过温保护电路13检测电池保护电路所集成芯片的温度,过温保护电路13同基本保护电路10共同控制导通栅极衬底控制电路12。单晶圆电池保护电路1通过钳压电路11钳制栅极衬底控制电路12的供电电压,保证单晶圆电池保护电路1不被损坏。

[0056]

如图9所示,是本申请实施例中钳压电路11的一种电路图。钳压电路11包括分压电阻r5和n个单向串联的齐纳管(zener),n≥1;分压电阻r5的一端接收供电电压vdd,分压电阻r5的另一端连接n个单向串联的齐纳管(zener)的负极和栅极衬底控制电路12的输入端gvdd,n个单向串联的齐纳管(zener)的正极耦接至栅极衬底控制电路12的输入端vss。

[0057]

本实施例的钳压电路11能将栅极衬底控制电路12的输入电压gvdd与vss之间的电压钳制在一预设范围内的原理在于:齐纳管(zener)的pn结在反向击穿状态时电阻极低,因而在齐纳管(zener)导通时,输入电压gvdd与vss之间的电压等于齐纳管(zener)的击穿电压;在齐纳管(zener)不导通时,输入电压gvdd几乎等于供电电压vdd。

[0058]

当vdd与vss之间的电压低于齐纳管(zener)的导通电压,输入电压gvdd等于供电电压vdd;当vdd与vss之间的电压高于齐纳管(zener)的导通电压时,输入电压gvdd与vss之间的最高输出电压为齐纳管(zener)电压。一般集成电路内部齐纳管(zener)的导通电压为5.5v至6.5v之间,如果vdd与vss之间的电压持续增加,一个或多个齐纳管(zener)串联钳压,齐纳管(zener)电压稳定在齐纳管(zener)的导通电压,其余的电压都降在分压电阻r5上,分压电阻r5的阻值大于或等于0,分压电阻r5上压降几十伏都不会有问题;因此供电电压vdd与vss之间的耐压高达几十伏都不会损害钳压电路11。vss连接栅极衬底电路12的低电位。将vdd与vss之间的电压箝位在一个或多个齐纳管(zener)电压值。栅极衬底控制电路12的供电电压为gvdd与vss之间的电压,最大值为齐纳管(zener)的导通电压。低于mos管m0的击穿电压8v至12v之间,因此栅极衬底控制电路12不会被损坏。

[0059]

如图10所示,是本申请实施例中钳压电路11的另一种电路图,与图9不同之处在于:钳压电路11包括分压电阻r5和n个单向串联的二极管,n≥1;分压电阻r5的一端接收供电电压vdd,分压电阻r5的另一端连接n个单向串联的二极管的正极和栅极衬底控制电路12的输入端gvdd,n个单向串联的二极管的负极耦接至栅极衬底控制电路12的输入端vss。

[0060]

本实施例的钳压电路11通过多个二极管串联能将栅极衬底控制电路12的输入电压gvdd与vss之间的电压钳制在预设范围内的原理在于:利用二极管正向导通电压缓变特性,在二极管导通时,输入电压gvdd与vss之间的电压等于多个二极管的导通电压之和;二极管不导通时,输入电压gvdd几乎等于供电电压vdd。

[0061]

如图11所示,是本申请实施例中钳压电路11的另一种电路图,与图9不同之处在于:钳压电路11包括分压电阻r5和n个串联的nmos管,n≥1;分压电阻r5的一端接收供电电压vdd,分压电阻r5的另一端连接n个串联的nmos管的一端和栅极衬底控制电路12的输入端gvdd,n个串联的nmos管的另一端耦接至栅极衬底控制电路12的输入端vss。

[0062]

本实施例的钳压电路11通过多个nmos串联能将栅极衬底控制电路12的输入电压gvdd与vss之间的电压钳制在预设范围内的原理在于:nmos的源极和栅极短接在一起,nmos等效为一个二极管,正向导通电压为nmos的阈值电压vthn。因此在nmos导通时,输入电压gvdd等于多个nmos的阈值电压之和;nmos不导通时,输入电压gvdd几乎等于供电电压vdd。

[0063]

如图12所示,是本申请实施例中钳压电路11的另一种电路图,与图9不同之处在于:钳压电路11包括分压电阻r5和n个串联的pmos管,n≥1;分压电阻r5的一端接收供电电压vdd,分压电阻r5的另一端连接n个串联的pmos管的一端和栅极衬底控制电路12的输入端gvdd,n个串联的pmos管的另一端耦接至栅极衬底电路12的输入端vss。

[0064]

本实施例的钳压电路11通过多个pmos串联能将栅极衬底控制电路12的输入电压gvdd与vss之间的电压钳制在预设范围内的原理同多个nmos串联将gvdd与vss之间的电压钳制在预设范围内的原理。

[0065]

如图5所示,是图4中单晶圆电池保护电路1中的基本保护电路10的电路图,包括:基准电路、放电过流比较器、放电短路比较器、充电过流比较器、过放电压比较器、过充电压比较器、延时电路、充放电检测电路、第二电阻r1、第三电阻r2、第四电阻r3、第五电阻r4、第六逻辑控制单元i0、第七逻辑控制单元i1、第八逻辑控制单元i2、第九逻辑控制单元i3、以及第十逻辑控制单元i4。

[0066]

基准电路的输出端分别与放电过流比较器的第一输入端(正向输入端)、放电短路比较器的第一输入端(正向输入端)、充电过流比较器的第二输入端(负向输入端)、过放电压比较器的第二输入端(负向输入端)和过充电压比较器的第一输入端(正向输入端)连接;放电过流比较器的第二输入端(负向输入端)、放电短路比较器的第二输入端(负向输入端)、充电过流比较器的第一输入端(正向输入端)和充放电检测电路的第二输入端(负向输入端)分别通过第五电阻r4与充放电控制mos管m0的源极或漏极连接;第二电阻r1的一端连接供电电压vdd,第二电阻r1的另一端连接过放电压比较器的第一输入端(正向输入端)和第三电阻r2的一端;第三电阻r2的另一端连接过充电压比较器的第二输入端(负向输入端)和第四电阻r3的一端,第四电阻r3的另一端连接充放电检测电路的第一输入端(正向输入端)和接地;放电过流比较器的输出端、放电短路比较器的输出端、充电过流比较器的输出端、过放电压比较器的输出端、过充电压比较器的输出端分别与延时电路连接;充电过流比较器的输出端分别连接延时电路和栅极衬底控制电路12;充放电检测电路的输出端连接过温比较电路13的输入端。

[0067]

延时电路的输出端通vdoc1、vdshort以及vdodv过第六逻辑控制单元i0连接第八逻辑控制单元i2的第一输入端;充放电检测电路的输出端连接第八逻辑控制单元i2的第二输入端;第八逻辑控制单元i2的输出端耦接栅极衬底控制电路12;延时电路的输出端vdchoc和vdocv通过第七逻辑控制单元i1连接第九逻辑控制单元i3的第一输入端;充放电检测电路的输出端连接第十逻辑控制单元i4的输入端;第十逻辑控制单元i4的输出端连接第九逻辑控制单元i3的第二输入端;第九逻辑控制单元i3的输出端耦接栅极衬底控制电路12。

[0068]

其中,基准电路用于产生放电过流比较器的正输入信号voc1、放电短路比较器的正输入信号vshort、充电过流比较器的负输入信号vchoc、参考输出电压vpn、votp、过充电压比较器的正输入信号vocv、以及产生过放电压比较器的负输入信号vodv。

[0069]

放电过流比较器基于正输入信号voc1与负输入信号虚拟接地电压vm1的大小比较结果,voc1大于vm1时输出高电平vdd,voc1低于vm1时输出低电平vgnd。

[0070]

放电短路比较器基于正输入信号vshort与负输入信号虚拟接地电压vm1的大小比较结果,vshort大于vm1时输出高电平vdd,vshort低于vm1时输出低电平vgnd。

[0071]

充电过流比较器基于正输入信号虚拟接地电压vm1与负输入信号vchoc的大小比较结果,vm1大于vchoc时输出高电平vdd,vm1低于vchoc时输出低电平vgnd。

[0072]

过充电压比较器基于正输入信号vocv与供电电压vdd经过电阻分压后的负输入信号vrocv的大小比较结果,输出高电平vdd或低电平vgnd。

[0073]

过放电压比较器基于供电电压vdd经过电阻分压后的正输入信号vrodv与负输入信号vodv的大小比较结果,输出高电平vdd或低电平vgnd。

[0074]

充放电检测电路基于正输入信号vgnd与负输入信号虚拟接地电压vm1的大小比较结果,输出高电平vdd或低电平vgnd。正输入信号vgnd大于负输入信号虚拟接地电压vm1时输出高电平vdd,正输入信号vgnd低于负输入信号虚拟接地电压vm1时输出低电平vgnd。

[0075]

延时电路用于对放电过流比较器的输出信号voc1p、放电短路比较器的输出信号vshortp、充电过流比较器的输出信号vchoc1、过放电压比较器的输出信号vodvp、过充电压比较器的输出信号vocvp进行延时,延时后对应输出vdoc1、vdshort、vdchoc、vdodv、vdocv。vdoc1为voc1p经过延时的信号,vdshort是vshortp经过延时的信号、vdchoc是vchoc1经过延时的信号、vdodv是vodvp进过延时的信号、vdocv是vocvp经过延时的信号。

[0076]

当vdoc1、vdshort、vdodv都为高时,第六逻辑控制单元i0输出信号vod3输出为高电平vdd,vdoc1、vdshort、vdodv中至少一个为低时,第六逻辑控制单元i0输出信号vod3输出为低电平vgnd。

[0077]

当vdchoc、vdocv都为高时,第七逻辑控制单元i1输出信号voc3输出为高电平vdd。vdchoc、vdocv中至少一个为低时,第七逻辑控制单元i1输出信号voc3输出为低电平vgnd。

[0078]

当第六逻辑控制单元i0输出信号vod3、充放电检测电路输出信号vchp中至少一个为高时,第八逻辑控制单元i2输出信号vod2输出为高电平vdd。当vod3、vchp都为低时,vod2输出为低电平vgnd。

[0079]

当第七逻辑控制单元i1输出信号voc3、第十逻辑控制单元i4输出信号vchn中至少一个为高时,第九逻辑控制单元i3输出信号voc2输出为高电平vdd。当第七逻辑控制单元i1输出信号voc3、第十逻辑控制单元i4输出信号vchn中都为低时,第九逻辑控制单元i3输出信号voc2输出为低电平vgnd。

[0080]

本实施例的基本保护电路10检测电池的充放电情况,向栅极衬底控制电路12发送控制信号,使栅极衬底控制电路12根据控制信号控制充放电控制mos管m0的导通情况,从而对电池的充放电进行控制。

[0081]

如图6所示,是图4中单晶圆电池保护电路1中的过温保护电路13的电路。

[0082]

过温保护电路13包括过温比较器、第三逻辑控制i14、第四逻辑控制单元i15和第五逻辑控制单元i16。

[0083]

过温比较器的输入端与基本保护电路10连接,过温比较电路13的输出端分别与第四逻辑控制单元i15的第一输入端和第五逻辑单元i16的第二输入端连接,第四逻辑控制单元i15的第二输入端与第三逻辑控制单元i14的输出端连接,第五逻辑控制单元i16的第一输入端和第三逻辑控制单元i14的输入端与基本保护电路10连接,第四逻辑控制单元i15的输出端和第五逻辑控制单元i16的输出端耦接栅极衬底控制电路12。具体地,第四逻辑控制单元i15的输出端vchotp通过第二逻辑控制单元i13耦接栅极衬底控制电路12,第五逻辑控制单元i16的输出端vdisotp通过第一逻辑控制单元耦接栅极衬底控制电路12。

[0084]

过温比较器基于正输入端电压vpn与负输入端电压votp的大小比较结果,正输入端电压vpn大于负输入端电压votp时输出高电平,正输入端电压vpn小于负输入端电压votp时输出低电平。

[0085]

当过温比较器输出电压votpp、第三逻辑控制单元i14输出电压vchn1中至少一个为高时,第四逻辑控制单元i15输出电压vchotp输出为高电平vdd。当过温比较器输出电压votpp、第三逻辑控制单元i14输出电压vchn1都为低时,第四逻辑控制单元i15输出电压vchotp输出为低。

[0086]

当过温比较器输出电压votpp、第三逻辑控制单元i14输入电压vchp中至少一个为高时,第五逻辑控制单元i16输出电压vdisotp输出为高电平vdd。当过温比较器输出电压votpp、第三逻辑控制单元i14输入电压vchp都为低时,第五逻辑控制单元i16输出电压vdisotp输出为低。

[0087]

本实施例的过温保护电路13用于检测单晶圆电池保护电路1所集成芯片的温度,并同基本保护电路10共同控制导通栅极衬底控制电路12。

[0088]

如图7所示,是图4中单晶圆电池保护电路1中的栅极衬底控制电路12的一种电路示意图。

[0089]

相对图3的栅极衬底控制电路,不同之处在于,栅极衬底控制电路12进一步的还包括电阻r11、r12、r13、r14、r15、r16和mos管m21、m22、m23、m24、m25、m26。

[0090]

栅极衬底控制电路12包括栅极控制部分和衬底控制部分,栅极控制部分和衬底控制部分具有共用电路;

[0091]

栅极控制部分包括电阻r11、r12、r13、r14、r15、r16和mos管m7、m8、m9、m10、m11、m12、m13、m14、m15、m16、m17、m18、m19、m20、m21、m22、m23、m24、m25、m26和逻辑控制单元i6、i7、i8、i9;

[0092]

电阻r11一端接入第一逻辑控制单元i12输出电压vod;电阻r11另一端连接mos管m7的栅极、逻辑控制单元i6的输入端、mos管m21的漏极;mos管m21的源极连接mos管m21的栅极、mos管m21的衬底、钳压电路11的输出端gvdd、mos管m7的衬底、mos管m7的源极、mos管m8的衬底、mos管m8的源极、mos管m22的栅极、mos管m22的衬底、mos管m22的源极;电阻r12一端连接mos管m22的漏极和mos管m8的栅极;电阻r12另一端连接逻辑控制单元i6的输出端;mos管m7的漏极连接mos管m9的漏极和mos管m10的栅极;mos管m8的漏极连接mos管m9的栅极、mos管m10的漏极和逻辑控制单元i9的第一输入端;逻辑控制单元i9的输出端连接充放电控制mos管m0的栅极;mos管m9的源极、mos管m9的衬底、mos管m10的源极、mos管m10的衬底、mos管m13源极、mos管m13的衬底、mos管m14的源极、mos管m14的衬底、mos管m17的源极、mos管m17的衬底、mos管m18的源极、mos管m18的衬底连接在一起,并连接mos管m19的源极、mos管m19的衬底和mos管m20的源极、mos管m20的衬底;mos管m19的漏极连接充放电控制mos管m0的源极或漏极的一端和电池负极;mos管m20的漏极连接充放电控制mos管m0的源极或漏极的另一端和充电器负极;

[0093]

电阻r13一端接入第二逻辑控制单元i13输出电压voc;电阻r13另一端连接mos管m11的栅极、逻辑控制单元i7的输入端、mos管m23的漏极;mos管m23的源极连接mos管m23的栅极、mos管m23的衬底、mos管m11的源极、mos管m11的衬底、钳压电路11的输出端gvdd、mos管m12的衬底、mos管m12的源极、mos管m24的栅极、mos管m24的源极、mos管m24的衬底;电阻

r14一端连接mos管m24的漏极和mos管m12的栅极;电阻r14另一端连接逻辑控制单元i7的输出端;mos管m11的漏极的连接mos管m13的漏极和mos管m14的栅极;mos管m12的漏极连接mos管m13的栅极、mos管m14的漏极、逻辑控制单元i9的第二输入端和逻辑控制单元i10的输入端;

[0094]

电阻r15一端接入基本保护电路10输出电压vchoc1;电阻r15另一端连接mos管m15的栅极、逻辑控制单元i8的输入端、mos管m25的漏极;mos管m25的源极连接mos管m25的栅极、mos管m25的衬底、mos管m15的源极、mos管m15的衬底、钳压电路11的输出端gvdd、mos管m16的衬底、mos管m16的源极、mos管m26的栅极、mos管m26的源极、mos管m26的衬底;电阻r16一端连接mos管m26的漏极和mos管m16的栅极;电阻r16另一端连接逻辑控制单元i8的输出端;mos管m15的漏极连接mos管m17的漏极、mos管m18的栅极和mos管m20的栅极;mos管m16的漏极连接mos管m17的栅极、mos管m18的漏极和mos管m19的栅极。

[0095]

衬底控制部分包括电阻r13、r14、r15、r16和mos管m1、m2、m11、m12、m13、m14、m15、m16、m17、m18、m19、m20、m23、m24、m25、m26和逻辑控制单元i7、i8、i10、i11;

[0096]

逻辑控制单元i10输入端连接逻辑控制单元i9的第二输入端、mos管m12的漏极、mos管m13的栅极和mos管m14的漏极;逻辑控制单元i10输出端连接逻辑控制单元i11输入端和mos管m2的栅极;逻辑控制单元i11输出端连接mos管m1的栅极;mos管m1的漏极连接mos管m19的漏极和充放电控制mos管m0的源极或漏极的一端和电池负极;mos管m1的源极、mos管m1的衬底、mos管m2的源极、mos管m2的衬底连接在一起,并连接充放电控制mos管m0的衬底;mos管m2的漏极连接mos管m20的漏极、充放电控制mos管m0的源极或漏极的另一端和充电器负极。

[0097]

下面以r11、r12、m21、m22说明加入电阻和mos管的作用:由于增加了钳压电路11,栅极衬底控制电路12的正电源电压为钳压电路11的输出电位gvdd,而输入电压vod可能为高电平vdd或低电平vgnd,输入电压gvdd与供电电压vdd之间的电压,输入电压gvdd与供电电压vgnd之间的电压可能超过mos管m7、m8的栅极击穿电压从而损坏mos管m7、m8,加入r11、m21、r12、m22后m7、m8的gate到gvdd的最大电压为m21、m22寄生的二极管电压,该寄生二极管电压不会损坏mos管。同理:r13、r14、m23、m24保护m11、m12不受损坏;r15、r16、m25、m26保护m15、m16不受损坏。

[0098]

本实施例的栅极衬底控制电路12包括栅极控制部分和衬底控制部分;栅极控制部分与充放电控制mos管m0的栅极连接,衬底控制部分与充放电控制mos管m0的衬底连接;当电池充放电时,栅极控制部分根据控制信号输出栅极控制响应信号,控制充放电控制mos管m0的栅极电压,衬底控制部分根据控制信号输出衬底控制响应信号,控制充放电控制mos管m0的衬底电压,从而控制充放电控制mos管m0的导通情况。

[0099]

如图8所示,相对图3的栅极衬底控制电路,不同之处在于,栅极衬底控制电路12进一步的还包括电阻r11、r12、r13、r14、r15、r16和二极管d3、d4、d5、d6、d7、d8,实现图9中同样的功能。

[0100]

栅极衬底控制电路12包括栅极控制部分和衬底控制部分,栅极控制部分和衬底控制部分具有共用电路;

[0101]

栅极控制部分包括电阻r11、r12、r13、r14、r15、r16和mos管m7、m8、m9、m10、m11、m12、m13、m14、m15、m16、m17、m18、m19、m20和二极管d3、d4、d5、d6、d7、d8和逻辑控制单元i6、

i7、i8、i9;

[0102]

电阻r11一端接入第一逻辑控制单元i12输出电压vod;电阻r11另一端连接mos管m7的栅极、逻辑控制单元i6的输入端、二极管d3的正极;二极管d3的负极连接mos管m7的衬底、mos管m7的源极、钳压电路11的输出端gvdd、mos管m8的衬底、mos管m8的源极、二极管d4的负极;电阻r12一端连接二极管d4的正极和mos管m8的栅极;电阻r12另一端连接逻辑控制单元i6的输出端;mos管m7的漏极连接mos管m9的漏极和mos管m10的栅极;mos管m8的漏极连接mos管m9的栅极、mos管m10的漏极和逻辑控制单元i9的第一输入端;逻辑控制单元i9的输出端连接充放电控制mos管m0的栅极;mos管m9的源极、mos管m9的衬底、mos管m10的源极、mos管m10的衬底、mos管m13源极、mos管m13的衬底、mos管m14的源极、mos管m14的衬底、mos管m17的源极、mos管m17的衬底、mos管m18的源极、mos管m18的衬底连接在一起,并连接mos管m19的源极、mos管m19的衬底和mos管m20的源极、mos管m20的衬底;mos管m19的漏极连接充放电控制mos管m0的源极或漏极的一端和电池负极;mos管m20的漏极连接充放电控制mos管m0的源极或漏极的另一端和充电器负极;

[0103]

电阻r13一端接入第二逻辑控制单元i13输出电压voc;电阻r13另一端连接mos管m11的栅极、逻辑控制单元i7的输入端、二极管d5的正极;二极管d5的负极连接mos管m11的衬底、mos管m11的源极、钳压电路11的输出端gvdd、mos管m12的衬底、mos管m12的源极、二极管d6的负极;电阻r14一端连接二极管d6的正极和mos管m12的栅极;电阻r14另一端连接逻辑控制单元i7的输出端;mos管m11的漏极连接mos管m13的漏极和mos管m14的栅极;mos管m12的漏极连接mos管m13的栅极、mos管m14的漏极、逻辑控制单元i9的第二输入端和逻辑控制单元i10的输入端;

[0104]

电阻r15一端接入基本保护电路10输出电压vchoc1;电阻r15另一端连接mos管m15的栅极、逻辑控制单元i8的输入端、二极管d7的正极;二极管d7的负极连接mos管m15的衬底、mos管m15的源极、钳压电路11的输出端gvdd、mos管m16的衬底、mos管m16的源极、二极管d8的负极;电阻r16一端连接二极管d8的正极和mos管m16的栅极;电阻r16另一端连接逻辑控制单元i8的输出端;mos管m15的漏极连接mos管m17的漏极、mos管m18的栅极和mos管m20的栅极;mos管m16的漏极连接mos管m17的栅极、mos管m18的漏极和mos管m19的栅极。

[0105]

衬底控制部分包括电阻r13、r14、r15、r16和mos管m1、m2、m11、m12、m13、m14、m15、m16、m17、m18、m19、m20和二极管d5、d6、d7、d8和逻辑控制单元i7、i8、i10、i11。

[0106]

逻辑控制单元i10输入端连接逻辑控制单元i9的第二输入端、mos管m12的漏极、mos管m13的栅极和mos管m14的漏极;逻辑控制单元i10输出端连接逻辑控制单元i11输入端和mos管m2的栅极;逻辑控制单元i11输出端连接mos管m1的栅极;mos管m1的漏极连接mos管m19的漏极和充放电控制mos管m0的源极或漏极的一端和电池负极;mos管m1的源极、mos管m1的衬底、mos管m2的源极、mos管m2的衬底连接在一起,并连接充放电控制mos管m0的衬底;mos管m2的漏极连接mos管m20的漏极、充放电控制mos管m0的源极或漏极的另一端和充电器负极。

[0107]

申请还提供一种便携式电子设备,其包括单晶圆和上述实施例所揭示的单晶圆电池保护电路1,便携式电子设备可以为具有锂电池的设备,例如手机、玩具、移动电源、电子烟、蓝牙耳机(tws)等。

[0108]

应当说明的是,上述实施例均可根据需要自由组合。以上所述仅是本实用新型的

优选实施方式,应当指出,对于本技术领域的普通技术人员来说,在不脱离本实用新型原理的前提下,还可以做出若干改进和润饰,这些改进和润饰也应视为本实用新型的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1