一种应用于框架断路器的可充电实时时钟电路的制作方法

1.本实用新型涉及一种时钟电路,尤其是涉及一种应用于框架断路器的可充电实时时钟电路。

背景技术:

2.框架断路器中的实时时钟作为框架断路器的一部分,为系统提供准确的时间基准,所有事件,故障的记录,都需要准确的发生时间。目前的实时时间大都采用实时时钟芯片获得,在系统掉电时,通过外加电池,保持实时时钟的正常运行.

3.现有的时钟电路系统断电时,由纽扣电池提供电能,维持芯片正常运行。此方案价格低廉,稳定可靠,但当纽扣电池电能耗尽后,若系统断电重启,实时时钟便会重置时间,引发错误。并需要重新更换电池并重新校时,对于框架断路器而言,需要定期维护,定期更换,无疑增加了维护成本。

技术实现要素:

4.本实用新型的目的就是为了克服上述现有技术存在的缺陷而提供一种应用于框架断路器的可充电实时时钟电路。

5.本实用新型的目的可以通过以下技术方案来实现:

6.一种应用于框架断路器的可充电实时时钟电路,包括电源、时钟芯片、晶振、备用电源和充电管理模块,所述的电源分别与时钟芯片和充电管理模块的输入端电连接,所述的充电管理模块的输出端与备用电源电连接,所述的晶振和备用电源分别与时钟芯片电连接。

7.优选地,所述的充电管理模块包括tp4054充电芯片和电阻r1,所述的tp4054充电芯片的vdd引脚与电源连接,所述的tp4054充电芯片的vbat引脚与备用电源的正极连接,所述的tp4054充电芯片的vss引脚接地,所述的电阻r1的一端与tp4054充电芯片的prog引脚连接,另一端与备用电源的负极连接并接地。

8.优选地,所述的备用电源为可充电纽扣电池。

9.优选地,所述的时钟电路还包括二极管d1,所述的二极管d1的正极与电源连接,所述的二极管d1的负极与时钟芯片连接。

10.优选地,所述的时钟电路还包括二极管d2,所述的二极管d2的正极与备用电源连接,所述的二极管d2的负极与时钟芯片连接。

11.优选地,所述的晶振的频率为32.768khz。

12.优选地,所述的时钟芯片为pcf8563时钟芯片。

13.优选地,所述的pcf8563时钟芯片的vcc引脚分别与电源和备用电源电连接,所述的pcf8563时钟芯片的x1引脚连接晶振的一端,所述的pcf8563时钟芯片的x2引脚连接晶振的另一端,所述的框架断路器包括主控芯片,所述的pcf8563时钟芯片的scl引脚与主控芯片的scl引脚连接,所述的pcf8563时钟芯片的sda引脚与主控芯片的sda引脚连接。

14.优选地,所述电源的电压为5v。

15.优选地,所述的电阻r1的阻值范围为大于等于20k欧姆且小于等于100k欧姆。

16.本实用新型的时钟电路工作时,若电源正常工作,由电源为时钟芯片供电,并由电源通过充电管理模块为备用电源充电,若电源断电,则由备用电源为时钟芯片供电。

17.与现有技术相比,本实用新型具有如下优点:

18.(1)本实用新型采用充电管理芯片与可充电纽扣电池配合的形式,电源正常工作时,电源通过充电管理芯片为可充电纽扣电池充电,当电源断电后,能够利用可充电纽扣电池为时钟芯片供电,避免现有时钟电路的备用电池损耗完后,时钟掉电会重置,需要开壳更换电池的情况,有效降低维护成本;

19.(2)本实用新型利用tp4054充电芯片对备用电池进行充电,提高充电的稳定性和安全性,提高备用电池的使用寿命;

20.(3)采用本实用新型时钟电路的框架断路器,能够在系统掉电、备用电池电能耗尽后,无需更换电池并重新校准时间,降低框架断路器的维护成本。

附图说明

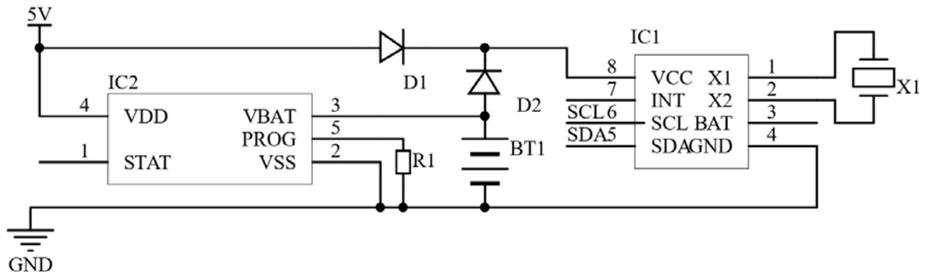

21.图1为本实用新型的电路结构图。

具体实施方式

22.下面结合附图和具体实施例对本实用新型进行详细说明。注意,以下的实施方式的说明只是实质上的例示,本实用新型并不意在对其适用物或其用途进行限定,且本实用新型并不限定于以下的实施方式。

23.实施例

24.一种应用于框架断路器的可充电实时时钟电路,如图1所示,包括电源、时钟芯片、晶振、备用电源和充电管理模块,电源分别与时钟芯片和充电管理模块的输入端电连接,充电管理模块的输出端与备用电源电连接,晶振和备用电源分别与时钟芯片电连接。

25.具体地,充电管理模块包括tp4054充电芯片和电阻r1,备用电源为可充电纽扣电池,时钟电路还包括二极管d1和二极管d2。tp4054充电芯片的vdd引脚与电源连接,tp4054充电芯片的vbat引脚与备用电源的正极连接,tp4054充电芯片的vss引脚接地,电阻r1的一端与tp4054充电芯片的prog引脚连接,另一端与备用电源的负极连接并接地,二极管d1的正极与电源连接,二极管d1的负极与时钟芯片连接,二极管d2的正极与备用电源连接,二极管d2的负极与时钟芯片连接。本实施例中,电源的电压为5v,备用电源的工作电压3v,电阻r1的阻值范围为大于等于20k欧姆且小于等于100k欧姆。本实施例中,电阻r1的阻值为100k欧姆。

26.本实施例中,时钟芯片为pcf8563时钟芯片,pcf8563时钟芯片的vcc引脚分别与电源和备用电源电连接,pcf8563时钟芯片的x1引脚连接晶振的一端,pcf8563时钟芯片的x2引脚连接晶振的另一端,框架断路器包括主控芯片,pcf8563时钟芯片的scl引脚与主控芯片的scl引脚连接,pcf8563时钟芯片的sda引脚与主控芯片的sda引脚连接。本实施例中,晶振的频率为32.768khz。

27.本实用新型的时钟电路工作时,若电源正常工作,由电源为时钟芯片供电,并由电

源通过充电管理模块为备用电源充电,若电源断电,则由备用电源为时钟芯片供电。

28.上述实施方式仅为例举,不表示对本实用新型范围的限定。这些实施方式还能以其它各种方式来实施,且能在不脱离本实用新型技术思想的范围内作各种省略、置换、变更。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1