一种芯片化紧凑型继电保护装置的制作方法

1.本申请涉及电力系统技术领域,特别是涉及一种芯片化紧凑型继电保护装置。

背景技术:

2.继电保护装置是电力系统中常用的器件,继电保护装置的工作状态直接影响到整个电力系统,担负着保护电力系统安全稳定运行的重要使命。

3.目前,国内外主要的继电保护厂家制造的继电保护装置,无论是常规化继电保护装置,还是数字化继电保护装置,通常有两种形式:一种是多板卡的插箱形式,不同板卡之间通过总线通信,板卡间通信规约种类多、不标准、复杂且通信速率较低,每台装置配置5

‑

8块板卡,每块板卡至少有一颗cpu芯片,单台装置的cpu芯片在5颗以上,体积大。另一种是以美国sel生产的保护装置为代表,采用大板式设计,多处理器在一块板卡上,但同样具有体积大的问题,占用较多空间。

技术实现要素:

4.基于此,有必要针对上述技术问题,提供一种能够减小体积的芯片化紧凑型继电保护装置。

5.一种芯片化紧凑型继电保护装置,包括背板、开入插件、开出插件、交互面板、接收通过所述开入插件输入的数据并发送显示信息的cpu插件以及接收所述cpu插件发送的显示信息并发送至所述交互面板的通信管理插件,所述cpu插件、所述通信管理插件、所述开入插件和所述开出插件设置于所述背板,所述cpu插件通过所述背板连接所述通信管理插件、所述开入插件和所述开出插件,所述通信管理插件通过所述背板连接所述交互面板。

6.在其中一个实施例中,所述cpu插件包括双核芯片和外部存储器,所述双核芯片包括主内核、从内核、前端数据处理模块、内部存储器和存储管理模块;

7.所述主内核连接所述开入插件和所述开出插件,所述从内核连接所述通信管理插件,且所述主内核和所述前端数据处理模块连接所述内部存储器,所述主内核、所述从内核和所述前端数据处理模块均连接所述存储管理模块,所述存储管理模块连接所述外部存储器。

8.在其中一个实施例中,所述cpu插件还包括第一phy芯片和光纤以太网口,所述第一phy芯片分别连接所述前端数据处理模块和所述光纤以太网口。

9.在其中一个实施例中,所述光纤以太网口包括2路

‑

8路sv/goose合一接口。

10.在其中一个实施例中,所述cpu插件还包括光差通道,所述前端数据处理模块连接所述光差通道。

11.在其中一个实施例中,所述通信管理插件包括单核芯片和fpga,所述单核芯片连接所述fpga、所述cpu插件和所述交互面板。

12.在其中一个实施例中,所述通信管理插件还包括第二phy芯片和电口以太网口,所述第二phy芯片分别连接所述fpga和所述电口以太网口。

13.在其中一个实施例中,所述通信管理插件还包括连接所述fpga的对时接口和/或打印串口。

14.在其中一个实施例中,所述开出插件包括多个继电器,所述继电器连接所述cpu插件和所述外部设备。

15.在其中一个实施例中,上述芯片化紧凑型继电保护装置还包括电源插件,所述电源插件连接所述cpu插件、所述通信管理插件、所述开入插件、所述开出插件和所述交互面板。

16.上述芯片化紧凑型继电保护装置中,cpu插件通过开入插件和开出插件与外部设备数据交互,可以获取数据发送显示信息,通信管理插件将显示信息发送至交互面板进行显示,以便用户查看;通过采用一个cpu插件实现数据交互和处理功能,减少板卡的使用,使得结构更紧凑,从而可以减小整体的体积,减少占用空间。

附图说明

17.为了更清楚地说明本申请实施例或传统技术中的技术方案,下面将对实施例或传统技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本申请的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

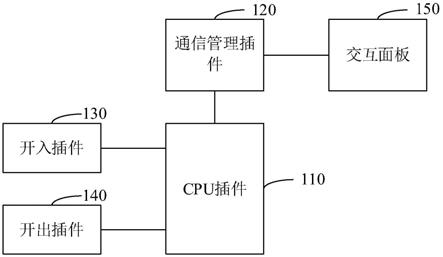

18.图1为一个实施例中芯片化紧凑型继电保护装置的结构示意图;

19.图2为一个实施例中cpu插件的内部结构示意图;

20.图3为另一个实施例中cpu插件的内部结构示意图;

21.图4为一个实施例中cpu插件的电源电路的示意图;

22.图5为一个实施例中cpu插件的时钟设计的示意图;

23.图6为一个实施例中通信管理插件的结构图;

24.图7(a)为一个实施例中开入插件的部分电路原理图;

25.图7(b)为一个实施例中开入插件的另一部分电路原理示意图;

26.图7(c)为一个图7(a)和图7(b)对应的端子示意图;

27.图8(a)为一个实施例中开出插件的部分电路原理图;

28.图8(b)为一个实施例中开出插件的另一部分电路原理图;

29.图8(c)为一个图8(a)和图8(b)对应的端子示意图;

30.图9为一个实施例中电源插件的电路原理图;

31.图10为一个实施例中芯片化紧凑型继电保护装置的外观示意图;

32.图11为一个实施例中芯片化紧凑型继电保护装置的线路保护装置硬件配置图。

具体实施方式

33.为了便于理解本申请,下面将参照相关附图对本申请进行更全面的描述。附图中给出了本申请的实施例。但是,本申请可以以许多不同的形式来实现,并不限于本文所描述的实施例。相反地,提供这些实施例的目的是使本申请的公开内容更加透彻全面。

34.除非另有定义,本文所使用的所有的技术和科学术语与属于本申请的技术领域的技术人员通常理解的含义相同。本文中在本申请的说明书中所使用的术语只是为了描述具

体的实施例的目的,不是旨在于限制本申请。

35.可以理解,本申请所使用的术语“第一”、“第二”等可在本文中用于描述各种元件,但这些元件不受这些术语限制。这些术语仅用于将第一个元件与另一个元件区分。

36.需要说明的是,当一个元件被认为是“连接”另一个元件时,它可以是直接连接到另一个元件,或者通过居中元件连接另一个元件。此外,以下实施例中的“连接”,如果被连接的对象之间具有电信号或数据的传递,则应理解为“电连接”、“通信连接”等。

37.在此使用时,单数形式的“一”、“一个”和“所述/该”也可以包括复数形式,除非上下文清楚指出另外的方式。还应当理解的是,术语“包括/包含”或“具有”等指定所陈述的特征、整体、步骤、操作、组件、部分或它们的组合的存在,但是不排除存在或添加一个或更多个其他特征、整体、步骤、操作、组件、部分或它们的组合的可能性。同时,在本说明书中使用的术语“和/或”包括相关所列项目的任何及所有组合。

38.参考图1,在一个实施例中,提供了一种芯片化紧凑型继电保护装置,包括背板(图未示)、接收通过开入插件输入的数据并发送显示信息的cpu插件110、接收cpu插件110发送的显示信息并发送至交互面板150的通信管理插件120、开入插件130、开出插件140和交互面板150,cpu插件110、通信管理插件120、开入插件130和开出插件140设置于背板,cpu插件110通过背板连接通信管理插件120、开入插件130和开出插件140,通信管理插件120通过背板连接交互面板150。

39.cpu插件110通过开入插件130和开出插件140与外部设备数据交互,获取数据后生成显示信息并通过通信管理插件120发送至交互面板150进行显示。其中,外部设备可以是设置芯片化紧凑型继电保护装置的现场采用的设备,外部设备可以提供继电保护所需要用到的数据,以及接收cpu插件110输出的信息。其中,cpu插件110是芯片化紧凑型继电保护装置的核心,可以实现继电保护装置基本具有的保护功能,比如可以根据获取的数据进行保护分析、根据分析结果确定是否需要跳闸,或者根据获取的数据进行保护分析、输出需要告知用户的用于提示保护分析结果的显示信息;其中,cpu插件110获取的数据可以是通过开入插件130接收的外部设备输出的数据。通信管理插件120是可以实现通信管理功能的插件,比如通过与cpu插件110和交互面板150连接,将cpu插件110发送的显示信息发出至交互面板150;交互面板150是可以显示信息的器件,在接收显示信息后进行显示,以便用户查看。

40.具体地,cpu插件110、通信管理插件120、开入插件130、开出插件140和交互面板150可以集成于一个芯片的背板上,即,整体芯片化。

41.上述芯片化紧凑型继电保护装置中,cpu插件110通过开入插件130和开出插件140与外部设备数据交互,可以获取数据发送显示信息,通信管理插件120将显示信息发送至交互面板150进行显示,以便用户查看;通过采用一个cpu插件110实现数据交互和处理功能,减少板卡的使用,使得结构更紧凑,从而可以减小整体的体积,减少占用空间。

42.在其中一个实施例中,cpu插件110包括双核芯片和外部存储器,双核芯片包括主内核、从内核、前端数据处理模块、内部存储器和存储管理模块。其中,主内核连接开入插件130和开出插件140,从内核连接通信管理插件120,且主内核和前端数据处理模块连接内部存储器,主内核、从内核和前端数据处理模块均连接存储管理模块,存储管理模块连接外部存储器。

43.其中,前端数据处理模块可以与外部装置通信以采集数据并发送至内部存储器,实现数据采集;具体地,前端数据处理模块可以向内部存储器中写入数据,主内核可以从内部存储器中读取数据进行处理,实现数据处理。具体地,主内核、从内核和前端数据处理模块之间可以通过存储管理模块连接的外部存储器进行数据交换,实现内部的数据交互。具体地,主内核、从内核和前端数据处理模块均可以通过存储管理模块从外部存储器中读写数据,使得主内核、从内核和前端数据处理模块三者可以通过外部存储器进行数据交换。通过采用双核芯片,实现双核结构的cpu插件,功能强大,可以在一个cpu插件实现数据采集、处理和交互,将多种功能集成于一个插件,实现小型化、高集成设计方案,减少板卡的使用,整体结构更紧凑,从而减小体积。

44.如图2所示,前端数据处理模块可以是fpga(field programmable gate array现场可编程逻辑门阵列),内部存储器可以是ram(random access memory随机存取存储器)。外部存储器200可以是ddr(double data rate双倍数率)存储器。cpu插件还可以包括flash、eeprom(electrically erasable programmable read only memory带电可擦可编程只读存储器),flash用于存储内核和fpga的程序文件,ddr由2个内核共享。除此之外,从内核core2还可以增加连接一个rtc(实时时钟)。

45.在其中一个实施例中,参考图3,cpu插件110还包括第一phy芯片和光纤以太网口,第一phy芯片分别连接前端数据处理模块和光纤以太网口。

46.具体地,前端数据处理模块为fpga,即,fpga通过第一phy芯片连接光纤以太网口。cpu插件110通过第一phy芯片扩展光纤以太网接口,用以实现多路的sv/goose报文传输,通信便利。

47.在其中一个实施例中,光纤以太网口可以包括2路

‑

8路sv/goose合一接口。sv/goose合一接口可以传输sv报文和goose报文,采用对外的多路sv/goose合一接口可以提高网络通信的便利性。

48.在其中一个实施例中,cpu插件110还包括光差通道,前端数据处理模块连接光差通道。

49.在其中一个实施例中,cpu插件110还包括光差通道,前端数据处理模块连接光差通道。

50.具体地,前端数据处理模块为fpga,即,fpga连接光差通道。fpga内部实现hdlc(high

‑

level data link control,高级数据链路控制)功能,通过外部的电平转换电路输出lvpecl(low voltage positive emitter

‑

couple logic低压正发射极耦合逻辑)电平,驱动2m光模块,可以实现线路的光差保护。

51.cpu插件110需要的电源种类非常多,如下表1所示。

52.表1

[0053][0054]

cpu插件110的ps(processing system处理系统)部分、pl(programmable logic可编程逻辑)部分以及硬件收发器gtx分别独立供电,汇总以后主要需要1.0v、1.8v、1.5v和3.3v四种电压,模拟电源使用数字电源滤波后得到。cpu插件110的输入电源为5v,使用dc/dc芯片或者ldo(low dropout regulator低压差线性稳压器)转换成需要的各电压等级,电源电路的拓扑结构如图4所示。3.3v、1.8v、1.5v和1.0v统一采用dc/dc方案,1.2v使用3.3v经过ldo转换得到,最大输出电流1a。其中,dc/dc可外接缓启动电容,可以通过调节电容的大小来控制不同的电压上电时序。

[0055]

cpu插件110需要多种时钟:ps时钟、phy时钟、收发器参考时钟以及hdlc精密时钟,具体如下表2所示。

[0056]

表2

[0057][0058]

时钟设计如图5所示,50mhz有源晶振经过时钟驱动器后,分别给ps、pl和phy使用。25mhz有源晶振经过倍频芯片后输出125m lvds差分时钟,做为硬件收发器(gtx)的参考时钟,实现光纤以太网。fpga内部无法实现精确的小数分频,外部提供65.536mhz有源晶振,用于实现hdlc协议。

[0059]

在其中一个实施例中,通信管理插件120包括单核芯片和fpga,单核芯片连接fpga、cpu插件110和交互面板150。

[0060]

其中,单核芯片是具有一个内核的芯片,具体地,单核芯片可以为zynq芯片;通信管理插件120使用单核芯片实现对时和通信管理功能,使用fpga进行数据处理后与外部通信;单核芯片可以接收cpu插件110发送的显示信息并发送至交互面板150进行显示,结构简单。

[0061]

在其中一个实施例中,参考图6,通信管理插件120还包括第二phy芯片和电口以太网口。第二phy芯片分别连接fpga和电口以太网口,即,fpga通过第二phy芯片连接电口以太网口。通过采用第二phy芯片扩展电网以太网口,用于实现多路通信,通信便利。具体地,电口以太网口包括3路电口以太网口。

[0062]

在其中一个实施例中,通信管理插件120还包括连接fpga的对时接口和/或打印串口。fpga的对时模块实现对时功能,通过连接对时接口便于对时;通过采用打印串口,便于与打印设备连接进行打印。通过提供对时接口和打印串口,功能多样。

[0063]

例如,如图6所示,通信管理模块120包括对时接口和打印串口。图6中,master表示单核芯片,master插件即为通信管理插件,master插件通过第二phy芯片扩展3路电口以太网口用于mms网络,同时对外1路对时接口和1路打印串口。

[0064]

在其中一个实施例中,开入插件130包括提供28路开关量输入的开入模块,开入模块连接cpu插件110和外部设备。例如图7(a)、图7(b)、图7(c)所示,采用多路开关量输入,可供多路输入。

[0065]

在其中一个实施例中,开出插件140包括多个继电器,继电器连接cpu插件110和外部设备。具体地,一个继电器对应一路开关量输出,继电器的数量可以为16,则对应16路开关量输出;继电器闭合,则cpu插件110可输出数据,具体地,可以由cpu插件110控制继电器是否闭合。例如图8(a)、图8(b)、图8(c)所示,采用多路开关量输出,可供多路输出。

[0066]

在其中一个实施例中,上述芯片化紧凑型继电保护装置还包括电源插件,电源插件连接cpu插件110、通信管理插件120、开入插件130、开出插件140和交互面板150,用于给cpu插件110、通信管理插件120、开入插件130、开出插件140和交互面板150供电。具体地,芯片化紧凑型继电保护装置还可以包括背板,cpu插件110、通信管理插件120、开入插件130和开出插件140设置于背板,电源插件通过背板连接cpu插件110、通信管理插件120、开入插件130、开出插件140和交互面板150。

[0067]

例如,如图9所示,电源插件提供4路告警开出信号。电源插件的输入为额定电压un:ac/dc 110v/220v,输入电压范围:

±

20%un;输出为额定电压:5v、24v,开出信号:2组。

[0068]

在其中一个实施例中,交互面板150配置320*240分辨率液晶、以太网调试口、操作按键以及指示灯;交互面板150最多支持24个红绿双色指示灯,实际使用个数及定义可以根据装置类型进行自定义,通过can网与通信管理插件120通信,接收通信管理插件的显示信息进行显示。

[0069]

具体地,芯片化紧凑型继电保护装置的外观如图10所示,硬件配置和网口功能分配如图11所示,插件列表如下表3所示。

[0070]

表3

[0071]

[0072][0073]

在本说明书的描述中,参考术语“有些实施例”、“其他实施例”、“理想实施例”等的描述意指结合该实施例或示例描述的具体特征、结构、材料或者特征包含于本申请的至少一个实施例或示例中。在本说明书中,对上述术语的示意性描述不一定指的是相同的实施例或示例。

[0074]

以上实施例的各技术特征可以进行任意的组合,为使描述简洁,未对上述实施例中的各个技术特征所有可能的组合都进行描述,然而,只要这些技术特征的组合不存在矛盾,都应当认为是本说明书记载的范围。

[0075]

以上所述实施例仅表达了本申请的几种实施方式,其描述较为具体和详细,但并不能因此而理解为对实用新型专利范围的限制。应当指出的是,对于本领域的普通技术人员来说,在不脱离本申请构思的前提下,还可以做出若干变形和改进,这些都属于本申请的保护范围。因此,本申请专利的保护范围应以所附权利要求为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1