一种高速脉冲输出占空比控制电路的制作方法

1.本实用新型涉及电路设计技术领域,尤其涉及一种高速脉冲输出占空比控制电路。

背景技术:

2.plc(programmable logic controller,可编程逻辑控制器)广泛应用于各种自动化控制领域,它是专门在工业环境下应用而设计的数字运算操作电子系统,它采用一种可编程的存储器,在其内部存储执行逻辑运算、顺序控制、定时、计算和算术运算等操作的指令,通过数字式或模拟式的输入输出来控制各种类型的机械设备或生产过程,plc主要功能之一是实现不同频率和占空比的高速脉冲输出。

3.目前plc高速脉冲输出通道,大多采用mos管来实现。但由于mos管结电容及外部杂散电容的存在,plc高速脉冲频率无法达到很高。尤其plc与驱动电流较小的设备连接时,往往存在输出的高速脉冲占空比出现极大的偏差,最终无法被所接设备正常获取。plc高速脉冲输出占空比补偿相关技术的不多,主要解决办法以及存在缺陷如下:

4.1)选择结电容小的mos管,但受半导体工艺影响,mos管的耐压和过流变小,在实际应用中容易损坏。

5.2)通过cpld或cpu对所输出的脉冲占空比进行采集,然后再与预期预设值进行比较。但需要硬件资源采集脉冲信号以及软件程序进行比对调整,控制相对麻烦。

技术实现要素:

6.为了克服上述现有技术的缺陷,本实用新型所要解决的技术问题是提供一种高速脉冲输出占空比控制电路。

7.为了解决上述技术问题,本实用新型采用的技术方案为:

8.一种高速脉冲输出占空比控制电路,包括mos管驱动电路、mos管q1和电容cs,所述mos管驱动电路的输入端与外置的cpu电连接,所述mos管驱动电路的输出端与mos管q1的栅极电连接,所述电容cs为mos管q1内部结电容及外部电路杂散电容的总和,所述电容cs的两端分别与mos管q1的漏极和源极电连接,所述mos管q1的漏极用于与外部脉冲接收设备电连接,还包括加速电路,所述加速电路与mos管q1的漏极电连接。

9.进一步的,所述加速电路包括电源vdd1、电阻r2和二极管d1;

10.所述电源vdd1与电阻r2一端电连接,所述电阻r2另一端与二极管d1正极电连接,所述二极管d1负极与mos管q1的漏极电连接。

11.进一步的,所述加速电路包括电源vdd2、反相器u2、电阻r3和二极管d2;

12.所述电源vdd2与反相器u2的电源端电连接;所述反相器u2的输入端与mos管驱动电路的输出端电连接,所述反相器u2的输出端与电阻r3一端电连接,所述电阻r3另一端与二极管d2正极电连接,所述二极管d2负极与mos管q1的漏极电连接。

13.进一步的,还包括电压监控电路,所述电压监控电路与加速电路电连接。

14.进一步的,所述电压监控电路包括电阻r9、电阻r13、电阻r15、电阻r16、电阻r17、电阻r18、电阻r21、电阻r22、电阻r23、电容c6、电容c5、肖特基二极管d4、电压基准芯片u3、运算放大器u6a和运算放大器u6d;

15.所述电阻r9一端与mos管q1的漏极电连接,所述电阻r9另一端分别与电阻r13一端、电容c6一端和运算放大器u6a的反向输入端电连接,所述电阻r13另一端和电容c6另一端均接地;所述运算放大器u6a的反向输入端与运算放大器u6d的正向输入端电连接;所述电阻r17一端与运算放大器u6a的正向输入端电连接;所述运算放大器u6a的输出端分别与电阻r22一端和肖特基二极管d4电连接;所述电阻r22另一端接地;

16.所述电压基准芯片u3分别与电阻r16一端、电阻r18一端、电阻r17另一端和电容c5一端电连接,所述电阻r16另一端与电源vcc5v电连接,所述电容c5另一端接地;所述电阻r18另一端分别与电阻r23一端和运算放大器u6d的反向输入端电连接;所述运算放大器u6d的输出端分别与电阻r21一端和肖特基二极管d4电连接;所述电阻r21另一端接地;

17.所述肖特基二极管d4与电阻r15一端电连接,所述电阻r15另一端与电源vcc5v电连接,所述电阻r15一端与加速电路电连接。

18.本实用新型的有益效果在于:

19.本实用新型提供的一种高速脉冲输出占空比控制电路,通过增加加速电路解决外部设备驱动电流不足问题。当mos_ctl信号输出高电平时,mos管q1正常导通,y_puls_out为低电平。当mos_ctl信号输出低电平时,mos管q1截止。这时除了外部设备供电vdd_d通过电阻r1对cs进行充电外,加速电路也会提供额外的一路电流对电容cs充电,使电容cs由0v充电到高电平阈值uh的时间变短,使得脉冲信号高电平的占空比得到改善。

附图说明

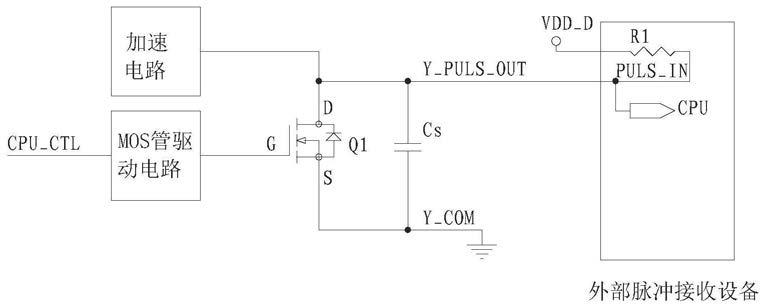

20.图1所示为本实用新型一种高速脉冲输出占空比控制电路的电路连接图;

21.图2所示为本实用新型一种高速脉冲输出占空比控制电路的电路连接图;

22.图3所示为本实用新型一种高速脉冲输出占空比控制电路的电路连接图;

23.图4所示为本实用新型一种高速脉冲输出占空比控制电路的电路连接图;

24.图5所示为本实用新型一种电压监控电路的电路连接图。

具体实施方式

25.为详细说明本实用新型的技术内容、所实现目的及效果,以下结合实施方式并配合附图予以说明。

26.请参照图1所示,本实用新型的一种高速脉冲输出占空比控制电路,包括mos管驱动电路、mos管q1和电容cs,所述mos管驱动电路的输入端与外置的cpu电连接,所述mos管驱动电路的输出端与mos管q1的栅极电连接,所述电容cs为mos管q1内部结电容及外部电路杂散电容的总和,所述电容cs的两端分别与mos管q1的漏极和源极电连接,所述mos管q1的漏极用于与外部脉冲接收设备电连接,还包括加速电路,所述加速电路与mos管q1的漏极电连接。

27.从上述描述可知,本实用新型的有益效果在于:本实用新型提供的一种高速脉冲输出占空比控制电路,通过增加加速电路解决外部设备驱动电流不足问题。当mos_ctl信号

输出高电平时,mos管q1正常导通,y_puls_out为低电平。当mos_ctl信号输出低电平时,mos管q1截止。这时除了外部设备供电vdd_d通过电阻r1对cs进行充电外,加速电路也会提供额外的一路电流对电容cs充电,使电容cs由0v充电到高电平阈值uh的时间变短,使得脉冲信号高电平的占空比得到改善。

28.进一步的,所述加速电路包括电源vdd1、电阻r2和二极管d1;

29.所述电源vdd1与电阻r2一端电连接,所述电阻r2另一端与二极管d1正极电连接,所述二极管d1负极与mos管q1的漏极电连接。

30.从上述描述可知,加速电路可简单的由电源vdd1、电阻r2、二极管d1组成。其中电源vdd1的负极必须与高速输出电路的y_com相连。二极管d1的作用是防止外部电平高于vdd1时,导致电压反灌,引起vdd1电源不良。vdd1为加速充电电压,电阻r2起限流作用,根据实际应用调整vdd1电压值和r2阻值,可达到不同的加速速度。该方案简单且易实现。

31.进一步的,所述加速电路包括电源vdd2、反相器u2、电阻r3和二极管d2;

32.所述电源vdd2与反相器u2的电源端电连接;所述反相器u2的输入端与mos管驱动电路的输出端电连接,所述反相器u2的输出端与电阻r3一端电连接,所述电阻r3另一端与二极管d2正极电连接,所述二极管d2负极与mos管q1的漏极电连接。

33.从上述描述可知,带使能的加速电路。加速电路增加使能控制,使加速电路在mos管q1截止时才会提供驱动补偿电流。加速电路的使能信号可以由mos管控制信号mos_ctl提供,也可以由cpu普通io控制。

34.进一步的,还包括电压监控电路,所述电压监控电路与加速电路电连接。

35.进一步的,所述电压监控电路包括电阻r9、电阻r13、电阻r15、电阻r16、电阻r17、电阻r18、电阻r21、电阻r22、电阻r23、电容c6、电容c5、肖特基二极管d4、电压基准芯片u3、运算放大器u6a和运算放大器u6d;

36.所述电阻r9一端与mos管q1的漏极电连接,所述电阻r9另一端分别与电阻r13一端、电容c6一端和运算放大器u6a的反向输入端电连接,所述电阻r13另一端和电容c6另一端均接地;所述运算放大器u6a的反向输入端与运算放大器u6d的正向输入端电连接;所述电阻r17一端与运算放大器u6a的正向输入端电连接;所述运算放大器u6a的输出端分别与电阻r22一端和肖特基二极管d4电连接;所述电阻r22另一端接地;

37.所述电压基准芯片u3分别与电阻r16一端、电阻r18一端、电阻r17另一端和电容c5一端电连接,所述电阻r16另一端与电源vcc5v电连接,所述电容c5另一端接地;所述电阻r18另一端分别与电阻r23一端和运算放大器u6d的反向输入端电连接;所述运算放大器u6d的输出端分别与电阻r21一端和肖特基二极管d4电连接;所述电阻r21另一端接地;

38.所述肖特基二极管d4与电阻r15一端电连接,所述电阻r15另一端与电源vcc5v电连接,所述电阻r15一端与加速电路电连接。

39.从上述描述可知,电压基准芯片u3为电压监控提供基准电压源,可以通过调整基准源或r9、r13、r18、r23的值,实现在特定的电压范围内使能加速电路。该方案通过监控y_puls_out电压来实现加速电路的使能。

40.请参照图1

‑

图2所示,本实用新型的实施例一为:

41.在现有技术中,当高速脉冲输出y_puls_out连接的外部设备,驱动能力较弱,即r1电阻较大时,mos管q1由导通状态切换成截止状态时,需要对cs进行充电。当r1阻值越大,时

间常数τ=r1*cs就越大。电容cs充电时间t1就越大。当外部设备高电平阈值uh越大,电容cs由0v充电至uh的时间越大,y_puls_out输出高电平就越窄,占空比则越小。当随着mos管开关频率的加快,电容cs充电时间会成为脉冲信号y_puls_out占空比畸变的关键原因。其中r1阻值越大占空比畸变越严重。

42.针对上述技术问题,本实用新型的一种高速脉冲输出占空比控制电路,包括mos管驱动电路、mos管q1和电容cs,所述mos管驱动电路的输入端与外置的cpu电连接,所述mos管驱动电路的输出端与mos管q1的栅极电连接,所述电容cs的两端分别与mos管q1的漏极和源极电连接,所述mos管q1的漏极用于与外部脉冲接收设备电连接,还包括加速电路,所述加速电路与mos管q1的漏极电连接。所述加速电路包括电源vdd1、电阻r2和二极管d1;所述电源vdd1与电阻r2一端电连接,所述电阻r2另一端与二极管d1正极电连接,所述二极管d1负极与mos管q1的漏极电连接。在本实施例中,电阻r2的阻值为1kω。

43.其中电源vdd1的负极必须与高速输出电路的y_com相连。二极管d1的作用是防止外部电平高于vdd1时,导致电压反灌,引起vdd1电源不良。vdd1为加速充电电压,电阻r2起限流作用,根据实际应用调整vdd1电压值和r2阻值,可达到不同的加速速度,当y_puls_out电压大于vdd1时,二极管d1截止,加速电路不再提供电流对cs进行充电。该方案简单且易实现。但缺点是当mos管q1导通时,加速电路的驱动电流仍然存在,造成功耗浪费。vdd1电压选择会受外接设备电平的影响,外设兼容性会差些。

44.请参照图1

‑

图3所示,本实用新型的实施例二为:

45.本实施例二提供另一种的加速电路以代替上述实施例一中的加速电路;

46.其中,所述加速电路包括电源vdd2、反相器u2、电阻r3和二极管d2;

47.所述电源vdd2与反相器u2的电源端电连接;所述反相器u2的输入端与mos管驱动电路的输出端电连接,所述反相器u2的输出端与电阻r3一端电连接,所述电阻r3另一端与二极管d2正极电连接,所述二极管d2负极与mos管q1的漏极电连接。在本实施例中,电阻r3的阻值为2.2kω。

48.通过加速电路增加使能控制,使加速电路在mos管q1截止时才会提供驱动补偿电流。具体工作原理为:当mos_ctl高电平时,mos管q1导通。这时mos_ctl控制反相器u2输出低电平,二极管d2截止。当mos_ctl低电平时,mos管q1截止,这时反相器u2输出高电平,二极管d2导通,加速电路提供补偿电流,提升cs杂散电容的充电速度。加速电路的使能信号可以由mos管控制信号mos_ctl提供,也可以由cpu普通io控制。该方案与上述方式相比,由于mos管q1导通时,反相器u2输出为低电平,d2截止,加速电路没有提供电流,更节能环保一些。但缺点是vdd2电压仍然受外设应用电平影响,在不同应用场景下,无法做到较好的兼容。

49.请参照图1

‑

图5所示,本实用新型的实施例三为:

50.本实施例为在上述实施例一或二的基础上增加电压监控功能,具体为:还包括电压控制电路,所述电压监控电路与加速电路电连接。

51.其中,所述电压监控电路包括电阻r9、电阻r13、电阻r15、电阻r16、电阻r17、电阻r18、电阻r21、电阻r22、电阻r23、电容c6、电容c5、肖特基二极管d4、电压基准芯片u3、运算放大器u6a和运算放大器u6d;

52.所述电阻r9一端与mos管q1的漏极电连接,所述电阻r9另一端分别与电阻r13一端、电容c6一端和运算放大器u6a的反向输入端电连接,所述电阻r13另一端和电容c6另一

端均接地;所述运算放大器u6a的反向输入端与运算放大器u6d的正向输入端电连接;所述电阻r17一端与运算放大器u6a的正向输入端电连接;所述运算放大器u6a的输出端分别与电阻r22一端和肖特基二极管d4电连接;所述电阻r22另一端接地;

53.所述电压基准芯片u3分别与电阻r16一端、电阻r18一端、电阻r17另一端和电容c5一端电连接,所述电阻r16另一端与电源vcc5v电连接,所述电容c5另一端接地;所述电阻r18另一端分别与电阻r23一端和运算放大器u6d的反向输入端电连接;所述运算放大器u6d的输出端分别与电阻r21一端和肖特基二极管d4电连接;所述电阻r21另一端接地;

54.所述肖特基二极管d4与电阻r15一端电连接,所述电阻r15另一端与电源vcc5v电连接,所述电阻r15一端与加速电路电连接。

55.在本实施例中,电阻r9的规格为137k/f/1206,电阻r13的规格为35k/f/0805,电阻r15的规格为2k2/0805,电阻r16的规格为1k/0805,电阻r17的规格为10k/f/0805,电阻r18的规格为100k/f/0805,电阻r21的规格为2k2/0805,电阻r22的规格为2k2/0805,电阻r23的规格为75k/f/0805,电容c6的规格为101/0805,电容c5的规格为106/0805,肖特基二极管d4的型号为bat54a,电压基准芯片u3的型号为tl431acdbzr,运算放大器u6a和运算放大器u6d的型号均为mc33074adr2。

56.具体工作原理为:当信号y_puls_out电压在5.26~12.27v之间时,即v_det电压值刚好处于vref和vref1两个参考电压之间,则u6a、u6d均输出高电平,肖特基二极管d4内的2个二极管均截止,en信号为高电平。en信号使能加速电路。当信号y_puls_out电压小于5.26v或大于12.27v时,u6a、u6d其中一路输出低电平,d4内的二极管其中一路导通,en信号为低电平,加速电路不使能。电压基准芯片u3为电压监控提供基准电压源,可以通过调整基准源或r9、r13、r18、r23的值,实现在特定的电压范围内使能加速电路。该方案通过监控y_puls_out电压来实现加速电路的使能。plc高速脉冲所接外设一般有5v、12v和24v这3种电平。当外设为5v电平外设时,由于电容cs充电到5v电平时所需的时间较小,且y_puls_out电压达不到5.26v,不使能加速电路。当外设为12v和24v电平设备时,cs从0v充电上升到5.26v后,使能加速电路,让电容cs快速的由5.26v充电至12.27v,当y_puls_out电压上升至12.27v后,加速电路使能失效。

57.综上所述,本实用新型提供的一种高速脉冲输出占空比控制电路,通过增加加速电路解决外部设备驱动电流不足问题。当mos_ctl信号输出高电平时,mos管q1正常导通,y_puls_out为低电平。当mos_ctl信号输出低电平时,mos管q1截止。这时除了外部设备供电vdd_d通过电阻r1对cs进行充电外,加速电路也会提供额外的一路电流对电容cs充电,使电容cs由0v充电到高电平阈值uh的时间变短,使得脉冲信号高电平的占空比得到改善。

58.以上所述仅为本实用新型的实施例,并非因此限制本实用新型的专利范围,凡是利用本实用新型说明书及附图内容所作的等同变换,或直接或间接运用在相关的技术领域,均同理包括在本实用新型的专利保护范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1