将转换器启动到预偏置电压的方法和设备与流程

1.本描述大体上涉及基于延迟的脉宽调制电源转换器,并且更具体地涉及将转换器启动为预偏置电压的方法和设备。

背景技术:

2.电源转换器(例如,降压转换器、降压

‑

升压转换器等)和/或各种功率电子装置响应于脉宽调制(pwm)信号发生器生成的脉宽调制信号而操作。在一些电源转换器和/或各种功率电子装置应用中,开关(例如,晶体管)由基于斜坡的pwm技术(例如,模拟控制)进行控制。最近,电源转换器和/或各种基于功率电子的装置的制造商已经开发了基于延迟的pwm技术作为基于斜坡的pwm技术的替代方案。基于延迟的pwm技术涉及利用延迟的pwm发生器生成脉冲宽度是延迟的函数的信号。

技术实现要素:

附图说明

3.图1是包括示例控制器的示例电源转换器系统的框图。

4.图2是示例电源转换器系统的示意图,其示出了图1的控制器的进一步细节。

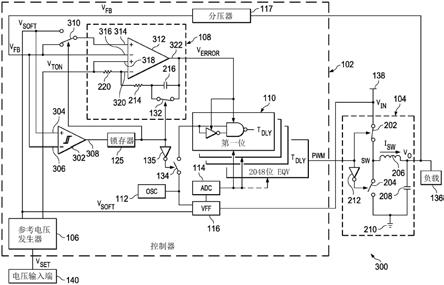

5.图3是示例电源转换器系统的示意图,其示出了图1的控制器的替代细节。

6.图4是示出图1的示例电压前馈控制器、图2的示例电压前馈控制器和/或图3的示例电压前馈控制器的进一步细节的示意图。

7.图5是示出图1的示例参考电压发生器、图2的示例参考电压发生器和/或图3的示例参考电压发生器的进一步细节的示意图。

8.图6是图示图1的示例电源转换器系统、图2的示例电源转换器系统和/或图3的示例电源转换器系统的操作的时序图。

9.图7是图示图1的示例电源转换器系统、图2的示例电源转换器系统和/或图3的示例电源转换器系统的附加操作的时序图。

10.图8是图示图1的示例参考电压发生器、图2的示例参考电压发生器和/或图3的示例参考电压发生器的操作的时序图。

11.图9是表示可以被执行以实现图1、2和3的示例控制器的示例机器可读指令的流程图。

12.附图不是按比例绘制。通常,在整个附图和随附的书面描述中将使用相同的附图标记来指代相同或相似的部件。

13.当标识可被单独引用的多个元件或部件时,在本文中使用描述符第一、第二、第三等。除非另有说明,否则这样的描述符不代表任何优先级或时间排序的含义,而仅仅是为了便于理解所描述的示例而分别指代多个元件或部件的标签。在一些示例中,描述符第一可以用于指代详细描述中的元件,而在权利要求中可以使用诸如第二或第三的不同描述符来

指代相同的元件。在这种情况下,仅仅为了易于指代多个元件或部件而使用这样的描述符。

具体实施方式

14.一些直流到直流(dc

‑

dc)转换器和/或其他功率电子装置(例如,交流(ac)逆变器)利用由生成pwm信号的控制器控制的多个开关(例如,晶体管)。在这样的应用中,控制器包括pwm信号发生器以响应于监测耦合的dc

‑

dc转换器的输出电压而生成和/或以其他方式向转换器提供pwm信号。在一些应用中,pwm信号发生器是延迟脉宽调制器(dpwm)(例如,基于延迟时间和/或周期生成脉宽调制信号的脉宽调制器,基于延迟的脉宽调制器)而不是比基于模拟的pwm信号发生器。与基于模拟的pwm信号发生器相比,dpwm具有优势,因为dpwm能够在pwm信号中产生更窄的脉冲(例如,小于30纳秒的脉冲)而没有抖动,而基于模拟的pwm信号发生器可能不能够产生如此窄的脉冲。

15.不是像基于模拟的pwm发生器那样通过将控制信号电压与基于斜坡的信号(例如,锯齿信号)进行比较来产生pwm信号,而是dpwm通过引入对应于期望的脉冲宽度的延迟来产生和/或以其它方式生成pwm信号。dpwm包括可由至少一个控制信号控制的延迟单元。控制信号由控制器生成并指示多个延迟单元中的每一个要引入的延迟长度(例如,1.0纳秒、1.2纳秒等)。在一些示例中,dpwm包含在控制器中。

16.在某些情况下,在控制器启用电源转换器之前,可能会有电压施加到电源转换器的输出端。例如,处理器集成电路(ic)需要第一电压电平(例如,1.2伏)用于核心功率,但需要第二电压电平(例如,3.3伏)用于输入和输出功率。在这样的示例中,在启动期间,可以在启用第二电压之前达到第一电压电平。处理器ic中的内部电路和/或泄漏可能导致耦合到将处于第二电压电平的节点的处理器ic的子电路处于或低于第一电压电平。

17.诸如此类的情况给电源转换器带来问题,因为控制器可以通过将转换器的占空比从对应于零伏的值倾斜以满足期望输出电压的占空比来控制电源转换器。许多电源转换器采用同步整流,这允许在电源转换器的某些状态期间电流从电源转换器的输出端流向电源转换器的输入端。虽然同步整流在电源转换器的稳态操作期间是有益的,但当输出端处存在预偏置电压电平时,它会在转换器启动期间引起问题。问题出现是因为启动时的占空比与电源转换器输出端处的电压不对应。这种电压电平差异导致来自电源转换器输出端的电流从电源转换器的输出端流向输入端(例如,电流相对于转换器为负,电源转换器从负载处的预偏置电压电平吸收电流)。这是不利的,因为用于电源转换器的控制器可能不被设计为支持在不连续传导模式(dcm)操作下的控制。传统的pwm方法无法适应dcm操作中的这种负电流,因为在连接到电源转换器之前将pwm信号设置为期望值是不切实际的。

18.本文的示例允许电源转换器在连接到预偏置输出时启动。本文的示例提供了一种设备,包括:包括反馈网络和差分差值放大器(dda)的误差放大器,dda包括第一输入端、第二输入端、第三输入端、第四输入端和输出端,dda的第二输入端被配置为耦合到电源转换器的输出端,dda的第三输入端配置为耦合到电压发生器的第一输出端,以及反馈网络耦合到dda的第三输入端、dda的第四输入端以及dda的输出端;包括控制端子的多路复用器,该多路复用器被配置为耦合到电压发生器的第二输出端,该多路复用器耦合到dda的第二输入端和dda的第一输入端;包括控制端子的第一开关,该第一开关与反馈网络并联耦合;包括控制端子的第二开关,该第二开关被配置为耦合到延迟单元和振荡器;包括输出端的触

发器,该触发器被配置为耦合到电压发生器的第二输出端、电源转换器的输出端,并且触发器的输出端耦合到多路复用器的控制端子、第一开关的控制端子以及第二开关的控制端子。

19.本文的方法、设备和制品不将误差放大器的输出钳位到对应于高于输出电压电平的电压电平的指定值,而是本文的示例允许误差放大器基于参考电压控制dpwm中的延迟单元的持续时间,直到dpwm的脉冲宽度等于或高于与电源转换器的输出端上的电压电平相关联的值,该电压电平大于或等于预偏置电压。此外,本文的示例防止误差放大器回转到误差放大器两端的电压电平,从而防止电源转换器的输出端上的瞬变。

20.此外,本文的示例通过禁用电源转换器直到对应于电源转换器的软启动电压等于或大于对应于预偏置电压的电压电平来防止负电流(例如,反向电流)。与描述一致,耦合被定义为直接或间接连接(例如,通过一个或多个中间结构和/或层,诸如电阻器、电容器、电感器、晶体管、电压钳、开关、缓冲放大器等)。与描述一致,软启动和/或其派生词(例如,软

‑

启动(soft start,soft

‑

start,soft

‑

startup,soft starting)等)是指当开关开始导通并防止电流电平超过不会损坏开关的部件或耦合到开关的部件的预定和/或感测值时控制电流流动速率并因此控制输出电压的变化速率的结构或功能。与描述一致,相等被定义为两个或更多个数量在彼此的百分比容差范围内(例如,5%的容差)之间的关系。

21.图1是包括示例控制器102的示例电源转换器系统100的框图。示例电源转换器系统100进一步包括示例功率级104、示例负载136、示例电源138和示例电压输入端140。示例控制器102控制功率级104以向负载136提供期望电压电平,其中期望电压电平基于由控制器102在电压输入端140处获得的预设或预定电压电平v

set

。示例控制器102包括示例参考电压发生器106、示例误差放大器108、示例延迟单元110、示例振荡器112、示例模数转换器(adc)114、示例前馈电压控制器116、示例分压器117、示例比较器118(包括示例第一输入端120、示例第二输入端122和示例输出端124)、示例锁存器125、示例第一开关126、示例第一反相器127、示例第二开关128、示例第三开关130、示例第二反相器131、示例第四开关132、示例第五开关134和示例第三反相器135。

22.在图1中,示例控制器102耦合到示例功率级104。在图1中,示例功率级104耦合到示例控制器102、示例负载136和示例电源138。在图1中,示例参考电压发生器106耦合到示例电压输入端140、经由示例第二开关128和示例第三开关130耦合到示例误差放大器108、耦合到示例前馈电压控制器116和示例比较器118的第二输入端122。在图1中,示例误差放大器108经由示例第一开关126耦合到示例功率级104、经由示例第二开关128和示例第三开关130耦合到示例参考电压发生器106、耦合到示例延迟单元110并且耦合到示例第四开关132。

23.在图1中,示例延迟单元110耦合到示例误差放大器108、经由示例第五开关134耦合到示例振荡器112、耦合到示例adc 114并耦合到示例功率级104。在图1中,示例振荡器112经由示例第五开关134耦合到示例延迟单元110并耦合到示例前馈电压控制器116。在图1中,示例adc 114耦合到示例延迟单元110和示例前馈电压控制器116。在图1中,示例前馈电压控制器116耦合到示例参考电压发生器106、示例振荡器112、示例adc 114和示例电源138。在图1中,示例比较器118的第一输入端120经由分压器117耦合到示例功率级104。此外,在图1的示例中,示例比较器118的第二输入端122耦合到示例参考电压发生器106。在图

1中,比较器118的输出端124耦合到示例锁存器125。示例锁存器125经由第一反相器127耦合到示例第一开关126、耦合到示例第二开关128、经由第二反相器131耦合到示例第三开关130、耦合到示例第四开关132并经由第三反相器135耦合到示例第五开关134。

24.在图1中,示例第一开关126、示例第二开关128、示例第三开关130、示例第四开关132和示例第五开关134中的每一个包括第一端子(例如,电流端子)、第二端子(例如,电流端子)和第三端子(例如,控制端子)。在所示示例中,示例第一开关126的第一端子经由分压器117耦合到示例功率级104,示例第一开关126的第二端子耦合到示例误差放大器108,并且示例第一开关126的第三端子经由锁存器125和第一反相器127耦合到示例比较器118的输出端124。在所示示例中,示例第二开关128的第一端子耦合到示例参考电压发生器106,示例第二开关128的第二端子耦合到示例误差放大器108,并且示例第二开关128的第三端子经由锁存器125耦合到示例比较器118的输出端124。在所示示例中,示例第三开关130的第一端子耦合到示例参考电压发生器106,示例第三开关130的第二端子耦合到示例误差放大器108,并且示例第三开关130的第三端子经由锁存器125和第二反相器131耦合到示例比较器118的输出端124。在所示示例中,示例第四开关132的第一端子耦合到示例误差放大器108,示例第四开关132的第二端子耦合到示例误差放大器108,并且示例第四开关132的第三端子经由锁存器125耦合到示例比较器118的输出端124。在所示示例中,示例第五开关134的第一端子耦合到示例振荡器112,示例第五开关134的第二端子耦合到示例延迟单元110,并且示例第五开关134的第三端子经由锁存器125和第三反相器135耦合到示例比较器118的输出端124。

25.在图1中,功率级104是由控制器102控制的dc

‑

dc转换器。功率级104从电源138接收要转换的功率。在本文的示例中,功率级104是dc

‑

dc电源转换器,诸如升压转换器、降压

‑

升压转换器等。可替代地,功率级104可以是在任何合适的电信应用、数据通信应用、服务器、汽车应用(例如,电动汽车(ev)中的牵引逆变器)、工业应用(例如,桥式逆变器、电机驱动等等。)中的任何功率级(例如,dc

‑

dc转换器、ac

‑

dc转换器、ac

‑

ac转换器等)。在其他示例中,功率级104可以是两个同步开关、附加电源转换器控制逻辑或其组合。在图1中,功率级104产生输出电压信号。此外,输出电压信号由控制器102,更具体地,由误差放大器108作为反馈电压信号vfb进行监测。在图1中,负载136可以是ev中的led阵列、马达、服务器、工业和/或住宅电器、数据通信服务器或任何合适的负载。在其他示例中,负载136可以是一个或多个电感器、电容器、电阻器或其组合以对功率级104的输出进行滤波。

26.在图1中,示例电源138是未调节的线性电源。例如,电源138是二极管整流器的输出。在其他示例中,可以使用适合于该应用的其他电源。示例电源138生成输入电压信号v

in

。

27.在图1中,参考电压发生器106是一个或多个电压调节器、放大器、比较器和调节控制器102中的一个或多个电压电平的其他逻辑的组合。例如,参考电压发生器106生成第一电压电平的第一电压信号v

soft

。例如,第一电压信号v

soft

处于对应于功率级104的软启动的参考电压电平,使得功率级104斜升至期望和/或预定的电压电平(例如,对应于v

set

信号的电压电平的电压电平)。此外,示例参考电压发生器106生成微调电压信号v

ton

(例如,处于第二电压电平)以用作误差放大器108的参考电压电平。在本文的示例中,由参考电压发生器106生成的微调电压信号v

ton

是温度补偿的(例如,响应于外部温度和/或硅管芯温度的变化而改变和/或以其他方式改变)。例如,随着延迟单元110的温度从先前的温度升高和/或降

114来设置由延迟单元110生成的pwm信号的脉冲宽度的延迟(例如,持续时间)。以这种方式,延迟单元110通过向示例振荡器信号引入延迟来生成pwm信号,该延迟基于前馈电压控制器116的输出(例如,基于输入电压v

in

、由振荡器112生成的信号以及第一电压信号v

soft

)。

33.在图1中,示例分压器117是电阻分压器网络,其允许功率级104的输出电压处的电压电平被误差放大器108和/或更一般地,被控制器102测量和/或以其他方式监测而没有损坏误差放大器108和/或更一般地说,控制器102的可能性。

34.在图1中,比较器118是模拟比较器。在其他示例中,比较器118是数字比较器、比较器控制器、触发器(例如,施密特触发器)、一个或多个集成电路、逻辑电路、微处理器、图形处理单元(gpu)、数字信号处理器(dsp),或来自任何所期望系列或制造商的控制器。比较器118可以是基于半导体(例如,基于硅)的器件。比较器118比较在第一输入端120处接收到的反馈电压信号v

fb

和在第二输入端122处接收到的第一电压信号v

soft

,并确定第一电压信号v

soft

的幅值是否在反馈电压信号v

fb

的阈值内。例如,阈值电压对应于基于应用的第一电压信号v

soft

的幅值与反馈电压信号v

fb

的幅值之间的可接受的差值。示例比较器118还至少基于第一电压信号v

soft

和反馈电压信号v

fb

的比较经由在输出端124处生成的控制信号来配置第一开关126、第二开关128、第三开关130、第四开关132或第五开关134中的一个或多个。在附加或替代示例中,示例比较器118在控制器102的操作开始时经由在输出端124处生成的控制信号配置第一开关126、第二开关128、第三开关130、第四开关132或第五开关134中的一个或多个。

35.在图1中,锁存器125是在锁存器125的输出端处保持与在锁存器125的输入端处接收到的逻辑值相对应的逻辑值的器件。例如,锁存器125是sr锁存器。在其他示例中,锁存器125是d触发器、jk锁存器、门控sr锁存器、门控jk锁存器、门控d触发器、厄尔(earle)锁存器或任何其他合适的锁存器。

36.在图1中,第一开关126、第二开关128、第三开关130、第四开关132和第五开关134中的每一个可以由晶体管来实现。例如,第一开关126、第二开关128、第三开关130、第四开关132和第五开关134中的每一个是负沟道(n沟道)金属氧化物半导体场效应晶体管(mosfet)。在其他示例中,第一开关126、第二开关128、第三开关130、第四开关132和第五开关134可以由双极结晶体管(bjt)、结栅极场效应晶体管(jfet)、异质结双极晶体管(hbt)、任何适合该应用的晶体管和/或其任何组合来实现。尽管可以使用bjt、jfet、hbt或任何合适的晶体管的许多组合来实现第一开关126、第二开关128、第三开关130、第四开关132或第五开关134中的一个或多个,但可能需要在特定控制器中以相同的开关类型来实现第一开关126、第二开关128、第三开关130、第四开关132和第五开关134中的每一个(例如,全部n型bjt,全部p型bjt、全部正沟道(p沟道)mosfet等)。在进一步的示例中,第一开关126、第二开关128、第三开关130、第四开关132、第五开关134或其任意组合中的每一个被实现为一个或多个多路复用器。

37.在图1中,第一反相器127、第二反相器131和第三反相器135中的每一个是将在第一反相器127、第二反相器131和第三反相器135的输入端处接收到的逻辑值分别取反并且在第一反相器127、第二反相器131和第三反相器135的输出端处分别输出反转逻辑值的器件。在图1中,第一反相器127、第二反相器131和第三反相器135中的每一个都是非(not)逻辑门。在另外的示例中,第一反相器127、第二反相器131和第三反相器135中的每一个可以

是一个或多个逻辑门/逻辑电路的组合,其将接收到的信号的逻辑值取反并输出反转后的逻辑值。在模拟实施方式中,第一反相器127、第二反相器131和第三反相器135中的每一个都可以是反相放大器。

38.在图1中,在操作时,示例比较器118将误差放大器108配置为电压跟随器,其中微调电压信号v

ton

作为输入。例如,示例比较器118配置第一开关126、第二开关128、第三开关130、第四开关132和第五开关134以将误差放大器108配置为作为电压跟随器进行操作。更具体地,示例比较器118断开第一开关126,闭合第二开关128,断开第三开关130,闭合第四开关132,并断开第五开关134。通过配置第一开关126、第二开关128、第三开关130、第四开关132或第五开关134中的一个或多个,比较器118禁止误差放大器108基于反馈电压信号v

fb

控制延迟单元110中的每个延迟单元的持续时间。相反,通过配置第一开关126、第二开关128、第三开关130、第四开关132或第五开关134中的一个或多个,比较器118启用误差放大器108以基于微调电压信号v

fb

控制延迟单元110中的每个延迟单元的持续时间。此外,示例前馈电压控制器116基于第一电压信号v

soft

除以输入电压信号v

in

并乘以振荡器112的周期来设置延迟单元110的输出(例如,pwm信号导通时间)。此外,通过配置第一开关126、第二开关128、第三开关130、第四开关132或第五开关134中的一个或多个,示例比较器118通过从延迟单元110断开振荡器112来禁用延迟单元110的pwm信号。

39.在图1中,在操作时,比较器118监测第一电压信号v

soft

以确定第一电压信号v

soft

是否已启动软启动功能。例如,比较器118监测第一电压信号v

soft

并且当比较器118检测到第一电压信号v

soft

上的电压正变化时,比较器118确定第一电压信号v

soft

已经启动软启动功能。当示例比较器118确定第一电压信号v

soft

已经启动软启动功能(例如,第一电压信号v

soft

开始上升)时,示例比较器118监测反馈电压信号v

fb

和第一电压信号v

soft

以确定第一电压信号v

soft

是否在反馈电压信号v

fb

的阈值差之内。

40.在图1中,在操作时,当示例比较器118确定第一电压信号v

soft

在反馈电压信号v

fb

的阈值差之内时,示例比较器118启用误差放大器108以基于反馈电压信号v

fb

和第一电压信号v

soft

来控制功率级104。例如,当示例比较器118确定第一电压信号v

soft

在反馈电压信号v

fb

的阈值差之内时,示例比较器118配置第一开关126、第二开关128、第三开关130、第四开关132或第五开关134中的一个或多个。更具体地,当示例比较器118确定第一电压信号v

soft

在反馈电压信号v

fb

的阈值差之内时,示例比较器118闭合第一开关126、断开第二开关128、闭合第三开关130、断开第四开关132并闭合第五开关134。通过配置第一开关126、第二开关128、第三开关130、第四开关132或第五开关134中的一个或多个,比较器118启用误差放大器108以基于反馈电压信号v

fb

和第一电压信号v

soft

控制延迟单元110中的每个延迟单元的持续时间。此外,通过配置(例如,断开和/或闭合)第一开关126、第二开关128、第三开关130、第四开关132和第五开关134中的一个或多个,示例比较器118启用延迟单元110的pwm信号。

41.图2是示例电源转换器系统200的示意图,其示出了图1的控制器102的进一步细节。电源转换器系统200包括示例控制器102、示例功率级104、示例负载136、示例电源138和示例电压输入端140。示例控制器102包括示例参考电压发生器106、示例误差放大器108、示例延迟单元110、示例振荡器112、示例adc 114、示例前馈电压控制器116、示例分压器117、示例比较器118(包括示例第一输入端120、示例第二输入端122和示例输出端124)、示例锁

存器125、示例第一开关126、示例第一反相器127、示例第二开关128、示例第三开关130、示例第二反相器131、示例第四开关132、示例第五开关134和示例第三反相器135。

42.在图2中,示例功率级104包括示例第六开关202、示例第七开关204、示例电感器206、示例第一电容器208、示例接地参考节点210和示例反相器212。示例误差放大器108包括示例第一电阻器214、示例第二电容器216、示例运算放大器218和示例第二电阻器220。示例运算放大器218包括反相输入端222、非反相输入端224和输出端226。在图2中,第一开关126、第二开关128、第三开关130、第四开关132、第五开关134、第六开关202和第七开关204中的每一个包括第一端子(例如,电流端子)、第二端子(例如,电流端子)和第三端子(例如,控制端子)。

43.在图2中,示例控制器102耦合到示例功率级104。示例功率级104耦合到示例控制器102、示例负载136、示例电源138和示例电压输入端140。

44.在图2中,示例第六开关202的第二端子耦合到电源138,示例第六开关202的第一端子耦合到开关节点sw,并且示例第六开关202的第三端子耦合到延迟单元110。在图2中,示例第七开关204的第二端子耦合到开关节点sw,示例第七开关204的第一端子耦合到接地参考节点210,并且示例第七开关204的第三端子耦合到反相器212。示例电感器206耦合在开关节点sw和输出电压节点v

o

之间。示例第一电容器208耦合在示例输出电压节点v

o

和接地参考节点210之间。在图2中,接地参考节点210耦合到第一电容器208和第七开关204的第一端子。示例反相器212耦合到第七开关204的第三端子和延迟单元110。

45.在图2中,示例参考电压发生器106经由第二开关128和第三开关130耦合到运算放大器218的非反相输入端224、耦合到比较器118的第二输入端122并耦合到前馈电压控制器116。在图2中,第一电阻器214串联耦合到第二电容器216。共同地,第一电阻器214和第二电容器216并联耦合在运算放大器218的反相输入端222和输出端226之间并且形成运算放大器反馈网络。在图2中,第二电容器216与第四开关132的第一端子和第二端子并联耦合。在替代示例中,第四开关132的第一端子和第二端子与第一电阻器214和第二电容器216并联耦合。在所示示例中,运算放大器218的反相端子222耦合到第一开关126的第二端子和第一电阻器214。运算放大器218的示例非反相端子224经由第二开关128和第三开关130耦合到参考电压发生器106。在所示示例中,第二电阻器220经由分压器117耦合到第一开关126的第一端子和功率级104的输出电压节点v

o

。

46.在图2中,示例延迟单元110耦合到运算放大器218的输出端226、经由示例第五开关134耦合到示例振荡器112、耦合到示例adc 114、耦合到示例第六开关202的第三端子和反相器212。示例振荡器112经由示例第五开关134耦合到示例延迟单元110并耦合到示例前馈电压控制器116。示例adc 114耦合到示例延迟单元110和示例前馈电压控制器116。示例前馈电压控制器116耦合到示例参考电压发生器106、示例振荡器112、示例adc 114和示例电源138。比较器118的示例第一输入端120经由分压器117耦合到示例功率级104的输出电压节点v

o

,示例比较器118的第二输入端122耦合到示例参考电压发生器106,并且比较器118的输出端124耦合到示例锁存器125。锁存器125经由第一反相器127耦合到示例第一开关126的第三端子、耦合到示例第二开关128的第三端子、经由第二反相器131耦合到示例第三开关130的第三端子、耦合到示例第四开关132的第三端子并且经由第三反相器135耦合到示例第五开关134的第三端子。

47.在图2中,示例第一开关126的第一端子经由第二电阻器220和分压器117耦合到示例功率级104的输出电压节点v

o

。示例第一开关126的第二端子耦合到运算放大器218的反相端子222。示例第一开关126的第三端子经由锁存器125和第一反相器127耦合到示例比较器118的输出端124。在所示示例中,示例第二开关128的第一端子耦合到示例参考电压发生器106,示例第二开关128的第二端子耦合到示例运算放大器218的非反相端子224。示例第二开关128的第三端子经由锁存器125耦合到示例比较器118的输出端124。在所示示例中,示例第三开关130的第一端子耦合到示例参考电压发生器106,示例第三开关130的第二端子耦合到示例运算放大器218的非反相端子224。示例第三开关130的第三端子经由锁存器125和第二反相器131耦合到示例比较器118的输出端124。在所示示例中,示例第四开关132的第一端子和第二端子耦合到第二电容器216,使得第四开关132并联耦合到第二电容器216。示例第四开关132的第三端子经由锁存器125耦合到示例比较器118的输出端124。在其他示例中,示例第四开关132的第一端子和第二端子耦合到第一电阻器214和第二电容器216,使得第四开关132并联耦合到第一电阻器214和第二电容器216。在所示示例中,示例第五开关134的第一端子耦合到示例振荡器112,示例第五开关134的第二端子耦合到示例延迟单元110。示例第五开关134的第三端子经由锁存器125和第三反相器135耦合到示例比较器118的输出端124。

48.在图2中,功率级104是dc

‑

dc降压转换器。dc电源转换器通过将输入能量暂时存储在电子组件(例如电感器、电容器、电感元件、电容元件等)中并且然后在不同电压下在负载136处释放该能量来起作用。在功率级104中,反相器212是非(not)门。示例反相器212确保当第六开关202闭合时第七开关204断开,并且当第七开关204闭合时第六开关202被启用。在其他示例中,反相器212可以是确保第六开关202和第七开关204不会同时闭合的逻辑电路的组合。

49.在图2中,当第六开关202闭合而第七开关204断开时,电流从电源138(例如,输入电压信号v

in

)流向以线性速率充电的电感器206。当电感器206正在充电时,电感器206在由流过电感器206的电流i

sw

产生的磁场中储存能量。而且,当第六开关202闭合而第七开关204断开时,第一电容器208也充电到期望的输出电压电平,并且负载136被提供有来自电源138的电流。当第六开关202断开时,第七开关204闭合,使得电流i

sw

可以继续流向负载136。存储在电感器206的磁场中的能量消散,并且随着它消散,生成流过功率级104并流向负载136的电流(例如,i

sw

)。当第六开关202断开时,流经功率级104的电流i

sw

将与流经第七开关204的电流大小相等。来自电感器206的电流流向第一电容器208和负载136,而第一电容器208在功率级104的输出电压节点v

o

处保持期望的输出电压并且负载136接收功率。电流i

sw

通过流经接地参考节点210和第七开关204返回电感器206。上述开关模式允许连续电流流入负载136。

50.在图2中,负载136是微控制器的子电路。在其他示例中,负载136可以是ev中的led阵列、马达、服务器、工业和/或住宅电器、数据通信服务器或任何合适的负载。

51.在图2中,示例电源138是未调节的线性电源。例如,电源138是二极管整流器的输出。在其他示例中,可以使用适合于该应用的其他电源。示例电源138生成输入电压信号v

in

。

52.在图2中,参考电压发生器106是一个或多个电压调节器、放大器、比较器和其他调节控制器102中的一个或多个电压电平的逻辑的组合。例如,参考电压发生器106生成第一

电压电平的第一电压信号v

soft

。例如,第一电压信号v

soft

处于对应于功率级104的软启动的参考电压电平,使得功率级104斜升至期望和/或预定的电压电平(例如,对应于v

set

信号的电压电平的电压电平)。此外,示例参考电压发生器106生成微调电压信号v

ton

(例如,处于第二电压电平)以用作运算放大器218的参考电压电平。在本文的示例中,由参考电压发生器106生成的微调电压信号v

ton

是温度补偿的(例如,响应于外部温度和/或硅管芯温度的变化而改变和/或以其他方式改变)。例如,随着延迟单元110的温度从先前的温度升高和/或降低,由参考电压发生器106生成的微调电压信号v

ton

相应地改变以确保在所有温度正确操作。例如,由参考电压发生器106生成的微调电压信号v

ton

对应于每个延迟单元110的期望持续时间(例如,1.2纳秒)。此外,由示例参考电压发生器106生成的微调电压信号v

ton

在不同温度变化,以保持每个延迟单元110的期望持续时间。例如,当延迟单元110的温度升高时,由参考电压发生器106生成的微调电压信号v

ton

减小以保持延迟单元110的期望持续时间。在替代方案中,当示例延迟单元110的温度降低时,由参考电压发生器106生成的微调电压信号v

ton

增大以在延迟单元110上保持期望的持续时间。在附加或替代示例中,由参考电压发生器106生成的微调电压信号v

ton

增大以补偿延迟单元110的温度上升并且减小以补偿延迟单元110的温度下降。

53.在图2中,示例误差放大器108包括第一电阻器214、第二电容器216、运算放大器218和第二电阻器220。共同地,第一电阻器214、第二电容器216、运算放大器218和第二电阻器220基于来自示例功率级104和参考电压发生器106的一个或多个输入在输出端226处生成控制信号v

error

。误差放大器108经由分压器117监测功率级104的输出电压节点v

o

处的输出电压电平以作为反馈电压信号v

fb

。在图2中,第一电阻器214、第二电容器216和第二电阻器220是运算放大器反馈网络,其设置误差放大器108的增益,使得误差放大器108可以控制功率级104以在功率级104的输出电压节点v

o

处生成期望的输出电压电平(例如,对应于v

set

信号的电压电平)。在稳态操作期间,如果功率级104的输出电压节点v

o

处的输出电压信号偏离期望电平(例如,如果反馈电压信号v

fb

在瞬变期间增大和/或减小到高于正常操作电平),则运算放大器反馈网络(例如,第一电阻器214、第二电容器216和第二电阻器220)使运算放大器218在输出端226处生成控制信号v

error

以调节延迟单元110中包括的每个延迟单元的延迟的持续时间。

54.在图2中,示例延迟单元110包括多个示例延迟单元以生成pwm信号。在本文的示例中,延迟单元110通过基于输入电压信号v

in

、振荡器112生成的信号和第一电压信号v

soft

(例如,更通常地,adc 114的输出)中的一个或多个向示例振荡器信号引入延迟来生成pwm信号。延迟单元110用于调节到功率级104的pwm信号的占空比以向示例负载136提供功率。例如,adc 114的输出确定被选择(例如,启用)的延迟单元110的数量。pwm信号的占空比对应于被启用的延迟单元110的数量乘以每个延迟单元110的持续时间。在图2中,延迟单元110中的每个延迟单元的持续时间是基于误差放大器108生成的控制信号确定的。例如,控制信号上的较高电压电平对应于每个延迟单元110的较长持续时间,而控制信号上的较低电压电平对应于每个延迟单元110的较短持续时间。

55.在图2中,振荡器112是锁相环振荡器。在其他示例中,振荡器112是电容器(rc)振荡器、环形振荡器、晶体振荡器或用于应用的任何其他合适的振荡器。示例振荡器112产生振荡信号。在图2中,振荡信号可以是为启动pwm信号的生成和/或以其他方式设置延迟单元

110操作的频率而生成的周期性和/或非周期性信号。例如,当振荡器112输出振荡信号时,延迟单元110在振荡信号处于下降沿时在pwm信号上生成相应的上升沿。在这样的示例中,pwm信号在与激活的延迟单元110的数量相关联的延迟持续时间内保持在逻辑高值。激活的延迟单元110的数量由示例adc 114指示。

56.在图2中,示例adc 114是电流模数转换器。adc 114将模拟电流电平转换为数字输出(例如,二进制计数值)。例如,示例adc 114将模拟电流电平转换为八位二进制信号以指示待激活的延迟单元110的数量。在本文的其他示例中,adc 114可以是指示待激活的延迟单元110的数量的任何其他合适的解码器。

57.在图2中,示例前馈电压控制器116是模拟乘法器。示例前馈电压控制器116产生供adc 114使用的模拟电流信号。例如,前馈电压控制器116基于第一电压信号v

soft

、输入电压信号v

in

、由振荡器112生成的振荡器信号的频率中的一个或多个和对应于比例因子的一个或多个常数产生模拟电流信号。比例因子适合于控制器102的设计。例如,比例因子与每个延迟单元110的持续时间有关。示例前馈电压控制器116经由adc 114设置待激活的延迟单元110的数量。以此方式,示例前馈电压控制器116通过设置待激活的延迟单元110的数量经由adc 114来设置由延迟单元110生成的pwm信号的脉冲宽度的延迟(例如,持续时间)。以这种方式,延迟单元110通过向示例振荡器信号引入延迟来生成pwm信号,该延迟基于前馈电压控制器116的输出(例如,基于输入电压vin、由振荡器112生成的信号、以及第一电压信号v

soft

)。

58.在图2中,示例分压器117是电阻分压器网络,其允许输出电压节点v

o

处的电压电平被运算放大器218和/或更一般地,被误差放大器108测量和/或以其他方式监测而没有损坏运算放大器218和/或更一般地说,误差放大器108的可能性。

59.在图2中,比较器118是包括第一输入端120、第二输入端122和输出端124的模拟比较器。在图2中,比较器118比较在第一输入端120处接收到的反馈电压信号v

fb

和在第二输入端122处接收到的第一电压信号v

soft

,并确定第一电压信号v

soft

的幅值是否在反馈电压信号v

fb

的阈值内。例如,阈值电压对应于基于应用的第一电压信号v

soft

的幅值与反馈电压信号v

fb

的幅值之间的可接受的差值。示例比较器118还基于第一电压信号v

soft

和反馈电压信号v

fb

的比较经由在输出端124处生成的控制信号来配置第一开关126、第二开关128、第三开关130、第四开关132或第五开关134中的一个或多个。在图2中,示例比较器118在控制器102的操作开始时经由在输出端124处生成的控制信号配置第一开关126、第二开关128、第三开关130、第四开关132或第五开关134中的一个或多个。

60.在图2中,锁存器125是在锁存器125的输出端处保持与在锁存器125的输入端处接收到的逻辑值相对应的逻辑值的器件。例如,锁存器125是sr锁存器。在其他示例中,锁存器125是d触发器、jk锁存器、门控sr锁存器、门控jk锁存器、门控d触发器、厄尔(earle)锁存器或任何其他合适的锁存器。

61.在图2中,第一开关126、第二开关128、第三开关130、第四开关132、第五开关134、第六开关202和第七开关204中的每一个可以由晶体管来实现。例如,第一开关126、第二开关128、第三开关130、第四开关132、第五开关134和第六开关202中的每一个都是n沟道mosfet。在图2中,第七开关204是p沟道mosfet。在其他示例中,第一开关126、第二开关128、第三开关130、第四开关132、第五开关134、第六开关202和第七开关204是bjt、jfet、hbt、用

于应用的任何合适晶体管和/或其任何组合。尽管可以使用bjt、jfet、hbt或任何合适的晶体管的许多组合来实现第一开关126、第二开关128、第三开关130、第四开关132或第五开关134中的一个或多个,但可能需要在特定控制器中以相同的开关类型来实现第一开关126、第二开关128、第三开关130、第四开关132和第五开关134中的每一个(例如,全部n型bjt,全部p型bjt、全部p沟道mosfet等)。在进一步的示例中,第一开关126、第二开关128、第三开关130、第四开关132、第五开关134或其任意组合中的每一个被实现为一个或多个多路复用器。

62.在图2中,第一反相器127、第二反相器131和第三反相器135中的每一个是将在第一反相器127、第二反相器131和第三反相器135的输入端处接收到的逻辑值分别取反并且在第一反相器127、第二反相器131和第三反相器135的输出端处分别输出反转逻辑值的器件。在图2中,第一反相器127、第二反相器131和第三反相器135中的每一个都是非(not)逻辑门。在另外的示例中,第一反相器127、第二反相器131和第三反相器135中的每一个可以是一个或多个逻辑门/逻辑电路的组合,其将接收到的信号的逻辑值取反并输出反转后的逻辑值。在模拟实施方式中,第一反相器127、第二反相器131和第三反相器135中的每一个都可以是反相放大器。

63.在图2中,在操作时,示例比较器118将误差放大器108配置为电压跟随器,其中微调电压信号v

ton

作为到非反相输入端224的输入。例如,示例比较器118配置第一开关126、第二开关128、第三开关130、第四开关132和第五开关134以将误差放大器108配置为作为电压跟随器进行操作。更具体地,示例比较器118断开第一开关126,闭合第二开关128,断开第三开关130,闭合第四开关132,并断开第五开关134。通过配置第一开关126、第二开关128、第三开关130、第四开关132或第五开关134中的一个或多个,比较器118禁止误差放大器108基于反馈电压信号v

fb

控制延迟单元110中的每个延迟单元的持续时间。相反,通过配置第一开关126、第二开关128、第三开关130、第四开关132或第五开关134中的一个或多个,比较器118启用误差放大器108以基于微调电压信号v

fb

控制延迟单元110中的每个延迟单元的持续时间。此外,示例前馈电压控制器116基于第一电压信号v

soft

除以输入电压信号v

in

并乘以振荡器112的周期来设置延迟单元110的输出(例如,pwm信号导通时间)。此外,通过配置第一开关126、第二开关128、第三开关130、第四开关132或第五开关134中的一个或多个,示例比较器118通过从延迟单元110断开振荡器112来禁用延迟单元110的pwm信号。

64.在图2中,在操作时,比较器118监测第一电压信号v

soft

以确定第一电压信号v

soft

是否已启动软启动功能。例如,比较器118监测第一电压信号v

soft

并且当比较器118检测到第一电压信号v

soft

上的电压正变化时,比较器118确定第一电压信号v

soft

已经启动软启动功能。当示例比较器118确定第一电压信号v

soft

已经启动软启动功能(例如,第一电压信号v

soft

开始上升)时,示例比较器118监测反馈电压信号v

fb

和第一电压信号v

soft

以确定第一电压信号v

soft

是否在反馈电压信号v

fb

的阈值差之内。

65.在图2中,在操作时,当示例比较器118确定第一电压信号v

soft

在反馈电压信号v

fb

的阈值差之内时,示例比较器118启用误差放大器108以基于反馈电压信号v

fb

和第一电压信号v

soft

来控制功率级104。例如,当示例比较器118确定第一电压信号v

soft

在反馈电压信号v

fb

的阈值差之内时,示例比较器118配置第一开关126、第二开关128、第三开关130、第四开关132或第五开关134中的一个或多个。更具体地,当示例比较器118确定第一电压信号v

soft

在反馈电压信号v

fb

的阈值差之内时,示例比较器118闭合第一开关126、断开第二开关128、闭合第三开关130、断开第四开关132并闭合第五开关134。通过配置第一开关126、第二开关128、第三开关130、第四开关132或第五开关134中的一个或多个,比较器118启用误差放大器108以基于反馈电压信号v

fb

和第一电压信号v

soft

控制延迟单元110中的每个延迟单元的持续时间。此外,通过配置(例如,断开和/或闭合)第一开关126、第二开关128、第三开关130、第四开关132和第五开关134中的一个或多个,示例比较器118启用延迟单元110的pwm信号。

66.图3是示例电源转换器系统300的示意图,其示出了图1的控制器102的替代细节。电源转换器系统300包括示例控制器102、示例功率级104、示例负载136、示例电源138和示例电压输入端140。示例控制器102包括示例参考电压发生器106、示例误差放大器108、示例延迟单元110、示例振荡器112、示例adc 114、示例前馈电压控制器116、示例分压器117、示例触发器302、示例锁存器125、示例第四开关132、示例第五开关134、示例第三反相器133和示例第八开关310。示例触发器302包括示例第一输入端304、示例第二输入端306和示例输出端308。

67.在图3中,示例功率级104包括示例第六开关202、示例第七开关204、示例电感器206、示例第一电容器208、示例接地参考节点210和示例反相器212。示例误差放大器108包括示例第一电阻器214、示例第二电容器216、示例差分差值放大器312和示例第二电阻器220。示例差分差值放大器312包括第一非反相输入端314、第一反相输入端316、第二非反相输入端318、第二反相输入端320和输出端322。在图2中,第四开关132、第五开关134、第六开关202和第七开关204包括第一端子(例如,电流端子)、第二端子(例如,电流端子)和第三端子(例如,控制端子)。在图3中,第八开关310包括第一端子(例如,电流端子)、第二端子(例如,电流端子)、第三端子(例如,电流端子)和第四端子(例如,控制端子)。

68.在图3中,示例控制器102耦合到示例功率级104。示例功率级104耦合到示例控制器102、示例负载136、示例电源138和示例电压输入端140。

69.在图3中,示例第六开关202的第二端子耦合到电源138,示例第六开关202的第一端子耦合到开关节点sw,示例第六开关202的第三端子耦合到延迟单元110。在图3中,示例第七开关204的第二端子耦合到开关节点sw,示例第七开关204的第一端子耦合到接地参考节点210,示例第七开关204的第三端子耦合到反相器212。示例电感器206耦合在开关节点sw和输出电压节点v

o

之间。示例第一电容器208耦合在示例输出电压节点v

o

和接地参考节点210之间。接地参考节点210耦合到第一电容器208和第七开关204的第一端子。示例反相器212耦合到第七开关204的第三端子和延迟单元110。

70.在图3中,示例参考电压发生器106经由第八开关310耦合到差分差值放大器312的第一非反相输入端314、耦合到差分差值放大器312的第二非反相输入端318、经由第二电阻器220耦合到差分差值放大器312的第二反相输入端316、耦合到触发器302的第一输入端304、耦合到前馈电压控制器116和功率级104。在图3中,第一电阻器214串联耦合到第二电容器216。共同地,第一电阻器214和第二电容器216并联耦合在差分差值放大器312的第二反相输入端320和输出端322之间并且形成差分差值放大器反馈网络。在图3中,第二电容器216与第四开关132的第一端子和第二端子并联耦合。在替代示例中,第四开关132的第一端子和第二端子与第一电阻器214和第二电容器216并联耦合。在所示示例中,差分差值放大

器312的第一非反相端子314耦合到第八开关310的第三端子。在图3中,差分差值放大器312的第一反相输入端316经由分压器117耦合到功率级104的输出电压节点v

o

。在图3中,差分差值放大器312的第二非反相输入端318耦合到参考电压发生器106。在图3中,差分差值放大器312的第二反相输入端320经由第二电阻器220耦合到参考电压发生器106。在所示示例中,第二电阻器220耦合到参考电压发生器106和差分差值放大器312的第二反相输入端320。

71.在图3中,示例延迟单元110耦合到差分差值放大器312的输出端322、经由示例第五开关134耦合到示例振荡器112、耦合到示例adc 114、耦合到示例第六开关202的第三端子和反相器212。示例振荡器112经由示例第五开关134耦合到示例延迟单元110并耦合到示例前馈电压控制器116。示例adc 114耦合到示例延迟单元110和示例前馈电压控制器116。示例前馈电压控制器116耦合到示例参考电压发生器106、示例振荡器112、示例adc 114和示例电源138。触发器302的示例第一输入端304耦合到参考电压发生器106(例如,第一电压信号v

soft

),示例触发器302的第二输入端306耦合到功率级104的输出电压节点v

o

,并且触发器302的输出端308耦合到示例锁存器125。锁存器125耦合到示例第四开关132的第三端子、经由第三反相器135耦合到示例第五开关134的第三端子并耦合到示例第八开关310的第四端子。

72.在图3中,示例第四开关132的第一端子和第二端子耦合到第二电容器216,使得第四开关132并联耦合到第二电容器216。示例第四开关132的第三端子经由锁存器125和第三反相器135耦合到示例触发器302的输出端308。在其他示例中,示例第四开关132的第一端子和第二端子耦合到第一电阻器214和第二电容器216,使得第四开关132并联耦合到第一电阻器214和第二电容器216。在所示示例中,示例第五开关134的第一端子耦合到示例振荡器112,示例第五开关134的第二端子耦合到示例延迟单元110。示例第五开关134的第三端子经由锁存器125耦合到示例触发器302的输出端308。在图3中,第八开关310的第一端子耦合到参考电压发生器106并接收第一电压信号v

soft

,第八开关310的第二端子耦合到功率级104的输出电压节点v

o

并接收反馈电压信号v

fb

,第八开关310的第三端子耦合到差分差值放大器312的第一非反相输入端,第八开关310的第四端子耦合到触发器302的输出端。

‑

在图3中,功率级104是dc

‑

dc降压转换器。dc电源转换器通过将输入能量暂时存储在电子组件(例如电感器、电容器、电感元件、电容元件等)中并且然后在不同电压下在负载136处释放该能量来起作用。在功率级104中,反相器212是非门。示例反相器212确保当第六开关202闭合时第七开关204断开,并且当第七开关204闭合时第六开关202断开。在其他示例中,反相器212可以是确保第六开关202和第七开关204不会同时闭合的逻辑电路的组合。

73.在图3中,当第六开关202闭合而第七开关204断开时,电流从电源138(例如,输入电压信号v

in

)流向以线性速率充电的电感器206。当电感器206充电时,电感器206在由流过电感器206的电流i

sw

产生的磁场中储存能量。此外,当第六开关202闭合而第七开关204断开时,第一电容器208也充电到期望的输出电压电平,并且负载136被提供有来自电源138的电流。当第六开关202断开时,第七开关204闭合,使得电流i

sw

可以继续流向负载136。存储在电感器206的磁场中的能量消散,并且随着它消散,生成流过功率级104并流向负载136的电流(例如,i

sw

)。当第六开关202断开时,流经功率级104的电流i

sw

将与流经第七开关204的电流大小相等。来自电感器206的电流流向第一电容器208和负载136,而第一电容器208在功率

级104的输出电压节点v

o

处保持期望的输出电压并且负载136接收功率。电流i

sw

通过流经接地参考节点210和第七开关204返回电感器206。上述开关模式允许连续电流流入负载136。

74.在图3中,负载136是微控制器的子电路。在其他示例中,负载136可以是ev中的led阵列、马达、服务器、工业和/或住宅电器、数据通信服务器或任何合适的负载。

75.在图3中,示例电源138是未调节的线性电源。例如,电源138是二极管整流器的输出。在其他示例中,可以使用适合于该应用的其他电源。示例电源138生成输入电压信号v

in

。

76.在图3中,参考电压发生器106是一个或多个电压调节器、放大器、比较器和调节控制器102中的一个或多个电压电平的其他逻辑的组合。例如,参考电压发生器106生成第一电压电平的第一电压信号v

soft

。例如,第一电压信号v

soft

处于对应于功率级104的软启动的参考电压电平,使得功率级104斜升至期望和/或预定的电压电平(例如,对应于v

set

信号的电压电平的电压电平)。此外,示例参考电压发生器106生成微调电压信号v

ton

(例如,处于第二电压电平)以用作差分差值放大器312的参考电压电平。在本文的示例中,由参考电压发生器106生成的微调电压信号v

ton

是温度补偿的(例如,响应于外部温度和/或硅管芯温度的变化而改变和/或以其他方式改变)。例如,随着延迟单元110的温度从先前的温度升高和/或降低,由参考电压发生器106生成的微调电压信号v

ton

相应地改变以确保在所有温度正确操作。例如,由参考电压发生器106生成的微调电压信号v

ton

对应于每个延迟单元110的期望持续时间(例如,1.2纳秒)。此外,由示例参考电压发生器106生成的微调电压信号v

ton

在不同温度变化,以保持每个延迟单元110的期望持续时间。例如,当延迟单元110的温度升高时,由参考电压发生器106生成的微调电压信号v

ton

减小以保持延迟单元110的期望持续时间。在替代方案中,当示例延迟单元110的温度降低时,由参考电压发生器106生成的微调电压信号v

ton

增大以在延迟单元110上保持期望的持续时间。在附加或替代示例中,由参考电压发生器106生成的微调电压信号v

ton

增大以补偿延迟单元110的温度上升并且减小以补偿延迟单元110的温度下降。

77.在图3中,示例误差放大器108包括第一电阻器214、第二电容器216、差分差值放大器312和第二电阻器220。共同地,第一电阻器214、第二电容器216、差分差值放大器312和第二电阻器220基于来自示例功率级104和参考电压发生器106的一个或多个输入在输出端322处生成控制信号v

error

。误差放大器108经由分压器117监测功率级104的输出电压节点v

o

处的输出电压电平以作为反馈电压信号v

fb

。在示例中,第一电阻器214、第二电容器216和第二电阻器220是差分差值放大器反馈网络,其设置误差放大器108的增益,使得误差放大器108可以控制功率级104以在功率级104的输出电压节点v

o

处生成期望的输出电压电平(例如,对应于v

set

信号的电压电平)。在稳态操作期间,如果功率级104的输出电压节点v

o

处的输出电压信号偏离期望电平(例如,如果反馈电压信号v

fb

在瞬变期间增大和/或减小到高于正常操作电平),则差分差值放大器反馈网络(例如,第一电阻器214、第二电容器216和第二电阻器220)使差分差值放大器312在输出端322处生成控制信号v

error

以调节延迟单元110中包括的每个延迟单元的延迟的持续时间。例如,差分差值放大器312确定第一非反相输入端314处的电压电平与第一反相输入端316处的电压电平之间的差。在确定第一非反相输入端314处的电压电平与第一反相输入端316处的电压电平之间的差之后,差分差值放大器312将差分差值放大器反馈网络的增益(例如,在第二非反相输入端318、第二反相输入端320和输出端322之间耦合的反馈网络的增益)乘以第一非反相输入端314处的电压电平和第一反

相输入端316处的电压电平之间的差值。

78.在图3中,示例延迟单元110包括多个示例延迟单元以生成pwm信号。在本文的示例中,延迟单元110通过基于输入电压信号v

in

、振荡器112生成的信号和第一电压信号v

soft

(例如,更通常地,adc 114的输出)中的一个或多个向示例振荡器信号引入延迟来生成pwm信号。延迟单元110用于调节到功率级104的pwm信号的占空比以向示例负载136提供功率。例如,adc 114的输出确定被选择(例如,启用)的延迟单元110的数量。pwm信号的占空比对应于被启用的延迟单元110的数量乘以每个延迟单元110的持续时间。在图3中,延迟单元110中的每个延迟单元的持续时间是基于误差放大器108生成的控制信号确定的。例如,控制信号上的较高电压电平对应于每个延迟单元110的较长持续时间,而控制信号上的较低电压电平对应于每个延迟单元110的较短持续时间。

79.在图3中,振荡器112是锁相环振荡器。在其他示例中,振荡器112是电容器(rc)振荡器、环形振荡器、晶体振荡器或用于应用的任何其他合适的振荡器。示例振荡器112产生振荡信号。在图3中,振荡信号可以是为启动pwm信号的生成和/或以其他方式设置延迟单元110操作的频率而生成的周期性和/或非周期性信号。例如,当振荡器112输出振荡信号时,延迟单元110在振荡信号处于下降沿时在pwm信号上生成相应的上升沿。在这样的示例中,pwm信号在与激活的延迟单元110的数量相关联的延迟持续时间内保持在逻辑高值。激活的延迟单元110的数量由示例adc 114指示。

80.在图3中,示例adc 114是电流模数转换器。adc 114将模拟电流电平转换为数字输出(例如,二进制计数值)。例如,示例adc 114将模拟电流电平转换为八位二进制信号以指示待激活的延迟单元110的数量。在本文的其他示例中,adc 114可以是指示待激活的延迟单元110的数量的任何其他合适的解码器。

81.在图3中,示例前馈电压控制器116是模拟乘法器。示例前馈电压控制器116产生供adc 114使用的模拟电流信号。例如,前馈电压控制器116基于第一电压信号v

soft

、输入电压信号v

in

、由振荡器112生成的振荡器信号的频率中的一个或多个和对应于比例因子的一个或多个常数产生模拟电流信号。比例因子适合于控制器102的设计。例如,比例因子与每个延迟单元110的持续时间有关。示例前馈电压控制器116经由adc 114设置待激活的延迟单元110的数量。以此方式,示例前馈电压控制器116通过设置待激活的延迟单元110的数量经由adc 114来设置由延迟单元110生成的pwm信号的脉冲宽度的延迟(例如,持续时间)。以这种方式,延迟单元110通过向示例振荡器信号引入延迟来生成pwm信号,该延迟基于前馈电压控制器116的输出(例如,基于输入电压v

in

、由振荡器112生成的信号以及第一电压信号v

soft

)。

82.在图3中,示例分压器117是电阻分压器网络,其允许输出电压节点v

o

处的电压电平被差分差值放大器312和/或更一般地,被误差放大器108测量和/或以其他方式监测而没有损坏差分差值放大器312和/或更一般地说,误差放大器108的可能性。

83.在图3中,触发器302是施密特(schmitt)触发器,包括第一输入端304、第二输入端306和输出端308。在图3中,触发器302比较在第一输入端304处接收到的第一电压信号v

soft

和在第二输入端306处接收到的反馈电压信号v

fb

,并确定第一电压信号v

soft

的幅值是否在反馈电压信号v

fb

的阈值内。例如,阈值电压对应于基于应用的第一电压信号v

soft

的幅值与反馈电压信号v

fb

的幅值之间的可接受的差值。示例触发器302还基于第一电压信号v

soft

和

反馈电压信号v

fb

的比较经由在输出端308处生成的控制信号来配置第四开关132、第五开关134或第八开关310中的一个或多个。在图3中,示例触发器302在控制器102的操作开始时经由在输出端308处生成的控制信号来配置第四开关132、第五开关134或第八开关310中的一个或多个。

84.在图3中,锁存器125是在锁存器125的输出端处保持与在锁存器125的输入端处接收到的逻辑值相对应的逻辑值的器件。例如,锁存器125是sr锁存器。在其他示例中,锁存器125是d触发器、jk锁存器、门控sr锁存器、门控jk锁存器、门控d触发器、厄尔锁存器或任何其他合适的锁存器。

85.在图3中,第四开关132、第五开关134、第六开关202和第七开关204中的每一个都可以由晶体管来实现。例如,第四开关132、第五开关134和第六开关202中的每一个都是n沟道mosfet。在图3中,第七开关204是p沟道mosfet。在其他示例中,第四开关132和第五开关134、第六开关202和第七开关204是bjt、jfet、hbt、用于应用的任何合适晶体管和/或其任何组合。尽管可以使用bjt、jfet、hbt或任何合适的晶体管的许多组合来实现第四开关132或第五开关134中的一个或多个,但可能需要在特定控制器中以相同的开关类型来实现第四开关132和第五开关134中的每一个(例如,全部n型bjt,全部p型bjt、全部p沟道mosfet等)。在图3中,第八开关310是二对一多路复用器。在其他示例中,第八开关310是逻辑电路的组合。

86.在图2中,第三反相器135是将在第三反相器135的输入端处接收到的逻辑值取反并在第三反相器135的输出端处输出反转逻辑值的器件。示例第三反相器135是非逻辑门。在另外的示例中,第三反相器135可以是一个或多个逻辑门/逻辑电路的组合,其将接收到的信号的逻辑值取反并输出反转后的逻辑值。在模拟实施方式中,第三反相器135可以是反相放大器。

87.在图3中,在操作时,示例触发器302将误差放大器配置为电压跟随器,其中微调电压信号v

ton

作为经由第二电阻器220至第二非反相输入端318和第二反相输入端320的输入。例如,示例触发器302配置第四开关132、第五开关134和第八开关310以将误差放大器108配置为作为电压跟随器进行操作。更具体地,示例触发器302闭合第四开关132,断开第五开关134,并切换第八开关310,使得第八开关310的第二端子耦合到第八开关310的第三端子。通过配置第四开关132、第五开关134或第八开关310中的一个或多个,触发器302基于反馈电压信号v

fb

禁止误差放大器108控制延迟单元110中的每个延迟单元的持续时间。相反,通过配置第四开关132、第五开关134或第八开关310中的一个或多个,触发器302启用误差放大器108以基于微调电压信号v

ton

控制延迟单元110中的每个延迟单元的持续时间。此外,示例前馈电压控制器116基于第一电压信号v

soft

除以输入电压信号v

in

并乘以振荡器112的周期来设置延迟单元110的输出(例如,pwm信号导通时间)。此外,通过配置第四开关132、第五开关134或第八开关310中的一个或多个,示例触发器302通过将振荡器112与延迟单元110断开来禁用延迟单元110的pwm信号。

88.在图3中,在操作时,触发器302监测第一电压信号v

soft

以确定第一电压信号v

soft

是否已启动软启动功能。例如,触发器302监测第一电压信号v

soft

并且当触发器302检测到第一电压信号v

soft

上的电压正变化时,触发器302确定第一电压信号v

soft

已经启动软启动功能。当示例触发器302确定第一电压信号v

soft

已经启动软启动功能(例如,第一电压信号v

soft

开始上升)时,示例触发器302监测反馈电压信号v

fb

和第一电压信号v

soft

以确定第一电压信号v

soft

是否在反馈电压信号v

fb

的阈值差之内。

89.在图3中,在操作时,当示例触发器302确定第一电压信号v

soft

在反馈电压信号v

fb

的阈值差之内时,示例触发器302启用误差放大器108以基于反馈电压信号v

fb

和第一电压信号v

soft

来控制功率级104。例如,当示例触发器302确定第一电压信号v

soft

在反馈电压信号v

fb

的阈值差之内时,示例触发器302配置第四开关132、第五开关134或第八开关310中的一个或多个。更具体地,当示例触发器302确定第一电压信号v

soft

在反馈电压信号v

fb

的阈值差之内时,示例触发器302断开第四开关132、闭合第五开关134,并切换第八开关310,使得第八开关310的第一端子耦合到第八开关310的第三端子。通过配置第四开关132、第五开关134或第八开关310中的一个或多个,触发器302启用误差放大器108以基于反馈电压信号v

fb

和第一电压信号v

soft

控制延迟单元110中的每个延迟单元的持续时间。此外,通过配置(例如,断开和/或闭合)第四开关132、第五开关134、第八开关310中的一个或多个,示例触发器302启用延迟单元110的pwm信号。

90.图4是示出图1的示例前馈电压控制器116、图2的示例前馈电压控制器116和/或图3的示例前馈电压控制器116的进一步细节的示意图。在图4中,示例前馈电压控制器116包括示例第三电阻器402、示例第四电阻器404、示例第一压控电流源406、示例电压供应节点408、示例频率至电流转换器、示例第五电阻器412、示例第六电阻器414、示例第二压控电流源416、示例电流倍增器418、示例第七电阻器420、示例第三压控电流源422和示例接地参考节点210。

91.在图4中,第三电阻器402耦合到示例电源138、第四电阻器404和第一压控电流源406。示例第四电阻器404耦合到第三电阻器402、第一压控电流源406和接地参考节点210。示例第三电阻器402和示例第四电阻器404一起形成分压器以将电源138的电压电平(例如,输入电压信号vin)递降到对于第一压控电流源406而言安全的电压电平。

92.在图4中,第一压控电流源406耦合到第三电阻器402、第四电阻器404、电压供应节点408、接地参考节点210和电流倍增器418。示例第一压控电流源406是生成与由分压器(例如,第三电阻器402和第四电阻器404)设置的电压成比例并且对应于输入电压信号v

in

的电流i

vin

的器件。例如,第一压控电流源406可以由耦合到bjt晶体管的缓冲放大器来实现。例如,在这样的实施方式的操作中,由分压器(例如,第三电阻器402和第四电阻器404)设置的电压电平被输入到缓冲放大器,并且示例缓冲放大器将bjt的基极以促使在包括在第一压控电流源406中的电阻器两端上感应出由分压器设置的电压电平必需的电流来偏置。在这样的实施方式中,bjt的集电极经由电阻器耦合到电压供应节点408并且在电压供应节点408处生成的电压供应信号v

dd

向bjt的集电极供应电流。bjt的发射极提供电流,该电流在电阻器上感应出由分压器设置的电压电平。由bjt的发射极提供的电流i

vin

被传送到电流倍增器418。

93.在图4中,示例频率至电流转换器410耦合到示例振荡器112、示例电压供应节点408、示例接地参考节点210和示例电流倍增器418。示例频率至电流转换器410是转换生成与由振荡器112生成的振荡器信号的频率成比例的电流i

osc

的器件。例如,频率至电流转换器410可以被实现为电阻电感(rl)滤波器。在这样的实施方式中,到电流倍增器418的电流输出由rl滤波器的增益(例如,传递函数)控制。示例rl滤波器的增益与输入信号(例如,由

振荡器112生成的振荡器信号)的频率有关。因此,从频率至电流转换器410输出到电流倍增器418的电流i

osc

基于频率至电流转换器410的增益与由振荡器112生成的振荡器信号的频率相关。

94.在图4中,第五电阻器412耦合到示例参考电压发生器106、第六电阻器414和第二压控电流源416。示例第五电阻器412耦合到第六电阻器414、第二压控电流源416和接地参考节点210。示例第五电阻器412和示例第六电阻器414一起形成分压器以将参考电压发生器106的电压电平(例如,第一电压信号v

soft

)逐降到对于第二压控电流源416而言安全的电压电平。

95.在图4中,第二压控电流源416耦合到第五电阻器412、第六电阻器414、电压供应节点408、接地参考节点210和电流倍增器418。示例第二压控电流源416是生成与由分压器(例如,第五电阻器412和第六电阻器414)设置的电压成比例并且对应于第一电压信号v

soft

的电流i

vsoft

的器件。例如,第二压控电流源416可以由耦合到bjt晶体管的缓冲放大器来实现。例如,在这样的实施方式的操作中,由分压器(例如,第五电阻器412和第六电阻器414)设置的电压电平被输入到缓冲放大器,并且示例缓冲放大器将bjt的基极以促使在包括在第二压控电流源416中的电阻器两端上感应出由分压器设置的电压电平必需的电流来偏置。在这样的实施方式中,bjt的集电极经由电阻器耦合到电压供应节点408并且在电压供应节点408处生成的电压供应信号v

dd

向bjt的集电极供应电流。bjt的发射极提供电流,该电流在电阻器上感应出由分压器设置的电压电平。由bjt的发射极提供的电流i

vsoft

被传送到电流倍增器418。

96.在图4中,示例电流倍增器418耦合到第一压控电流源406、频率至电流转换器410、第二压控电流源416、接地参考节点210并经由第七电阻器420耦合到第三压控电流源422。示例电流倍增器418是将第一压控电流源406提供的电流i

vin

与频率至电流转换器410提供的电流i

osc

和第二压控电流源416提供的电流i

vsoft

相乘的器件。例如,电流倍增器418可由一个或多个级联电流镜实现。示例电流倍增器418将第一压控电流源406提供的电流i

vin

、由频率至电流转换器410提供的电流i

osc

和第二压控电流源416提供的电流i

vsoft

相乘以根据下面的公式1生成输出电流i

out

:

97.公式

‑1[0098][0099]

在图4中,公式1包括电流i

vsoft

、电流i

osc

、电流i

vin

和比例因子k。在图4中,比例因子与每个延迟单元110的持续时间有关。所得输出电流i

out

经由第七电阻器420提供给第三压控电流源422。

[0100]

在图4中,第二压控电流源416经由第七电阻器420耦合到电流倍增器418、耦合到电压供应节点408、耦合到接地参考节点210并耦合到adc 114。示例第三压控电流源422是生成与由电流i

out

引起的第七电阻器420两端的电压降设置的电压成比例的电流i

on

的器件。例如,第三压控电流源422可以由耦合到bjt晶体管的缓冲放大器来实现。例如,在这种实施方式的操作中,由第七电阻器420两端的电压降设置的电压电平被输入到缓冲放大器,并且示例缓冲放大器用引起在包括在第三压控电流源422中的电阻器两端感应出第七电阻器420两端的电压降设置的电压电平所需的电流偏置bjt的基极。在这样的实施方式中,bjt的

集电极经由电阻器耦合到电压供应节点408并且在电压供应节点408处生成的电压供应信号v

dd

向bjt的集电极供应电流。bjt的发射极提供电流,该电流在电阻器上感应出由分压器设置的电压电平。由bjt的发射极提供的电流i

on

被传送到adc 114。

[0101]

图5是示出图1的示例参考电压发生器106、图2的示例参考电压发生器106和/或图3的示例参考电压发生器106的进一步细节的示意图。示例参考电压发生器106包括示例带隙电压源502、示例第一电压放大器504、示例第二电压放大器506、示例数模转换器508、包括输入端512、输入端514和输出端516的示例比较器510、示例振荡器518和示例电压供应节点408。

[0102]

在图5中,带隙电压源502耦合到电压供应节点408、第一电压放大器504和第二电压放大器506。在图5中,带隙电压源502是生成具有电压电平(例如,1.25伏)的信号而与工作温度和电压供应变化无关的电路。此外,示例带隙电压源502被配置为生成与参考电压发生器106的温度成反比的电流i

inverse

。以这种方式,随着参考电压发生器106的温度升高,电流i

inverse

减小并且随着参考电压发生器106的温度降低,电流i

inverse

增大。例如,带隙电压源502可以由brokaw带隙电路实现。在其他示例中,带隙电压源502可以是生成带隙参考电压和电流i

inverse

的任何电路。

[0103]

在图5中,示例第一电压放大器504耦合到带隙电压源502、第二开关128的第一端子、第二电阻器220和差分差值放大器312的第二非反相输入端318。示例第一电压放大器504是被配置为基于电流i

inverse

生成微调电压信号v

ton

的器件。例如,第一电压放大器504可以由跨阻放大器来实现。在其他示例中,示例第一电压放大器504可以由任何合适的放大器来实现。在示例中,第二电压放大器506耦合到带隙电压源502和数模转换器508。示例第二电压放大器506是被配置为生成具有任意电压电平的信号的器件,该任意电压电平被设置为大于可以经由电压输入端140作为v

set

信号输入的任何电压电平。例如,第二电压放大器506可以由非反相放大器来实现。在其他示例中,示例第二电压放大器506可以由任何合适的放大器来实现。

[0104]

在图5中,数模转换器508耦合到第二电压放大器506、比较器510的第二输入端514、振荡器518、前馈电压控制器116、比较器118的第二输入端122、比较器118的第二输入端122、第三开关130的第一端子和触发器302的第一输入端304。示例数模转换器508是以指定频率对输入电压进行采样的器件。例如,数模转换器508可以由十二位数模转换器来实现。在其他示例中,可以使用任何合适的数模转换器。

[0105]

在图5中,示例比较器510在第一输入端512处耦合到电压输入端140,在第二输入端514处耦合到数模转换器508,并且在输出端516处耦合到振荡器518。示例比较器510是包括第一输入端512、第二输入端514和输出端516的模拟比较器。在图5中,比较器510比较由数模转换器508生成的电压信号和从电压输入端接收到的电压(例如,v

set

信号),并确定从数模转换器508接收到的电压信号的幅值是否在v

set

电压信号的幅值的阈值内。例如,阈值电压对应于由数模转换器508生成的电压信号的幅值与基于应用的v

set

信号的幅值之间的可接受差。当比较器510确定由数模转换器508生成的电压信号在v

set

信号的阈值电压内时,比较器510在输出端516处生成控制信号。

[0106]

在图5中,示例振荡器518在输出端516处耦合到示例数模转换器508和示例比较器510。示例振荡器1518可以由锁相环振荡器实现。在其他示例中,振荡器518是电容器(rc)振

荡器、环形振荡器、晶体振荡器或用于应用的任何其他合适的振荡器。示例振荡器518产生振荡信号。在图5中,振荡信号可以是为启动数模转换器508的采样而生成的周期性和/或非周期性信号。此外,示例振荡器518包括要启用和禁用的功能。

[0107]

在图5中,示例数模转换器508以振荡器518的频率(例如,在由振荡器518生成的信号的上升沿)采样由第二电压放大器506生成的电压信号的电压电平。因为数模转换器508对第二电压放大器506生成的电压信号进行采样,所以信号的电压电平由数模转换器508生成。因此,当数模转换器508对由第二电压放大器506生成的信号进行采样时,第二输入端514处的电压电平以振荡器518的频率缓慢递升到由第二电压放大器506生成的信号的电压电平。当比较器510确定第一输入端512处的电压电平(例如,v

set

信号的电压电平)在第二输入端514处的电压电平(例如,第一电压信号v

soft

)的阈值电压内时,比较器510在输出端516处生成控制信号以禁用振荡器518。在一些示例中,当比较器510在输出端516处生成控制信号时,比较器510额外地将控制信号传送到开关,该开关将第一电压信号v

soft

上的电压电平从数模转换器508的输出端处的电压电平切换到v

set

信号的电压电平。

[0108]

图6是图示图1的示例电源转换器系统100、图2的示例电源转换器系统200和/或图3的示例电源转换器系统300的操作的时序图600。时序图600包括示例第一曲线图602、示例第二曲线图604、示例第三曲线图606、示例第四曲线图608、示例第一时间610(t1)和示例第二时间612(t2)。示例第一曲线图602包括示例锁存器输出曲线614。示例第二曲线图604包括示例误差放大器输出曲线616,并且示例第三曲线图606包括示例反馈电压曲线618和示例软启动曲线620。示例第四曲线图608包括示例第一非反相输入曲线622、示例第一反相输入曲线624、示例第二非反相输入曲线626和示例第二反相输入曲线628。

[0109]

在图6中,第一曲线图602图示了由示例比较器118的输出124和/或示例触发器302的输出308控制的示例锁存器125的输出与时间的关系。在该示例中,锁存器输出曲线614表示由锁存器125生成的模拟电压,该模拟电压由比较器118的输出124和/或触发器302的输出308控制。示例第二曲线图604图示了误差放大器108的输出与时间的关系。示例误差放大器输出曲线616图示了由运算放大器218的输出226和/或图3的示例差分差值放大器312的输出322支配的误差放大器108的输出端处的电压电平。示例第三曲线图606表示控制器102中的各种电压与时间的关系。示例反馈电压曲线618表示由误差放大器108经由分压器117在功率级104的输出电压节点v

o

处监测到的反馈电压信号v

fb

。示例软启动曲线620表示由参考电压发生器106生成的第一电压信号v

soft

。示例第一非反相输入曲线622表示差分差值放大器312的第一非反相输入端314处的电压电平。示例第一反相输入曲线624表示差分差值放大器312的第一反相输入端316处的电压电平。示例第二非反相输入曲线626表示差分差值放大器312的第二非反相输入端318处的电压电平。示例第二反相输入曲线628表示差分差值放大器312的第二反相输入端320处的电压电平。

[0110]

在图6中,第一时间610表示电源转换器系统100、电源转换器系统200或电源转换器系统300中的一个或多个的启动。例如,第一时间610可以表示电源被连接到控制器102。在其他示例中,第一时间610表示控制器102接收到启用信号。在第一时间610处,锁存器输出曲线614的值为0伏,误差放大器输出曲线616的值为1.03伏,反馈电压曲线618的值为40毫伏(mv),并且软启动曲线620的值为零mv。此外,在第一时间610处,第一非反相输入曲线622的值为40mv,第一反相输入曲线624的值为40mv,第二非反相输入曲线626的值为20mv,

并且第二反相输入曲线628的值为零mv。在图1中,在第一时间610处,比较器118断开第一开关126,闭合第二开关128,断开第三开关130,闭合第四开关132,并断开第五开关134。在图2中,在第一时间610处,比较器118断开第一开关126,闭合第二开关128,断开第三开关130,闭合第四开关132,并断开第五开关134。在图3中,在第一时间610处,触发器302闭合第四开关132,断开第五开关134,并配置第八开关310,使得第八开关310的第二端子耦合到第八开关310的第三端子。在第一时间610处,比较器118和/或触发器302闭合和/或断开第一开关126、第二开关128、第三开关130、第四开关132、第五开关134或第八开关134中的一个或多个,以配置误差放大器108来基于微调电压信号v

ton

控制延迟单元110中的每个延迟单元的持续时间。在替代示例中,比较器118闭合和/或断开第一开关126、第二开关128、第三开关130、第四开关132或第五开关134中的一个或多个,以配置误差放大器108来基于微调电压信号v

ton

控制延迟单元110中的每个延迟单元的持续时间。此外,在示例第一时间610处,示例前馈电压控制器116基于第一电压信号v

soft

除以输入电压信号v

in

并乘以振荡器112的周期来设置延迟单元110的输出(例如,pwm信号)。此外,通过配置第一开关126、第二开关128、第三开关130、第四开关132、第五开关134或第八开关310中的一个或多个,示例比较器118和/或触发器302禁用延迟单元110中的pwm信号。

[0111]

在图6中,在第一时间610和第二时间612之间,参考电压发生器106开始将第一电压信号v

soft

从零斜升至对应于功率级104的输出电压节点v

o

上的期望电压(例如,v

set

信号)的电压。在第一时间610和第二时间612之间,锁存器输出曲线614保持在零伏,误差放大器输出曲线616保持在1.03伏,反馈电压曲线618保持在40mv,以及软启动曲线620开始上升到对应于功率级104的输出电压节点v

o

处的期望电压的值。而且,在第一时间610和第二时间612之间,第一非反相输入曲线622保持在40mv的值,第一反相输入曲线624保持在40mv的值,第二非反相输入曲线626保持在20mv的值,并且第二反相输入曲线628开始上升到差分差值放大器312的第二非反相输入端318处的电压电平。

[0112]

在图6中,第二时间612表示反馈电压信号v

fb

等于第一电压信号v

soft

的时间。在第二时间612处,锁存器输出曲线614从0伏转变为4.6伏,误差放大器输出曲线616从1.03伏的恒定电压转变为取决于误差放大器108的误差放大器反馈网络的增益的电压,反馈电压曲线618处于40mv的值,并且软启动曲线620处于大于或等于40mv的值。此外,在第二时间612处,第一非反相输入曲线622的值为40mv,第一反相输入曲线624的值为40mv,第二非反相输入曲线626的值为20mv,并且第二反相输入曲线628的值为20mv。在图1中,在第二时间612处,示例比较器118闭合第一开关126,断开第二开关128,闭合第三开关130,断开第四开关132,并闭合第五开关134。在图2中,在第二时间612处,示例比较器118闭合第一开关126,断开第二开关128,闭合第三开关130,断开第四开关132,并闭合第五开关134。在图3中,在第二时间612处,示例触发器302断开第四开关132,闭合第五开关134,并切换第八开关310,使得第八开关310的第一端子耦合到第八开关310的第三端子。在第二时间612处,比较器118和/或触发器302闭合和/或断开第一开关126、第二开关128、第三开关130、第四开关132、第五开关134或第八开关310中的一个或多个,以启用误差放大器108来基于反馈电压信号v

fb

和第一电压信号v

soft

控制延迟单元110中的每个延迟单元的持续时间。在替代示例中,比较器118闭合和/或断开第一开关126、第二开关128、第三开关130、第四开关132或第五开关134中的一个或多个,以配置误差放大器108来基于反馈电压信号v

fb

和第一电压信号v

soft

控

制延迟单元110中的每个延迟单元的持续时间。此外,通过配置第一开关126、第二开关128、第三开关130、第四开关132和第五开关134中的一个或多个,示例比较器118和/或示例触发器302启用延迟单元110的pwm信号。

[0113]

在图6中,在第二时间612之后,示例锁存器输出曲线614保持在4.6伏,示例误差放大器输出曲线616继续取决于误差放大器108的误差放大器反馈网络的增益,示例反馈电压曲线618关于第一电压信号v

soft

的电压电平略微变化,并且示例软启动曲线620继续斜升至对应于功率级104的输出电压节点v

o

处的期望电压(例如,v

set

信号)的值。此外,在第二时间612之后,第一非反相输入曲线622在第一电压信号v

soft

的电压电平附近略微变化,第一反相输入曲线624继续斜升至对应于在功率级104的输出电压节点v

o

处的期望电压电平(例如,v

set

信号)的值,第二非反相输入曲线626保持在20mv的值,并且第二反相输入曲线628在微调电压信号v

ton

的电压电平附近略微变化。在图6中,第一非反相输入曲线622的电压电平与第一反相输入曲线624的电压电平之间的差异实质上类似于第二非反相输入曲线626的电压电平与第二反相输入曲线628的电压电平之间的差异。

[0114]

图7是图示图1的示例电源转换器系统100、图2的示例电源转换器系统200和/或图3的示例电源转换器系统300的附加操作的时序图700。时序图700包括示例第五曲线图702、示例第六曲线图704、示例第一时间610(t1)和示例第二时间612(t2)。示例第五曲线图702包括示例输出电压曲线706。示例第六曲线图704包括示例转换器电流曲线708。

[0115]

在图7中,第五曲线图702图示了功率级104的输出电压节点v

o

处的差分电压电平与时间的关系。在示例中,输出电压曲线706表示功率级104的输出电压节点v

o

处的差分电压电平。示例第六曲线图704图示了通过电感器206的电流i

sw

与时间的关系。示例转换器电流曲线708图示了通过图2和3的电感器206的电流i

sw

。在其他示例中,示例转换器电流曲线708表示通过图1的功率级104的电流。

[0116]

在图7中,第一时间610表示电源转换器系统100、电源转换器系统200或电源转换器系统300中的一个或多个的启动。例如,第一时间610可以表示电源被连接到控制器102。在其他示例中,第一时间610表示控制器102接收到启用信号。在第一时间610处,输出电压曲线706处于200mv的值并且转换器电流曲线708处于零安培的值。在图1中,在第一时间610处,比较器118断开第一开关126,闭合第二开关128,断开第三开关130,闭合第四开关132,并断开第五开关134。在图2中,在第一时间610处,比较器118断开第一开关126,闭合第二开关128,断开第三开关130,闭合第四开关132,并断开第五开关134。在图3中,在第一时间610处,比较器118闭合第四开关132,断开第五开关134,并配置第八开关310,使得第八开关310的第二端子耦合到第八开关310的第三端子。在第一时间610处,比较器118和/或触发器302闭合和/或断开第一开关126、第二开关128、第三开关130、第四开关132、第五开关134或第八开关134中的一个或多个,以配置误差放大器108来响应于微调电压信号v

ton

控制延迟单元110中的每个延迟单元的持续时间。此外,在示例第一时间610处,示例前馈电压控制器116设置延迟单元110的输出(例如,pwm信号)以跟踪除以输入电压信号v

in

并乘以振荡器112的周期的第一电压信号v

soft

。此外,通过配置第一开关126、第二开关128、第三开关130、第四开关132、第五开关134或第八开关310中的一个或多个,示例比较器118和/或示例触发器302禁用延迟单元110中的pwm信号。

[0117]

在图7中,在第一时间610和第二时间612之间,参考电压发生器106开始将第一电

压信号v

soft

从零斜升至对应于功率级104的输出电压节点v

o

上的期望电压的电压。在第一时间610和第二时间612之间,输出电压曲线706保持在200mv并且转换器电流曲线708保持在零安培的值。

[0118]

在图7中,第二时间612表示反馈电压信号v

fb

等于第一电压信号v

soft

的时间。在第二时间612处,输出电压曲线706随着功率级104的输出电压节点v

o

处的输出电压电平开始上升,并且转换器电流曲线708随着电感器206的磁场充电和放电开始上升然后下降。在图1中,在第二时间612处,示例比较器118闭合第一开关126,断开第二开关128,闭合第三开关130,断开第四开关132,并闭合第五开关134。在图2中,在第二时间612处,示例比较器118闭合第一开关126,断开第二开关128,闭合第三开关130,断开第四开关132,并闭合第五开关134。在图3中,在第二时间612处,示例触发器302断开第四开关132,闭合第五开关134,并切换第八开关310,使得第八开关310的第一端子耦合到第八开关310的第三端子。在第二时间612处,比较器118和/或触发器302闭合和/或断开第一开关126、第二开关128、第三开关130、第四开关132、第五开关134或第八开关310中的一个或多个,以启用误差放大器108来基于反馈电压信号v

fb

和第一电压信号v

soft

控制延迟单元110中的每个延迟单元的持续时间。此外,通过配置第一开关126、第二开关128、第三开关130、第四开关132和第五开关134中的一个或多个,示例比较器118和/或示例触发器302启用延迟单元110的pwm信号。

[0119]

在图7中,在第二时间612之后,示例输出电压曲线706继续上升并且示例转换器电流曲线708继续上升然后下降,同时趋向于更高的电流值。

[0120]

图8是图示图1的示例参考电压发生器106、图2的示例参考电压发生器106和/或图3的示例参考电压发生器106的操作的时序图800。示例时序图800包括示例第七曲线图802、示例第八曲线图804、示例第九曲线图806、示例第十曲线图808、示例第十一曲线图810、示例第三时间812(t3)和示例第四时间814(t4)。

[0121]

在图8中,第七曲线图802包括示例电源电压曲线816,第八曲线图804包括示例设定电压曲线818,第九曲线图806包括示例软启动曲线820,第十曲线图808包括示例振荡器曲线822,并且第十一曲线图810包括示例比较器输出曲线824。

[0122]

在图8中,第七曲线图802图示了在电压供应节点408处生成的电压供应信号v

dd

的电压电平。示例电源电压曲线816表示电压供应信号v

dd

的电压电平。示例第八曲线图804图示了电压输入端140处的电压电平与时间的关系。示例设定电压曲线818图示了v

set

信号的电压电平。示例第九曲线图806图示了数模转换器508的电压电平与时间的关系。示例软启动曲线820图示了由数模转换器508生成的第一电压信号v

soft

。示例第十曲线图808图示了振荡器518的频率与时间的关系。示例振荡器曲线822图示了由振荡器518生成的振荡器信号。示例第十一曲线图810图示了比较器510的输出516的逻辑值与时间的关系。示例比较器输出曲线824图示了在输出端516处生成的逻辑值。

[0123]

在图8中,第三时间812表示电源转换器系统100、电源转换器系统200或电源转换器系统300中的一个或多个的启动。例如,第三时间812可以表示电源被连接到控制器102(例如,电源电压信号v

dd

的电压电平上升)。在第三时间812处,电源电压曲线816的值为3.3v,设定电压曲线818的值为1.5v,软启动曲线820的值为0伏,振荡器曲线822处于逻辑低值,并且比较器输出曲线824处于逻辑低值。

[0124]

在图8中,在第三时间812和第四时间814之间,第一电压信号v

soft

上升到v

set

信号

上的电压电平。在第三时间812和第四时间814之间,电源电压曲线816保持在3.3v的值,设定电压曲线818保持在1.5v的值,软启动曲线820开始从零伏递增上升到1.5v(例如,在振荡器曲线822的上升沿处),振荡器曲线822开始以振荡器518的频率振荡,并且比较器输出曲线824保持在逻辑低值。

[0125]

在图8中,第四时间814表示电源转换器系统100、电源转换器系统200或电源转换器系统300中的一个或多个的软启动电压电平满足预设或期望的电压电平(例如,v

set

信号)的时间。在第四时间814处,电源电压曲线816的值为3.3v,设定电压曲线818的值为1.5v,软启动曲线820的值为1.5v,振荡器曲线822处于逻辑高值(例如,上升沿),并且比较器输出曲线824从逻辑低值转变为逻辑高值。在图5中,在第四时间814处,由数模转换器508生成的电压电平与电压输入端140处的电压电平基本上相似。在第四时间814处,示例比较器510在输出端516处生成逻辑高值以禁用振荡器518。

[0126]

在图8中,在第四时间814之后,电源电压曲线816保持在3.3v的值,设定电压曲线818保持在1.5v的值,软启动曲线820保持在1.5v的值,振荡器曲线822从逻辑高值转变为逻辑低值并保持在逻辑低值,并且比较器输出曲线824保持在逻辑高值。

[0127]

虽然在图2和图3中图示了实现图1的控制器102的示例方式,但是图2和图3中图示的元件、过程和/或器件中的一个或多个可以被组合、划分、重新布置、省略、以任何其他方式消除和/或实施。此外,示例参考电压发生器106、示例误差放大器108、示例延迟单元110、示例振荡器112、示例adc 114、示例前馈电压控制器116、示例比较器118和/或更一般地,图1、2和3的示例控制器102可以由硬件、软件、固件和/或硬件、软件和/或固件的任何组合来实现。因此,例如,示例参考电压发生器106、示例误差放大器108、示例延迟单元110、示例振荡器112、示例adc 114、示例前馈电压控制器116、示例比较器118和/或更一般地,示例控制器102可以由一个或多个模拟或数字电路、逻辑电路、一个或多个可编程处理器、一个或多个可编程控制器、一个或多个图形处理单元(一个或多个gpu)、一个或多个数字信号处理器(dsp)、一个或多个专用集成电路(asic)、一个或多个可编程逻辑器件(pld)和/或一个或多个现场可编程逻辑器件)(fpld)实现。当阅读本专利的任何设备或系统权利要求以涵盖纯软件和/或固件实施方式时,示例参考电压发生器106、示例误差放大器108、示例延迟单元110、示例振荡器112、示例adc 114、示例前馈电压控制器116、示例比较器118和/或示例控制器102中的至少一个在此明确定义为包括非暂时性计算机可读存储装置或存储盘,诸如存储器等,包括软件和/或固件。更进一步,图1、2和3的示例控制器102可以包括除图9中所示的那些之外的一个或多个元件、过程和/或器件,或代替图9中所示的一个或多个元件、过程和/或器件,和/或可以包括所示的元件、过程和器件中的不止一个元件、过程和/或器件或所有所示的元件、过程和器件。如本文所用,短语在通信中包括其变体,涵盖直接通信和/或通过一个或多个中间部件的间接通信,并且不需要直接的物理(例如,有线)通信和/或恒定的通信,而是另外包括以周期性间隔、计划间隔、非周期性间隔和/或一次性事件的选择性通信。

[0128]

图9示出了代表用于实现图1、2和3的控制器102的示例硬件逻辑、机器可读指令、硬件实现的状态机和/或其任何组合的流程图。机器可读指令可以是由诸如控制器102的计算机处理器执行的一个或多个可执行程序或可执行程序的一部分。程序可以实施在存储在诸如非易失性存储器(例如,只读存储器(rom)、电可擦除可编程只读存储器(eeprom)、闪存

等)、易失性存储器(例如,同步动态随机存取存储器(sdram)、动态随机存取存储器(dram)等,和/或任何其他类型的随机存取存储器(ram)器件)等或与控制器102相关联的存储器的非暂时性计算机可读存储介质上的软件中,但是整个程序和/或其部分可以替代地由除控制器102之外的器件执行和/或实施在固件或专用硬件中。此外,尽管参考图9中所示的流程图描述了示例程序,但是可以替代地使用实现示例控制器102的许多其他方法。例如,可以改变框的执行顺序,和/或可以改变、消除或组合所描述的一些框。附加地或替代地,任何或所有框可以由被构造成在不执行软件或固件的情况下执行相应的操作的一个或多个硬件电路(例如,分立和/或集成模拟和/或数字电路、fpga、asic、比较器、运算放大器(op

‑

amp)、逻辑电路等)实现。

[0129]

本文描述的机器可读指令可以以压缩格式、加密格式、分段格式、打包格式等中的一种或多种存储。本文描述的机器可读指令可以存储为可用于创建、制造和/或产生机器可执行指令的数据(例如,指令的一部分,代码,代码的表示等)。例如,机器可读指令可以被分段并且存储在一个或多个存储装置和/或计算装置(例如,服务器)上。机器可读指令可能需要安装、修改、改编、更新、组合、补充、配置、解密、解压缩、解包、分发、重分配等中的一项或多项,以便使其可由计算装置和/或其他机器直接可读和/或执行。例如,机器可读指令可以存储在多个部分中,这些部分被分别压缩、加密并存储在单独的计算装置上,其中,这些部分在解密、解压缩和组合后形成一组可执行指令,这些可执行指令实现了诸如本文所述的程序。在另一个示例中,在机器可读指令和/或相应的一个或多个程序可以全部或部分执行之前,可能需要配置机器可读指令(例如,存储的设置,数据输入,记录的网络地址等)。因此,所描述的机器可读指令和/或相应的一个或多个程序包括这样的机器可读指令和/或一个或多个程序,而不管机器可读指令和/或一个或多个程序在存储时或以其他方式搁置或在途中时的特定格式或状态。

[0130]

如上所述,图9的示例过程可以使用存储在非暂时性计算机和/或机器可读介质(诸如硬盘驱动器、闪存、只读存储器、光盘、数字通用磁盘、高速缓存、随机存取存储器和/或在任何持续时间(例如,延长的时间段、永久地、用于短暂实例、用于暂时缓存和/或高速缓存信息)内存储信息的任何其他存储装置或存储盘)上的可执行指令(例如,计算机和/或机器可读指令)来实现。如本文所用,术语“非暂时性计算机可读介质”包括任何类型的计算机可读存储装置和/或存储盘,并且排除传播信号并排除传输介质。

[0131]

包括和包含(及其所有形式和时态)是开放式术语。因此,每当权利要求采用任何形式的“包括”或“包含”(例如,包括、包含,具有等)作为前序部分或在任何种类的权利要求陈述中时,在不超出相应权利要求或陈述的范围的情况下,可以存在其他要素、术语等。该短语至少以与术语包含和包括是开放式相同的方式也是开放式的。术语和/或当例如以诸如a、b和/或c的形式使用时是指a、b、c的任何组合或子集,诸如(1)单独的a,(2)单独的b,(3)单独的c,(4)a与b,(5)a与c,(6)b与c,以及(7)a与b和c。短语a和b中的至少一个是指包括(1)至少一个a、(2)至少一个b和(3)至少一个a和至少一个b的实施方式。

[0132]

图9是代表可以被执行以实现图1、2和3的示例控制器102的示例机器可读指令的流程图。示例机器可读指令900开始于框902处,其中比较器118配置误差放大器108以基于微调的电压信号v

ton

来控制延迟单元110中的延迟单元的延迟的持续时间。更具体地,在框902处,比较器118启用和/或禁用第一开关126、第二开关128、第三开关130和第四开关132

中的一个或多个。例如,在电源转换器系统100中,比较器118禁用第一开关126,启用第二开关128,禁用第三开关130,并启用第四开关132。此外,例如,在电源转换器系统200中,比较器118禁用第一开关126,启用第二开关128,禁用第三开关130,并启用第四开关132。可替代地,在示例电源转换器系统300中,示例比较器118启用第四开关132并配置第八开关310,使得第八开关310的第二端子耦合到第八开关310的第三端子。

[0133]

在图9中,在框904处,比较器118禁用延迟单元110。更具体地,比较器118禁用第五开关134。在框906处,前馈电压控制器116设置延迟单元110,使得pwm信号跟踪第一电压信号v

soft

和振荡器112的周期除以输入电压信号v

in

的乘积。在框908处,比较器118监测第一电压信号v

soft

。在框910处,比较器118确定第一电压信号v

soft

是否已经从零伏开始上升。如果比较器118确定第一电压信号v

soft

已经开始上升(框910:是),则机器可读指令900进行到框912。如果比较器118确定第一电压信号v

soft

尚未开始上升(框910:否),则机器可读指令900进行到框908。

[0134]

在图9中,在框912处,比较器118监测反馈电压信号v

fb

和第一电压信号v

soft

。在框914处,比较器118确定第一电压信号v

soft

是否在反馈电压信号v

fb

的阈值差之内。如果比较器118确定第一电压信号v

soft

在反馈电压信号v

fb

的阈值差之内(框914:是),则机器可读指令900进行到框916。如果比较器118确定第一电压信号v

soft

不在反馈电压信号v

fb

的阈值差之内(框914:否),则机器可读指令900进行到框912。

[0135]

在框916处,响应于第一电压信号v

fb

在反馈电压信号v

fb

的阈值差内,比较器118配置误差放大器108以响应于反馈电压信号v

fb

控制延迟单元110中的每个延迟单元的持续时间。更具体地,比较器118启用和/或禁用第一开关126、第二开关128、第三开关130、第四开关132或第八开关310中的一个或多个。例如,在电源转换器系统100中,比较器118启用第一开关126,禁用第二开关128,启用第三开关130,并且禁用第四开关132。此外,例如,在电源转换器系统200中,比较器118启用第一开关126,禁用第二开关128,启用第三开关130,并且禁用第四开关132。可替代地,在示例电源转换器系统300中,示例比较器118禁用第四开关132并配置第八开关310,使得第八开关310的第一端子耦合到第八开关310的第三端子。在图9中,在框918处,比较器118启用延迟单元110。更具体地,比较器118启用第五开关134。

[0136]

从上文可以理解,已经描述了示例方法、设备和制品,其通过将电源转换器从关断状态平滑地转变到被控制以在电源转换器输出端处输出等于或大于预偏置电压电平的电压电平来防止电源转换器的输出上的瞬变。此外,一些示例通过禁用电源转换器直到对应于电源转换器的软启动电压等于或大于对应于预偏置电压的电压电平来防止负电流和dcm操作。所描述的方法、设备和制品通过防止电源转换器的负电流流动和dcm操作而通过降低器件的功耗来提高使用计算装置的效率。所描述的方法、设备和制品通过减少瞬变来改善电源转换器的输出信号,从而改善耦合到电源转换器的一个或多个电路和/或器件的功能。所描述的方法、设备和制品相应地针对计算机的功能进行一项或多项改进。

[0137]

尽管本文已经描述了某些示例方法、设备和制品,但是本专利的覆盖范围不限于此。相反,本专利涵盖了完全落入本专利权利要求范围内的所有方法、设备和制品。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1