恒定导通时间降压转换器的制作方法

1.本发明涉及恒定导通时间(constant on-time,cot)降压转换器,特别涉及可改善暂态响应的cot降压转换器。

背景技术:

2.传统降压转换器的运作可描述如下。传统的降压转换器包含作为开关的一对功率晶体管,该对功率晶体管可被导通或截止以将输出电压调节至等于参考电压。具体而言,功率晶体管交替地导通及截止以在开关输出节点sw(也称为开关节点)产生开关电压v

sw

。开关节点耦接于包含电感及电容的lc滤波器电路,用以产生具有实质上恒定大小的输出电压。接着可使用输出电压来驱动负载。

3.图1为现有技术的传统降压转换器1的示意图。降压转换器1包含一对功率晶体管t1及t2,用以接收输入电压v

in

及交替地导通及截止以在开关节点sw产生开关电压v

sw

。开关电压v

sw

直接耦接于包含电感l1及电容c

out

的lc滤波电路,以在节点out产生具有实质上恒定大小的稳定输出电压v

out

。接着可使用输出电压v

out

驱动负载30,由降压转换器1提供负载电流i

load

以使输出电压v

out

保持在恒定水平。

4.降压转换器1包含反馈控制电路用以调节到lc滤波器电路的能量传递,以在电路的期望负载极限之内将输出电压v

out

维持恒定。具体而言,反馈控制电路使功率晶体管t1及t2导通或关闭以将输出电压v

out

调节为等于参考电压v

ref

,或调节为等于相关于参考电压v

ref

的电压值。在降压转换器1中,使用包含电阻r1及r2的分压器对输出电压v

out

进行分压,然后将分压作为反馈节点fb上的反馈电压v

fb

反馈至降压转换器1。误差处理电路(例如比较器12)将反馈电压v

fb

与参考电压v

ref

进行比较。比较器12的输出端耦接于驱动电路14,以基于开关调节器控制机制产生功率晶体管的控制电压。控制电压用以产生功率晶体管t1及t2的栅极驱动信号。

5.恒定导通时间(constant on-time,cot)降压转换器是一种采用纹波模式控制的降压转换器,cot降压转换器基于输出信号中的纹波成分来调节输出电压。由于功率晶体管的开关动作,所有开关模式调节器都会通过输出电感产生输出纹波电流。由于输出电容c

out

中的等效串联电阻(equivalent series resistance,esr)及等效串联电感(equivalent series inductance,esl)与负载并联放置,电流纹波会以输出电压纹波的方式显示。在图1中,输出电容c

out

的esr及esl分别以电阻r

esr

及电感l

esl

表示。

6.cot降压转换器因具有一些优点,例如快速的暂态响应及易于控制的高输入电压至低输出电压的调节功能而在工业上得到了广泛应用。然而,传统的cot降压转换器仍存在一些缺点,如由于低抗扰性、不佳的直流(direct-current,dc)调节及暂态响应而引起的抖动反应。

技术实现要素:

7.本发明实施例提供一种恒定导通时间(constant on-time,cot)降压转换器,包含

第一晶体管、第二晶体管、驱动电路、电感、第一电阻、第二电阻、电容、负载及反馈控制电路。第一晶体管包含第一端,用以接收输入电压;第二端,耦接于开关节点;及控制端。第二晶体管包含第一端,耦接于开关节点;第二端,耦接于接地端;及控制端。驱动电路耦接在第一晶体管的控制端及第二晶体管的控制端,用以控制第一晶体管及第二晶体管。电感包含第一端,耦接于开关节点;及第二端,耦接于输出节点。第一电阻包含第一端,耦接于输出节点;及第二端,耦接于反馈节点。第二电阻包含第一端,耦接于反馈节点;及第二端,耦接于接地端。电容包含第一端,耦接于输出节点;及第二端,耦接于接地端。负载包含第一端,耦接于输出节点;及第二端,耦接于接地端。反馈控制电路包含第一开关、第二开关、误差放大器、比较器、锁频回路电路、反相器及cot逻辑电路。第一开关包含第一端,耦接于反馈节点;第二端;及控制端。第二开关包含第一端,耦接在第一开关的第二端;第二端;及控制端。误差放大器包含负输入端,耦接在第一开关的第二端;正输入端,用以接收参考电压;及输出端,耦接于第二开关的第二端,用以输出误差信号。比较器用以将误差信号与反馈节点处的反馈电压进行比较及输出比较信号。锁频回路电路用以产生频率信号。反相器包含输入端,耦接于锁频回路电路及第二开关的控制端;及输出端,耦接在第一开关的控制端。cot逻辑电路用以接收频率信号及比较信号并产生cot信号至驱动电路。

附图说明

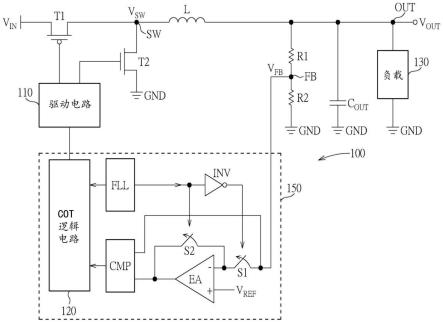

8.图1为现有技术的传统降压转换器的示意图。

9.图2为本发明实施例中一种cot降压转换器的示意图。

10.图3为图2中的输出电压信号的时序图。

11.【符号说明】

12.1:降压转换器

13.12,cmp:比较器

14.24,out:节点

15.14,110:驱动电路

16.100:cot降压转换器

17.120:cot逻辑电路

18.30,130:负载

19.150:反馈控制电路

20.c

out

:电容

21.ea:误差放大器

22.fb:反馈节点

23.fll:锁频回路电路

24.gnd:接地端

25.i

l

:电流

26.i

load

:负载电流

27.inv:反相器

28.l1,l:电感

29.r1:第一电阻

30.r2:第二电阻

31.r

esr

:电阻

32.l

esl

:电感

33.s1:第一开关

34.s2:第二开关

35.sw:开关节点

36.t0至t2:时间

37.t1:第一晶体管

38.t2:第二晶体管

[0039]vfb

:反馈电压

[0040]vin

:输入电压

[0041]vout

:输出电压

[0042]vref

:参考电压

[0043]vsw

:开关电压

具体实施方式

[0044]

通过参考下面的详细描述,并结合以下附图,可理解本公开,另本公开的各种附图已进行简化,已达成清楚说明本发明的目的,然各元件在各附图中并未按比例绘制。此外,附图中所示的每个元件的数量及尺寸仅为示例性质,并非用以限定本公开的范围。

[0045]

在整个说明书及所附发明权利要求书中会使用某些术语来称呼特定元件。如本领域技术人员所理解的,电子设备制造商可用不同的名称来称呼元件。本公开不受限于名称不同但功能相同的元件。在以下描述及权利要求中,用词“包含”及“具有”以开放式方式使用,因此应解释为“包含但不限于...”。

[0046]

图2为本发明实施例中一种cot降压转换器100的示意图。cot降压转换器100包含第一晶体管t1、第二晶体管t2、驱动电路110、电感l、第一电阻r1、第二电阻r2、电容c

out

、负载130及反馈控制电路150。反馈控制电路150包含第一开关s1、第二开关s2、误差放大器ea、比较器cmp、锁频回路电路fll、反相器inv及cot逻辑电路120。

[0047]

第一晶体管t1包含第一端,用以接收输入电压v

in

,第二端,耦接于开关节点sw,及控制端。第二晶体管t2包含第一端,耦接于开关节点sw,第二端,耦接于接地端gnd,及控制端。驱动电路110耦接在第一晶体管t1的控制端及第二晶体管t2的控制端,且驱动电路110用以控制第一晶体管t1及第二晶体管t2。电感l包含第一端,耦接于开关节点sw,及第二端,耦接于输出节点out。第一电阻r1包含第一端,耦接于输出节点out,及第二端,耦接于反馈节点fb。第二电阻r2包含第一端,耦接于反馈节点fb,及第二端,耦接于接地端gnd。电容c

out

包含第一端,耦接于输出节点out,及第二端,耦接于接地端gnd。负载130包含第一端,耦接于输出节点out,及第二端,耦接于接地端gnd。第一开关s1包含第一端,耦接于反馈节点fb,第二端及控制端。第二开关s2包含第一端,耦接在第一开关s1的第二端,第二端及控制端。误差放大器ea包含负输入端,耦接在第一开关s1的第二端,正输入端,用以接收参考电压v ref

,及输出端,耦接于第二开关s2的第二端,用以输出误差信号。比较器cmp用以比较误差信号及节点fb反馈的反馈电压v

fb

,及输出比较信号。锁频回路电路fll用以产生频率信号。反

相器inv包含输入端,耦接于锁频回路电路fll及第二开关s2的控制端,及输出端,耦接在第一开关s1的控制端。cot逻辑电路120用以接收频率信号及比较信号,并产生cot信号至驱动电路110。

[0048]

在本实施例中,第一开关s1及第二开关s2可以是金属氧化物半导体场效应晶体管(metal oxide semiconductor field effect,mosfet)。然而,在其他实施例中,第一开关s1及第二开关s2可以是双极接面晶体管(bipolar junction transistor)。在本实施例中,第一晶体管t1为p型晶体管。第二晶体管t2为n型晶体管。开关s1及s2及晶体管t1及t2的实际实现方式并非本发明的实施例的关键。

[0049]

晶体管t1及t2可接收输入电压v

in

及交替地导通及截止以在开关节点sw产生开关电压v

sw

。开关节点sw直接耦接于lc滤波器电路以产生调节的输出电压v

out

,lc滤波器电路包含电感l及电容c

out

,输出电压v

out

驱动负载130且具有实质上恒定的大小。

[0050]

cot降压转换器100包含反馈控制电路150,用以调节到lc滤波器电路的能量传递,以在电路的期望负载极限内将输出电压保持恒定。具体而言,反馈控制电路150可导通或关闭晶体管t1及t2以将输出电压v

out

调节至等于参考电压v

ref

,或调节至等于相关于参考电压v

ref

的电压值。分压器包含第一电阻r1及第二电阻r2,用以对输出电压v

out

分压,然后将分压作为反馈节点fb上的反馈电压v

fb

反馈至反馈控制电路150。在稳定状态下,反馈控制电路150的第一开关s1被设于导通,第二开关s2被设于截止。误差放大器ea可比较反馈电压v

fb

与参考电压v

ref

。误差放大器ea输出的误差信号被输出至比较器cmp,并且与反馈电压v

fb

进行比较。接着,cot逻辑电路120使用来自比较器cmp的比较结果信号及来自锁频回路电路fll的频率信号来产生驱动电路110的恒定导通时间(constant on-time,cot)信号。驱动电路110基于根据cot信号的恒定导通时间控制机制来产生晶体管t1及t2的控制信号。

[0051]

恒定导通时间反馈控制的开关动作基于反馈电压v

fb

中的纹波分量。为了实现恒定导通时间反馈控制,当反馈纹波降至参考电压v

ref

以下时,开关电压v

sw

会在固定导通时间内被切换至高电平。在固定导通时间结束时,开关电压v

sw

会被切换至低电平(电感不通电),直到反馈电压v

fb

再次降至参考电压v

ref

以下为止。此时将启动另一新的固定导通时间。若反馈电压v

fb

仍低于参考电压v

ref

,则开关电压v

sw

仅在最小截止时间内被切换为低电平,接着又再次变为固定导通时间的高电平。

[0052]

图3为图2中的输出电压信号v

out

的时序图。暂态响应可通过反馈控制电路150的配置来改善。在稳定状态下,第一开关s1导通,第二开关s2截止。在时间t0,开关电压v

sw

被切换,输出电压v

out

从4.82v升压到4.98v。此时,锁频回路电路fll发送频率信号以通过反相器inv导通第二开关s2及截止第一开关s1。误差放大器ea被设置为单一增益(unity gain),表示误差放大器ea输出的误差信号等于误差放大器ea负输入端的电压。通过将误差放大器ea设置为单一增益,cot降压转换器100可具有更快的暂态响应。

[0053]

如图3所示,cot降压转换器100可藉由快速的暂态响应将输出电压v

out

从4.98v逐渐调节回4.82v。当在时间t1将输出电压v

out

调节回4.82v时,锁频回路电路fll发送另一信号以截止第二开关s2并导通第一开关s1。因此,cot降压转换器100将再次在稳态下操作。

[0054]

同样如图3所示,相关技术的降压转换器1会将输出电压v

out

下调至例如为4.72v的较低电压,接着在时间t2,降压转换器1将缓慢地将输出电压v

out

调整回4.82v,与现有技术的降压转换器1相比,cot降压转换器100会改善输出电压的暂态响应时间。

[0055]

以上仅为本发明的优选实施例,凡依本发明权利要求书所做的均等变化与修饰,皆应属本发明的涵盖范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1