缓冲电路及电源装置的制作方法

1.以下的公开涉及缓冲电路。

背景技术:

2.缓冲电路是为了抑制对开关元件施加的浪涌电压而附加的。另一方面,在缓冲电路中产生的损失也成为问题。在日本特开2012

‑

39810号公报中公开了以削减缓冲电路的损失为目的的放电阻断器。

技术实现要素:

4.但是,即使使用这种放电阻断器,仍然有减少损失的余地。本公开的一方面的目的在于,提供与以往相比能够削减损耗的缓冲电路。

5.为了解决上述课题,本公开的一个方面所涉及的缓冲电路是一种与具备高电位节点、开关节点以及基准电位节点的开关电路连接的缓冲电路,上述开关电路具备:上侧开关元件,其连接在上述高电位节点与上述开关节点之间;下侧开关元件,其连接在上述开关节点与上述基准电位节点之间;以及旁路电容器,其连接在上述高电位节点与上述基准电位节点之间,上述缓冲电路具备缓冲电容器、二极管和线圈,上述缓冲电容器的正极与上述高电位节点连接,上述二极管的阳极与上述缓冲电容器的负极连接,且阴极与上述开关节点连接,上述线圈的一端与上述缓冲电容器的负极连接,且另一端与上述基准电位节点连接。

6.另外,为了解决上述课题,本公开的一个方面所涉及的缓冲电路是一种连接于高电位节点、开关节点和基准电位节点的缓冲电路,上述缓冲电路具备缓冲电容器、二极管和线圈,上述缓冲电容器的正极与上述高电位节点连接,上述二极管的阳极与上述缓冲电容器的负极连接,并且阴极与上述开关节点连接,上述线圈的一端连接于上述缓冲电容器的负极,并且另一端连接于上述基准电位节点。

7.根据本公开的一个方面,相较于以往能够进一步削减缓冲电路的损失。

附图说明

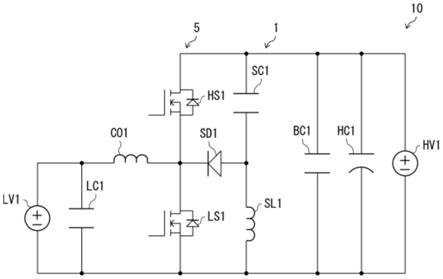

8.图1是表示第一实施方式的缓冲电路和电源电路的图。图2是表示缓冲电路的电流路径的图。图3是表示缓冲电路的各部的动作波形的图。图4是表示缓冲电路的线圈的电压波形的图。图5是表示第二实施方式的电源装置的图。

具体实施方式

9.[第一实施方式]在第一实施方式中,使用低损耗化的缓冲电路1,能够抑制在电源电路10中产生的浪涌电压。以下使用图1至图4对这些内容进行说明。关于具有与在第一实施方式中说明的

构件相同功能的构件,在以后的实施方式中,标注相同的附图标记,不重复其说明。为了简洁化,例如将“高电压电源hv1”也简单标记为“hv1”。另外,请注意以下所述的各数值仅为一个例子。

[0010]

(电源电路10的构成的概要)电源电路10是在低电压电源lv1与高电压电源hv1之间能够双向地传输电力的双向dcdc转换器。电源电路10中设置有缓冲电路1。缓冲电路1与电源电路10的开关电路5连接。

[0011]

(电源电路10的低电压部的构成)低电压部设置有lv1、电容器lc1和线圈co1。lv1的正极(+侧)的电压为200v,负极(

‑

侧)的电压为0v。lc1的静电电容是1μf。co1的电感是1mh,co1的平均电流是12a。

[0012]

(电源电路10的高电压部的构成)高电压部设置有hv1、电容器hc1和旁路电容器bc1。hv1的正极的电压为400v,负极的电压为0v。hc1的静电电容为1mf。bc1为静电电容为1μf的薄膜电容器。在第一实施方式中,将0v作为基准电位。并且,将0v的节点称为基准电位节点。另外,将比基准电位高的电位称为高电位。并且,将高电位的节点称为高电位节点。本说明书中的高电位例如为10v至1200v的电压。400v的节点是高电位节点的一个例子。

[0013]

bc1与hc1相比,设置于靠近以下所述的开关部的位置。bc1连接于高电位节点与基准电位节点之间。

[0014]

(电源电路10的开关部的构成)开关部具备上侧开关元件hs1和下侧开关元件ls1的半桥结构。开关电路5是在hs1和ls1上加入了bc1的结构。hs1以及ls1各自的栅极端子与后述的控制电路9连接。hs1和ls1的连接点是开关节点。co1的一端与开关节点连接。开关节点的电压通过hs1或者ls1的开关,交替地切换为400v和0v。

[0015]

hs1以及ls1均是漏极耐压为650v且导通电阻为50mω的共源共栅型的gan

‑

hemt。在图1的例子中,使用mosfet的电路符号来表示共源共栅gan

‑

hemt。hs1连接在高电位节点和开关节点之间。ls1连接于开关节点与基准电位节点之间。

[0016]

hs1以及ls1可以根据电源电路的种类而置换为其它开关元件。另外,本说明书中的开关元件的定义如下。

[0017]“开关元件”:可以使任意节点(例如:开关节点)的电压变化的元件。开关元件包括整流元件、晶体管元件以及磁性元件(例如:变压器的绕组以及线圈)。

[0018]

(电源电路10的缓冲电路1的构成)缓冲电路1具备缓冲电容器sc1、二极管sd1以及线圈sl1。

[0019]

sc1是耐压为630v、且静电电容为4.7nf的层叠陶瓷电容器。sc1的正极(图1中的上侧)与高电位节点连接。

[0020]

sd1是耐压为600v且导通开始时间点的vf为1v并导通状态下的电阻为0.13ω的frd(fast recovery diode)。sd1的阳极与sc1的负极(图1中的下侧)连接。sd1的阴极与开关节点连接。

[0021]

sl1是电感为470nh且电阻为70mω的芯片线圈。sl1的一端与sc1的负极连接。sl1的另一端与基准电位节点连接。

[0022]

(电源电路10的动作的说明)电源电路10进行与一般的双向dcdc转换器相同的动作。通过控制hs1或者ls1的接通和断开,双向地传输电力。在hs1截止时,在高电位节点和开关节点之间产生浪涌电压。换言之,hs1中产生浪涌电压。

[0023]

使用图2至图4,说明缓冲电路1的动作。

[0024]

图2是表示图1的缓冲电路1的电流路径的图。在图2中,示出了与图1相同的电路图,但省略了图1中的一部分标记。

[0025]

图3是基于共同的时间轴(横轴)示出缓冲电路1的各部的波形。图3的波形分别示出了如下电流:

·

hs1v(hs1的电压):以开关节点为基准的高电位节点的电压;

·

sc1v(sc1的电压):以负极为基准的正极的电压;

·

sl1v(sl1的电压):以基准电位节点侧的端子为基准的sc1侧的端子电压;

·

sd1i(sd1的电流):从阳极流向阴极的电流;

·

sl1i(sl1的电流):从sc1侧的端子流向基准电位节点侧的端子的电流;

·

sc1i(sc1的电流):从正极流向负极的电流。

[0026]

图4是放大了图3的sl1v后的图。

[0027]

(缓冲电路1的动作方法)在缓冲电路1的动作中,按此顺序执行以下的三个工序。

[0028]

第一工序:在高电位节点和开关节点之间产生浪涌电压;第二工序:经由sd1将浪涌电压充电至sc1;第三工序:使充电后的sc1的电压经由sl1向高电位节点放电。

[0029]

(第一工序:产生浪涌电压)在第一工序中,将hs1从开启切换为关闭。切换的时机是图3的时间点“1.47e

‑

5sec”。通过该切换,在以开关节点为基准的高电位节点上产生浪涌电压。在缓冲电路1未被连接至电源电路10的情况下,相对于稳态电压400v会产生浪涌电压480v(未图示)。在第一实施方式中,由于缓冲电路1与电源电路10连接,因此浪涌电压被抑制为410v(参照图3的hs1v)。

[0030]

(第二工序:将浪涌电压充电至sc1)上述降低后的浪涌电压(480v

‑

410v=70v)经由sd1被sc1吸收。换言之,该降低后的浪涌电压对sc1进行充电。充电的时机在紧接着第一工序之后(同时靠近紧接着之后)。充电的时机是图3的时间点“1.475e

‑

5sec”。能够确认sd1i以及sc1i的流动与sc1v的上升(sc1的充电)。sc1的充电路径是图2的箭头ar1。浪涌电压的能量(sc1的充电电流)从bc1作为电流被供给,经由sc1、sd1和ls1返回到bc1。

[0031]

(第三工序:将sc1的电压向高电位节点放电)被充电后的sc1的电压从稳定状态(400v)变化至410v(参照图3的sc1v)。sc1的放电开始的时机为紧邻第二工序之后。sc1的放电开始的时机是图3的时间点“1.48e

‑

5sec”。sc1的电压在“从1.48e

‑

5到1.53e

‑

5sec”的期间内被sl1缓慢地向高电位节点放电。在电源电路10的情况下,sc1的电压对与高电位节点连接的bc1进行充电。sc1的放电路径是从sc1,经由bc1和sl1返回至sc1的路径。sc1的放电路径为图2的箭头ar2。sc1的放电电流通过sl1

被平滑化,缓慢地对bc1进行充电。因此,能够降低缓冲电路1的损耗。

[0032]

(用于使缓冲电路1动作的改良点1~2)在第一实施方式中适用多个优选的改良点。以下,对这些优选的改良点进行说明。

[0033]

(改良点1:sc1的放电路径的电感大于sc1的充电路径的电感)在第一实施方式的例子中,路径ar1(即,由sc1、sd1、ls1和bc1构成的路径)的电感(以下,l1)被设计成小于50nh。因此,浪涌电压被sc1迅速地吸收,因此能够有效地抑制浪涌电压。另一方面,路径ar2(即,由sc1、sl1和bc1构成的路径)的电感(以下,l2)被设计成大于500nh。因此,由于sc1的放电被缓慢地实施,因此能够降低损耗。如上所述,优选将l2设计得较大,且将l1设计得较小。具体而言,l2优选为l1的2倍以上,进一步优选为l1的10倍以上。在第一实施方式中,l2被设计成l1的10倍。

[0034]

(改良点2:由于hs1的接通而产生的sl1v的谐振频率为10mhz以下)在此,不是hs1,而是sl1的浪涌电压的问题。由于该浪涌电压,sl1的电压发生谐振,从而产生sl1的损失。在本改良点2中,实施该损失的降低。

[0035]

在图4中,示出了将图3的sl1v的时间轴放大后的图表。图4的周期t1为3.00e

‑

7sec。因此,可以确认sl1v的谐振频率(以下,简称为“谐振频率”)为3.3mhz。

[0036]

在hs1接通时(图4的时间点“1.99e

‑

5sec”),由于向sl1施加浪涌电压,因此发生了sl1v的谐振。在缓冲电路1中,具备这样的动作模式。

[0037]

此外,本说明书中的sl1v的“谐振频率”是指sl1v所包含的频率成分中的、表示周期t1中最大的电压振幅的成分的频率(3.3mhz)。在图4的例子中,周期t1所包含的高频成分(例子:50mhz的成分)的电压振幅较小。因此,50mhz不符合本说明书中的共振频率的定义。

[0038]

表示最大电压振幅的sl1v的频率成分给sl1的损失带来很大的影响。因此,降低如上所述定义的谐振频率对于削减sl1的损失是有效的。

[0039]

通过将谐振频率抑制在10mhz以下,能够降低sl1的损失(核心损失和涡流损失)。通过将共振频率设为10mhz以下,也可以使用采用了铁氧体的小型的线圈。谐振频率由ar2的电感和sc1的静电电容决定。通过适当调整这两个值,能够将共振频率设定为10mhz以下。

[0040]

[第二实施方式]图5是表示具备电源电路10的电源装置100的图。电源电路10具备缓冲电路1、开关电路5以及控制电路9。控制电路9控制设置在电源电路10中的各元件的接通/断开的切换。特别是,控制电路9控制hs1以及ls1的接通/断开的切换。作为电源电路10的应用例,可以列举逆变器电路以及轮极pfc(power factor correction:功率因数校正)电路等。电源装置100在通过缓冲电路1来降低了损耗的状态下,能够抑制浪涌电压。

[0041]

〔总结〕本公开的第一方面所涉及的缓冲电路是与具备高电位节点、开关节点以及基准电位节点的开关电路连接的缓冲电路,上述开关电路具备:上侧开关元件,其连接在上述高电位节点与上述开关节点之间;下侧开关元件,其连接在上述开关节点与上述基准电位节点之间;以及旁路电容器,其连接在上述高电位节点与上述基准电位节点之间,上述缓冲电路具备缓冲电容器、二极管和线圈,上述缓冲电容器的正极与上述高电位节点连接,上述二极管的阳极与上述缓冲电容器的负极连接,且阴极与上述开关节点连接,上述线圈的一端与上述缓冲电容器的负极连接,且另一端与上述基准电位节点连接。

[0042]

根据上述构成,在上侧开关元件中产生的浪涌电压对缓冲电容器进行充电。缓冲电容器在由二极管、下侧开关元件和旁路电容器构成的路径中充电。该充电后的电压通过线圈被平滑地再生到旁路电容器(对旁路电容器进行充电)。因此,能够降低缓冲电路的损耗。

[0043]

在本公开的第二方面所涉及的缓冲电路中,由上述缓冲电容器、上述线圈以及上述旁路电容器构成的路径的电感,比由上述缓冲电容器、上述二极管、上述下侧开关元件以及上述旁路电容器构成的路径的电感大。

[0044]

根据上述的构成,浪涌电压能够以较小的电感的路径对缓冲电容器进行高速地充电。也就是说,能够利用缓冲电容器迅速地吸收浪涌电压。通过吸收浪涌电压而被充电的缓冲电容器的电压能够通过较大的电感被平滑化,并再生到旁路电容器。

[0045]

在本公开的第三方面所涉及的缓冲电路中,在上述上侧开关元件接通之后,施加于上述线圈的电压的谐振频率为10mhz以下。

[0046]

根据上述构成,通过将线圈中产生的电压的谐振频率抑制在10mhz以下,从而可以降低线圈的损耗。

[0047]

本公开的第四方面所涉及的电源装置具备本公开的一个方面所涉及的缓冲电路。

[0048]

根据上述构成,通过使用损失被降低后的缓冲电路,能够实现损失降低的电源装置。

[0049]

本公开的第五方面所涉及的缓冲电路是与高电位节点、开关节点和基准电位节点连接的缓冲电路,上述缓冲电路具备缓冲电容器、二极管和线圈,上述缓冲电容器的正极与上述高电位节点连接,上述二极管的阳极与上述缓冲电容器的负极连接,且阴极与上述开关节点连接,上述线圈的一端与上述缓冲电容器的负极连接,且另一端与上述基准电位节点连接。

[0050]

根据上述构成,在高电位节点和开关节点之间产生的浪涌电压经由二极管而被缓冲电容器吸收(缓冲电容器被充电)。该充电后的电压使用线圈被平滑地、缓慢地向高电位节点放电。因此,能够降低缓冲电路的损耗。

[0051]

[附记事项]本公开的一个方面并不限定于上述各实施方式,可以在权利要求所示的范围内进行各种变更,对于适当组合不同实施方式中分别公开的技术手段而得到的实施方式,也包括在本公开的一个方面的技术范围内。此外,通过将各实施方式分别公开的技术方案进行组合,能够形成新的技术特征。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1