静电放电防护电路的制作方法

1.本发明涉及一种静电放电防护电路,尤其涉及一种可提升静电放电防护能力的静电放电防护电路。

背景技术:

2.在现有常识中,为确保集成电路不受到静电放电的破坏,通常在集成电路中会加入静电放电防护电路,以提供静电放电电流的宣泄路径,并防止电路组件遭到破坏。在电源轨线间,现有技术常设置电源箝制(power clamp)电路以作为静电放电防护电路。

3.由于静电放电现象中,集成电路的电源轨线间有可能产生正脉冲电压或负脉冲电压。静电放电防护电路需要因应这些状况以有效产生电流宣泄路径,方能针对集成电路执行有效的保护动作。现有技术常会因应静电放电现象中不同的电压脉冲状态来设置电路组件,以提供电流宣泄路径。这样的做法常需要额外的电路组件,并造成电路布局面积的浪费。

技术实现要素:

4.本发明是针对一种静电放电防护电路,可减低电路布局面积,并提升静电放电的防护能力。

5.根据本发明的实施例,静电放电防护电路包括第一晶体管、第二晶体管、电容、分压电路以及第一二极管。第一晶体管耦接在第一电源轨线以及第二电源轨线间。第二晶体管耦接在第一电源轨线以及第二电源轨线间,第二晶体管的块体耦接至第一晶体管的控制端。电容耦接在第一电源轨线以及第二晶体管的控制端间。分压电路耦接在第二晶体管的控制端与第二电源轨线间,具有一分压电压输出端以耦接至第二晶体管的块体。第一二极管耦接在分压电压输出端以及第二电源轨线间。

6.根据上述,本发明通过在第二晶体管的块体与用以提供第二晶体管控制端偏压电压的电容电阻网络间形成一二极管。通过此二极管,在负的电压脉冲产生时,可提供路径以实时的导通第一晶体管,并快速提供静电放电电流的宣泄路径,有效提升静电放电防护的能力。在本实施例中,二极管可以通过集成电路中的电阻(n型)以及基体(p型)的材质来形成,不需要额外的布局安排,可节省电路的面积。

附图说明

7.包含附图以便进一步理解本发明,且附图并入本说明书中并构成本说明书的一部分。附图说明本发明的实施例,并与描述一起用于解释本发明的原理。

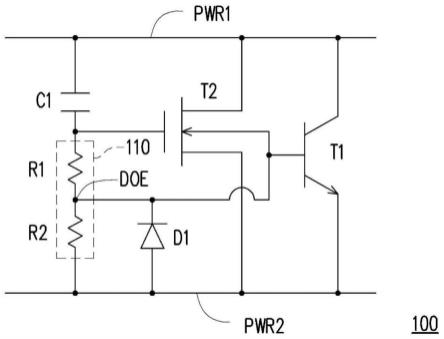

8.图1为本发明一实施例的静电放电防护电路的示意图;

9.图2为本发明图1实施例中的电阻r2以及二极管d1的布局结构的剖面图;

10.图3a以及图3b为本发明实施例的静电放电防护电路的静电放电防护动作示意图;

11.图4为本发明另一实施例的静电放电防护电路的电路示意图;

12.图5为本发明图4实施例的静电放电防护电路400的部分布局架构的俯视图。

13.附图标号说明

14.100、300、400:静电放电防护电路;

15.110、410:分压电路;

16.210:井区;

17.211、212、221:掺杂区;

18.220:基底;

19.bk:块体;

20.c1:电容;

21.d1、d2:二极管;

22.doe:分压电压输出端;

23.g1:栅极;

24.gnd:接地电压;

25.m1、m2:传输导线;

26.nd1~nd3:掺杂区;

27.nw:n型井区;

28.path1~path4:路径;

29.ps1:负脉冲电压;

30.ps2:正脉冲电压;

31.pwr1、pwr2:电源轨线;

32.r1、r2:电阻;

33.sub:基底;

34.t1、t2晶体管;

35.vdd:电源电压;

36.via1~via5:连接窗。

具体实施方式

37.现将详细地参考本发明的示范性实施例,示范性实施例的实例说明于附图中。只要有可能,相同元件符号在附图和描述中用来表示相同或相似部分。

38.请参照图1,图1为本发明一实施例的静电放电防护电路的示意图。静电放电防护电路100包括晶体管t1、t2、电容c1、分压电路110以及二极管d1。晶体管t1耦接在第一电源轨线pwr1以及第二电源轨线pwr2间。晶体管t2耦接在第一电源轨线pwr1以及第二电源轨线pwr2间。晶体管t2的块体(bulk)耦接至该晶体管t1的控制端。在本实施例中,晶体管t1为双极性晶体管(bipolar junction transistor,bjt),晶体管t2则可以为金氧半场效晶体管(metal-oxide-semiconductor field-effect transistor,mosfet)。细节上,晶体管t1可以为npn型双极性晶体管,晶体管t2则可以为n型金氧半场效晶体管。

39.在本实施例中,第一电源轨线pwr1可用以接收电源电压,第二电源轨线pwr2则可用以接收接地电压。

40.另外,电容c1耦接在第一电源轨线pwr1以及晶体管t2的控制端间,其中晶体管t2

的控制端为其栅极端。分压电路110耦接在晶体管t2的控制端与第二电源轨线pwr2间。分压电路110具有分压电压输出端doe以耦接至晶体管t2的块体。在本实施例中,分压电路110包括电阻r1以及r2。电阻r1的一端耦接至晶体管t2的控制端,电阻r1的另一端耦接至分压电压输出端doe。电阻r2的一端耦接至分压电压输出端doe,电阻r2的另一端则耦接至第二电源轨线pwr2。

41.二极管d1的阳极耦接至第二电源轨线pwr2,二极管d1的阴极则耦接至分压电压输出端doe,并通过分压电压输出端doe以耦接至晶体管t2的块体。

42.在本实施例中,电容c1以及分压电路110用以在当第一电源轨线pwr1上,因静电放电现象产生正脉冲电压时,针对正脉冲电压进行分压,并在分压电压输出端doe产生一偏压电压以使晶体管t1被导通。通过导通晶体管t1来产生电流宣泄路径,以达到静电放电的防护功能。

43.另一方面,当第一电源轨线pwr1上,因静电放电现象而产生负脉冲电压时,二极管d1可对应负脉冲电压而被导通,并提供偏压电压以导通晶体管t1。同样的,可通过导通晶体管t1来产生电流宣泄路径,以达到静电放电的防护功能。

44.以下请同步参照图1以及图2,图2为本发明图1实施例中的电阻r2以及二极管d1的布局结构的剖面图。其中,静电放电防护电路100设置在集成电路中。集成电路中具有基底(substrate)220以及井区(well)210。井区210设置在基底220中。井区210包括掺杂区211以及212。在本实施例中,基底220可以为p型基底,井区可以为n型井区,掺杂区211以及212则可以皆为n+型掺杂区。

45.本实施方式中,电阻r2可以利用为n型井区,形成在掺杂区211以及212间。并通过使掺杂区211耦接至分压电压输出端doe,使掺杂区212耦接至第二电源轨线pwr2,可以实现图1的电路架构。

46.在另一方面,基底220另具有掺杂区221。其中,掺杂区221可以为p+型掺杂区,并耦接至第二电源轨线pwr2。如此一来,由基底220以及井区210所形成的p-n接面,可以建构出二极管d1。并且,二极管d1的阳极可通过掺杂区221耦接至第二电源轨线pwr2,二极管d1的阴极则可通过掺杂区212耦接至分压电压输出端doe。

47.由上述的说明不难得知,本实施方式中的二极管d1可通过电阻r2的布局时所产生的寄生效应所构成,并不需要额外的布局面积。因此,本发明实施例的静电放电防护电路100的布局面积可以有效的被缩减。

48.以下请参照图3a以及图3b,图3a以及图3b为本发明实施例的静电放电防护电路的静电放电防护动作示意图。在图3a中,静电放电防护电路300具有与静电放电防护电路100相同的电路架构,相关细节不再赘述。当在第一电源轨线pwr1以及第二电源轨线pwr2间因静电放电现象而产生负脉冲电压ps1时,二极管d1可根据负脉冲电压ps1而被导通,并在负脉冲电压ps1、二极管d1以及晶体管t1的控制端(基极)间产生一路径path1。通过路径path1,一偏压电压vb可根据负脉冲电压ps1来被提供至晶体管t1的控制端,并使晶体管t1被导通。如此一来,晶体管t1可提供作为静电放电保护的电流宣泄路径path2。

49.在另一方面,当在第一电源轨线pwr1以及第二电源轨线pwr2间因静电放电现象而产生正脉冲电压ps2时,电容c1、电阻r1以及r2所构成的电容电阻网络可以根据正脉冲电压ps2在分压电压输出端doe上产生偏压电压vb。偏压电压vb并可通过路径path3提供至晶体

管t1的控制端,如此一来,晶体管t1可以被导通并提供作为静电放电保护的电流宣泄路径path4。

50.以下请参照图4,图4为本发明另一实施例的静电放电防护电路的电路示意图。静电放电防护电路400包括晶体管t1、t2、电容c1、分压电路410以及二极管d1、d2。晶体管t1耦接第一电源轨线pwr1以及第二电源轨线pwr2间。晶体管t2耦接在第一电源轨线pwr1以及第二电源轨线pwr2间。晶体管t2的块体耦接至该晶体管t1的控制端。在本实施例中,晶体管t1为双极性晶体管,晶体管t2则可以为金氧半场效晶体管。细节上,晶体管t1可以为npn型双极性晶体管,晶体管t2则可以为n型金氧半场效晶体管。

51.另外,电容c1耦接在第一电源轨线pwr1以及晶体管t2的控制端间,其中晶体管t2的控制端栅极端。分压电路410耦接晶体管t2的控制端与第二电源轨线pwr2间。分压电路410具有分压电压输出端doe以耦接至晶体管t2的块体。其中,在本实施例中,分压电路410包括电阻r1以及r2。电阻r1的一端耦接至晶体管t2的控制端,电阻r1的另一端耦接至分压电压输出端doe。电阻r2的一端耦接至分压电压输出端doe,电阻r2的另一端则耦接至第二电源轨线pwr2。第一电源轨线pwr1以及第二电源轨线pwr2分别接收电源电压vdd以及接地电压gnd。

52.在本实施例中,二极管d1的阳极耦接至第二电源轨线pwr2,二极管d1的阴极耦接至分压电压输出端doe,并通过分压电压输出端doe以耦接至晶体管t2的块体。此外,与前述实施例不相同的是,本实施例的静电放电防护电路400还包括二极管d2。二极管d2的阳极耦接至分压电压输出端doe,二极管d2的阴极则耦接至晶体管t2的控制端,也就是晶体管t2的栅极。

53.以下请参照图5,图5为本发明图4实施例的静电放电防护电路400的部分布局架构的俯视图。其中,电容c1的第一极板通过多个连接窗via2以电性连接至第一电源轨线pwr1。第一电源轨线pwr1用以接收电源电压vdd。电容c1的第二极板则可通过多个连接窗via3以及传输导线m1以电性连接至晶体管t2的栅极g1。另外,电容c1的第二极板并通过传输导线m2以电性连接至n型井区nw。n型井区中具有多个掺杂区nd1~nd3,其中掺杂区nd1~nd2间可形成电阻r1,掺杂区nd2~nd3间则可形成电阻r2。掺杂区nd2上并可提供分压电压输出端doe。

54.另外,n型井区nw设置在基底sub中,基底sub通过多个连接窗via4以电性连接至第二电源轨线pwr2。第二电源轨线pwr2用以接收接地电压gnd。基底sub为p型基底,并与n型井区nw形成p-n接面而产生二极管d1、d2。也就是说,在本发明中,二极管d1、d2并不需要额外进行布局,有效减低电路所需的面积。

55.此外,晶体管t2的块体bk通过多个连接窗via1以电性连接至分压电压输出端doe。晶体管t2的第一端(汲极)通过多个连接窗via6以电性耦接至第一电源轨线pwr1,晶体管t2的第二端(源极)则通过多个连接窗via5以电性耦接至第二电源轨线pwr2。晶体管t1的控制端(基极)内嵌于晶体管t2的块体,并通过多个连接窗via1以电性耦接于分压电压输出端doe。晶体管t1的第一端(集极)内嵌于晶体管t2的第一端(汲极),并通过多个连接窗via6以电性耦接至第一电源轨线pwr1。晶体管t1的第二端(射极)内嵌于晶体管t2的第二端(源极),并以多个连接窗v1a5以电性耦接于第二电源轨线pwr2。因此,晶体管t1并不需要额外的布局空间,可有效降低整体电路所需面积。

56.根据上述,本发明提出的静电放电防护电路,在不需要占去额外布局面积的前提下,通过在金氧半场效晶体管的块体与第二电源轨线间设置反向偏压的二极管,可有效提升负脉冲电压的静电放电现象的防护能力,进以提升集成电路的可靠度。

57.最后应说明的是:以上各实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述各实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1