一种高压开关电源纹波抑制电路的制作方法

1.本发明属于高压电源技术领域,特别是一种高压开关电源纹波抑制电路。

背景技术:

2.高压电源在真空放大器中应用时往往对输出的纹波要求较高,特别是在成像、空间合成等系统方案中,高压电源的纹波直接影响末级放大器的相位、噪声以及杂散。

3.电真空放大器工作电压高,如果通过线性电源直接对其供电,线性电源的调整管工作电压高,调整管需选用电子管实现,电子管高压线性电源具有体积大、效率低、可靠性差等缺点。

4.目前随着开关电源的技术不断革新,小型化的高压开关电源已经基本取代了电子管高压线性电源,然而一些较高要求的场合高压开关电源的输出纹波又难以满足设计需求。

5.综上,电子管高压线性电源纹波小但体积大、效率低、可靠性差,高压开关电源纹波大,难以同时实现小型化、高效率、高可靠与低纹波。

技术实现要素:

6.本发明的目的在于提供一种高压开关电源纹波抑制电路,实现对高压输出的纹波抑制,降低串联调整纹波抑制电路两端的工作电压,在实现高压纹波抑制的同时减小电路体积、提高效率及可靠性。

7.实现本发明目的的技术解决方案是:一种高压开关电源纹波抑制电路,包括开关功率变换电路、高压变压器、pwm控制电路、高压整流滤波电路、串联调整纹波抑制电路和高压分压取样电路;

8.所述开关功率变换电路、高压变压器、高压整流滤波电路顺次连接,串联调整纹波抑制电路串联于高压整流滤波电路与地端之间,pwm控制电路与串联调整纹波抑制电路并联设置且输出接入开关功率变换电路;

9.pwm控制电路的取样反馈电压为串联调整纹波抑制电路两端电压,而串联调整纹波抑制电路的取样反馈电压通过高压分压取样电路对高压输出按比例取样完成;串联调整纹波抑制电路和pwm控制电路形成两个级联的电压反馈环路实现高压开关电源的输出电压反馈调节。

10.进一步地,所述串联调整纹波抑制电路包括晶体管v1、运算放大器n1,所述晶体管v1的漏源分别并联吸收电阻r1和瞬态电压抑制二极管d1。

11.进一步地,所述高压分压取样电路由第八电阻r8、第九电阻r9与第十电阻r10串联组成。

12.进一步地,所述串联调整纹波抑制电路中的晶体管v1为线性调整管,工作在线性区,漏源等效电阻随栅极电压的变化而变化。

13.进一步地,所述运算放大器n1的同相输入端pin3通过隔离电阻r7接第九电阻r9与

第十电阻r10的公共端,运算放大器n1的反相输入端pin2接电压基准ref,运算放大器n1的输出端通过驱动电阻r5接晶体管v1,驱动匹配电阻r4并联在晶体管v1的漏源之间。

14.进一步地,串联调整纹波抑制电路的稳压反馈过程为:当扰动导致高压开关电源的输出电压vk绝对值大于设定值时,阴极分压点即运算放大器n1的同相输入端pin3电压变低,运算放大器n1输出端pin1电压变低,晶体管v1栅极电压变低,晶体管v1漏源导通电阻变大,晶体管v1漏源电压变高,串联调整纹波抑制电路压降增大,总输出vk变低;

15.反之当当扰动导致高压开关电源的输出电压vk绝对值小于设定值时,阴极分压点即运算放大器n1的同相输入端pin3电压变高,运算放大器n1输出端pin1电压变高,晶体管v1栅极电压变高,晶体管v1漏源导通电阻变小,晶体管v1漏源电压变低,串联调整纹波抑制电路压降减小,总输出vk变高;

16.由此完成所述串联调整纹波抑制电路的闭环负反馈,即线性稳压反馈。

17.进一步地,pwm控制电路的稳压反馈过程为:当扰动导致所述串联调整纹波抑制电路中晶体管v1漏源电压降低时,pwm控制电路接收到串联调整纹波抑制电路输出的取样反馈提高开关功率变换电路增益,既而通过高压变压器提高高压整流滤波电路的电压;反之当扰动导致所述串联调整纹波抑制电路中晶体管v1漏源电压升高时,pwm控制电路接收到串联调整纹波抑制电路输出的取样反馈降低开关功率变换电路增益,既而通过高压变压器降低高压整流滤波电路的电压,完成所述pwm控制电路的闭环负反馈,即开关稳压反馈。

18.本发明与现有技术相比,其显著优点为:

19.(1)纹波低:在高压开关电源上级联了串联调整纹波抑制电路,降低了输出纹波;

20.(2)体积小:通过开关稳压和线性稳压的级联降低了线性调整电路的电压,通过晶体管实现了线性调整,减小了纹波抑制电路的体积。

21.(3)效率高:通过开关稳压和线性稳压的级联降低了线性调整电路的电压,主功率变换部分为开关电源,线性调整电路部分电压较低,在实现线性稳压纹波抑制的同时效率高;

22.(4)可靠性高:通过开关稳压和线性稳压的级联降低了线性调整电路的电压,规避了高压线性电源的电子管使用,提高了可靠性。

附图说明

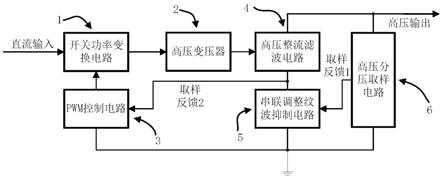

23.图1是本发明的高压开关电源纹波抑制电路电路框图。

24.图2是本发明的高压整流滤波电路、高压分压取样电路与串联调整纹波抑制电路部分的原理图。

25.图3是本发明的电路启动时总高压输出vk与串联调整纹波抑制电路部分电源vsense的波形示意图。

具体实施方式

26.本发明提供一种高压开关电源纹波抑制电路,通过在高压整流滤波电路下端串联的串联调整纹波抑制电路实现对高压输出的纹波抑制,将开关电源和串联调整线性电源的两个反馈环路级联调整,实现了对高压输出的纹波抑制,也降低了串联调整纹波抑制电路两端的工作电压,通过晶体管即可实现串联调整,无需高压电子管进行串联线性稳压,在实

现高压纹波抑制的同时减小了电路体积、提高了效率及可靠性。

27.本发明一种高压开关电源纹波抑制电路,包括开关功率变换电路1、高压变压器2、pwm控制电路3、高压整流滤波电路4、串联调整纹波抑制电路5和高压分压取样电路6;

28.所述开关功率变换电路1、高压变压器2、高压整流滤波电路4顺次连接,串联调整纹波抑制电路5串联于高压整流滤波电路4与地端之间,pwm控制电路3与串联调整纹波抑制电路5并联设置且输出接入开关功率变换电路1;

29.pwm控制电路3的取样反馈电压为串联调整纹波抑制电路5两端电压,而串联调整纹波抑制电路5的取样反馈电压通过高压分压取样电路6对高压输出按比例取样完成;串联调整纹波抑制电路5和pwm控制电路3形成两个级联的电压反馈环路实现高压开关电源的输出电压反馈调节。

30.进一步地,所述串联调整纹波抑制电路5包括晶体管v1、运算放大器n1,所述晶体管v1的漏源分别并联吸收电阻r1和瞬态电压抑制二极管d1。

31.进一步地,所述高压分压取样电路6由第八电阻r8、第九电阻r9与第十电阻r10串联组成。

32.进一步地,所述串联调整纹波抑制电路5中的晶体管v1为线性调整管,工作在线性区,漏源等效电阻随栅极电压的变化而变化。

33.进一步地,所述运算放大器n1的同相输入端pin3通过隔离电阻r7接第九电阻r9与第十电阻r10的公共端,运算放大器n1的反相输入端pin2接电压基准ref,运算放大器n1的输出端通过驱动电阻r5接晶体管v1,驱动匹配电阻r4并联在晶体管v1的漏源之间。

34.进一步地,串联调整纹波抑制电路5的稳压反馈过程为:当扰动导致高压开关电源的输出电压vk绝对值大于设定值时,阴极分压点即运算放大器n1的同相输入端pin3电压变低,运算放大器n1输出端pin1电压变低,晶体管v1栅极电压变低,晶体管v1漏源导通电阻变大,晶体管v1漏源电压变高,串联调整纹波抑制电路5压降增大,总输出vk变低;

35.反之当当扰动导致高压开关电源的输出电压vk绝对值小于设定值时,阴极分压点即运算放大器n1的同相输入端pin3电压变高,运算放大器n1输出端pin1电压变高,晶体管v1栅极电压变高,晶体管v1漏源导通电阻变小,晶体管v1漏源电压变低,串联调整纹波抑制电路5压降减小,总输出vk变高;

36.由此完成所述串联调整纹波抑制电路5的闭环负反馈,即线性稳压反馈。

37.进一步地,pwm控制电路3的稳压反馈过程为:当扰动导致所述串联调整纹波抑制电路5中晶体管v1漏源电压降低时,pwm控制电路3接收到串联调整纹波抑制电路5输出的取样反馈提高开关功率变换电路1增益,既而通过高压变压器2提高高压整流滤波电路4的电压;反之当扰动导致所述串联调整纹波抑制电路5中晶体管v1漏源电压升高时,pwm控制电路3接收到串联调整纹波抑制电路5输出的取样反馈降低开关功率变换电路1增益,既而通过高压变压器2降低高压整流滤波电路4的电压,完成所述pwm控制电路3的闭环负反馈,即开关稳压反馈。

38.下面结合附图及具体实施例对本发明作进一步详细描述。

39.实施例

40.如图1所示,本发明的一种高压开关电源纹波抑制电路电路框图,包括:

41.开关功率变换电路1、高压变压器2、pwm控制电路3、高压整流滤波电路4、串联调整

纹波抑制电路5和高压分压取样电路6以及它们之间特定的连接方式;所述开关功率变换电路1、高压变压器2、pwm控制电路3、高压整流滤波电路4除电压反馈环路外,功率开关回路的电路结构原理与常规高压开关电源相同。

42.所述pwm控制电路3的反馈取样电压为串联调整纹波抑制电路5两端电压,而串联调整纹波抑制电路5的取样反馈电压是通过高压分压取样电路6对高压输出按比例取样完成的。

43.所述高压开关电源的输出电压反馈调节是通过的串联调整纹波抑制电路5和pwm控制电路3两个级联的电压反馈环路实现的。

44.如图2所示,本发明的高压整流滤波电路4、高压分压取样电路6与串联调整纹波抑制电路5部分包括:高压二极管与高压电容组成的倍压整流电路,电阻r1~r5,瞬态电压抑制二极管d1,晶体管v1、运算放大器n1及其外围电路。

45.所述高压分压取样电路6由高压精密电阻r8、r9与分压电阻r10串联组成。

46.所述串联调整纹波抑制电路5在晶体管v1的漏源并联了吸收电阻r1和瞬态电压抑制二极管d1。

47.所述串联调整纹波抑制电路5中的晶体管v1为线性调整管,其工作在线性区,漏源等效电阻随栅极电压的变化而变化。运算放大器n1的同相输入端pin3通过隔离电阻r7接阴极分压取样电阻r9与r10的连接点,n1的反相输入端pin2接电压基准(高压电源输出为负,基准及取样电压均为负),运算放大器n1的输出端通过驱动电阻r5接晶体管v1,驱动匹配电阻r4并联在晶体管v1的漏源之间。线性调整的稳压反馈过程为当扰动导致vk偏高(vk为负,偏高默认指绝对值偏高)时,阴极分压点即运算放大器n1的同相输入端pin3电压变低,运算放大器n1输出端pin1电压变低,晶体管v1栅极电压变低,晶体管v1漏源导通电阻变大,晶体管v1漏源电压变高,串联调整纹波抑制电路5压降增大,总输出vk变低。

48.所述串联调整纹波抑制电路5的稳压反馈过程为当扰动导致vk偏高(vk为负,偏高默认指绝对值偏高)时,阴极分压点即运算放大器n1的同相输入端pin3电压变低,运算放大器n1输出端pin1电压变低,晶体管v1栅极电压变低,晶体管v1漏源导通电阻变大,晶体管v1漏源电压变高,串联调整纹波抑制电路5压降增大,总输出vk变低,反之当扰动导致vk偏低,亦然,由此完成所述串联调整纹波抑制电路5闭环负反馈,即线性稳压反馈。

49.所述pwm控制电路3的稳压反馈过程为当扰动导致所述串联调整纹波抑制电路5中晶体管v1漏源电压降低时,pwm控制电路3接收到取样反馈2提高开关功率变换电路1增益,既而通过高压变压器2提高了高压整流滤波电路4的电压,反之当扰动导致所述串联调整纹波抑制电路5中晶体管v1漏源电压升高时,亦然,完成了所述pwm控制电路3的闭环负反馈,即开关稳压反馈。

50.较佳的,以本实例说明,总输出vk为

‑

10.5kv,将所述串联调整纹波抑制电路5两端电压设定为100v,晶体管v1选用sk1317,瞬态电压抑制二极管选用p6ke440ca,运算放大器n1选用lm158j。

51.较佳的,以螺线电流2ma,总流50ma为例。

52.总输出功率为

53.pout=uk

×

ik=10.5kv

×

50ma=525w。

54.所述串联调整纹波抑制电路5消耗功率

55.ploss=vds

×

ih=100v

×

2ma=200mw

56.可知,所述串联调整纹波抑制电路5实际功耗小,实现了在高转换效率情况下的纹波抑制。

57.图3是本发明的电路启动时总高压输出vk与串联调整纹波抑制电路部分电源vsense的波形示意图。

58.电压vk和vsense对地电压一正一负,为了方便比较,在示意图中都变为正电压进行电压幅度的时域分析。

59.在启动时,vk为0v,ref为负,此时运算放大器n1的输出端为高电平,晶体管v1饱和导通,压降接近0v,pwm控制电路3处于满占空比的缓启动过程,输出电压vk随高压整流滤波电路4的电压升高同步升高,当输出vk逐渐升高到其取样反馈电压接近反馈基准ref时,串联调整纹波抑制电路5进入闭环反馈状态,晶体管v1进入线性工作区,此时,pwm控制电路3的增益根据晶体管v1漏源电压的取样进行反馈调节。

60.本发明的高压开关电源纹波抑制电路,通过高压开关电源和线性稳压电源的级联反馈,利用高压开关电源完成主功率部分的升压变换,将线性稳压电源部分的工作电压控制在晶体管调整器的可靠工作范围,兼顾了线性电源的纹波优势和开关电源的高效率、高可靠、小型化。

61.综上所述,以上仅为本发明的较佳实施例而已,并非用于限定本发明的保护范围。凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1