具有整流调节器的LDO自由无线功率接收器的制作方法

具有整流调节器的ldo自由无线功率接收器

技术领域

1.本公开涉及无线功率传输领域,并且具体地涉及硬件、针对硬件的操作技术、以及用于使桥式整流器执行整流功能和调节功能的方法。

背景技术:

2.便携式电子设备(诸如,智能手机、智能手表、音频输出设备(耳塞式耳机、头戴式耳机))以及可穿戴设备依靠电池供电,而不是来自通过有线传输线和配电系统向其传输的有线电源。用于该设备的电池通常是可再充电的,并且因此需要为该电池再充电的方法。

3.大多数便携式电子设备包括充电端口,通常符合micro usb或usb-c标准,连接到电源的电源线可以被插入到该充电端口中以提供用于它们的电池的再充电。然而,该充电端口可能难以提高电子设备的防水性,并且容易因重复使用而损坏。此外,一些更小的便携式电子设备(例如,耳塞式耳机和智能手表)可能缺乏可用空间来提供充电端口。此外,一些用户可能发现将电源线插入电子设备的充电端口以对该设备的电池充电很麻烦。

4.因此,为了解决这些问题,已经开发了无线功率传输。如图1所示,典型的现有技术无线功率传输系统10利用包括传输线圈lp和串行电容cp的发射器11形成由来自电源12(通常为有线连接,但在某些情况下为电池)的电功率驱动的串行谐振l,c网络,生成时变电场,以及利用包括接收线圈ls和串行电容cs的接收器15形成类似的串行谐振l,c网络,其中时变电场感应出ac电流。存在其它可能的配置,其中l,c并行在初级侧和/或次级侧,提供四种可能的方案——串行-串行、串行-并行、并行-串行、以及并行-并行。取决于应用,每种方案都可能存在一些优势和/或劣势,并且串行-串行配置在针对移动设备市场的最近发展中被最广泛地使用。接收器15包括桥式整流器16(由所图示的二极管d1-d4组成),该桥式整流器16对ac电流进行整流以产生dc电流,该dc电流对连接到调节器17的输入节点nin的槽路电容器ctank进行充电到调节器输入电压。调节器17(通常为低压差放大器)在其输出节点nout处产生经调节的输出电压,该经调节的输出电压被提供到负载(由负载电阻r1和负载电容c1表示)。

5.尽管这种现有技术无线功率传输系统10是功能性的并且被广泛使用,但是调节器17的使用由于调节器17使用大功率mos器件而消耗了大量的集成电路面积。由于这种无线功率传输系统10主要被用在便携式电子设备中,因此该面积消耗是不合需要的。因此,需要进一步开发无线功率传输系统。

技术实现要素:

6.本文公开了桥式整流器和相关联的控制电路装置,该桥式整流器和相关联的控制电路共同形成“整流调节器(regtifier)”,能够对输入时变电压进行整流以及调节所产生的经整流的输出电压。为了实现这个,可以经由模拟控制(以增加那些晶体管的导通电路)或经由脉宽调制(以在阶段结束之前关断那些晶体管)来调制在给定的阶段期间导通的桥整流器的晶体管的栅极电压。备选地或附加地,在给定的阶段期间将以其它方式关断的桥

式整流器的晶体管可以被接通以帮助耗散过量功率并且由此调节输出电压。在本设计中不使用传统的电压调节器,诸如低压差放大器。

附图说明

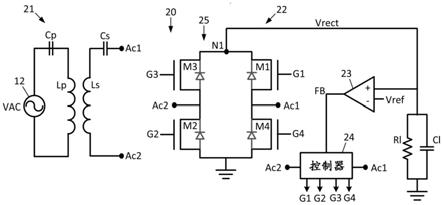

7.图1是现有技术无线功率传输系统的示意框图。

8.图2是本文中所公开的无线功率传输系统的示意框图,其中桥式整流器还执行调节功能,使能没有附加的电压调节电路。

9.图3是示出了图2的无线功率传输系统在操作中(当反馈回路正在控制桥式整流器以执行同相串行电压调节时)的电压的时序图。

10.图4是图2的无线功率传输系统的示意框图,该示意框图示出了在图3的同相串行电压调节的阶段a期间的无线功率传输系统的操作。

11.图5是图2的无线功率传输系统的示意框图,该示意框图示出了在图3的同相串行电压调节的阶段b期间的无线功率传输系统的操作。

12.图6是示出了图2的无线功率传输系统在操作中(当反馈回路正在控制桥式整流器以执行反相并行电压调节时)的电压的时序图。

13.图7是图2的无线功率传输系统的示意框图,该示意框图示出了在图6的反相并行电压调节的阶段a期间的无线功率传输系统的操作。

14.图8是图2的无线功率传输系统的示意框图,该示意框图示出了在图6的反相并行电压调节的阶段b期间的无线功率传输系统的操作。

15.图9是示出了图2的无线功率传输系统在操作中(当反馈回路正在控制桥式整流器以执行低侧同相串行电压调节时)的电压的时序图。在该示例中,调节仅被施加在低侧上,用于允许更好地了解依据本文中所公开的无线功率传输系统被施加到低侧的驱动信号与依据现有技术被施加到高侧的常规驱动信号之间的实质差异。

16.图10是示出了图2的无线功率传输系统在操作中(当反馈回路正在控制桥式整流器以执行低侧反相并行电压调节时)的电压的时序图。

17.图11是示出了图2的无线功率传输系统在操作中的电压的时序图,其中反馈回路在控制桥式整流器以执行同相串行电压调节和控制桥式整流器以执行图示了在功率传输期间被传输的fsk符号的反相并行电压调节之间进行切换。

18.图12是示出了当使用基于pwm的同相串行电压调节来操作时反馈信号fb和经调制的晶体管的pwm控制的时序图。

19.图13是示出了图2的无线功率传输系统在操作中(当反馈回路正在控制桥式整流器以执行低侧基于pwm的同相串行电压调节时)的电压的时序图。

20.图14是示出了当反馈回路正在控制桥式整流器以执行低侧基于pwm的同相串行电压调节时的可用的三种不同的pwm控制技术的时序图。

21.图15是针对图2的整流调节器的备选配置的示意图。

22.图16是示出了当反馈回路正在控制桥式整流器以使用图16的整流调节器执行低侧基于pwm的同相串行电压调节时的可用的pwm控制技术中的一个pwm控制技术的时序图。

23.图17a是在图2的控制器内的ac1和ac2信号以及相关联的产生的ga信号和gb信号的时序图。

24.图17b是在图2的控制器内用于产生ga信号和gb信号所使用的迟滞比较器的输出/输入传递函数。

25.图17c是用于产生ga信号的迟滞比较器的示意图。

26.图17d是用于产生gb信号的迟滞比较器的示意图。

27.图18a是图示了在图2的控制器内用于在同相串行电压调节与反相并行电压调节之间切换图2的整流调节器的模式选择电路装置的示意图。

28.图18b是图示了在图2的控制器内用于在同相串行电压调节与反向并行电压调节之间切换图2的整流调节器并且支持基于pwm的同相串行电压调节的模式选择电路的示意图。

29.图18c是图示了存在放大器和比较器作为反馈回路的示意图。

30.图19是示出了图2的无线功率传输系统在操作中(当反馈回路正在控制桥式整流器以执行同相串行电压调节以及反相并行电压调节时)的电压的时序图。

31.图20是示出了用于在同相串行电压调节与反相并行电压调节之间执行飞行模式切换的控制器的组件的框图。

32.图21是操作图20的模式切换电路装置以在执行同相串行电压调节和反相并行电压调节之间切换整流调节器的方法的流程图。

33.图22是示出了图2的无线功率传输系统在操作中(当反馈回路正在控制桥式整流器以执行低侧反相并行电压调节时)的电压的时序图。应注意,这里,反馈信号的反馈生成被过滤,因此桥式整流器的晶体管的栅极被伪静态地驱动。

34.图23是示出了图2的无线功率传输系统在操作中(当反馈回路正在控制桥式整流器以执行低侧反相并行电压调节时)的电压的时序图。应注意,这里,反馈信号的反馈生成被过滤,因此桥式整流器的晶体管的栅极被伪静态地驱动。

35.图24是示出了图2的无线功率传输系统在操作中(当反馈回路正在控制桥式整流器以执行低侧同相串行电压调节时)的电压的时序图。应注意,这里,反馈信号的反馈生成被过滤,因此桥式整流器的晶体管的栅极被伪静态地驱动。

36.图25是示出了图2的无线功率传输系统在操作中(当反馈回路正在控制桥式整流器以执行低侧同相串行电压调节时)的电压的时序图。应注意,这里,反馈信号的反馈生成被过滤,因此桥式整流器的晶体管的栅极被伪静态地驱动。

具体实施方式

37.以下公开内容使本领域技术人员能够制造和使用本文中所公开的主题。在不脱离本公开的精神和范围的情况下,本文中所描述的一般原理可以被施加到除以上所详尽的那些实施例和应用之外的实施例和应用。本公开不旨在限于所示的实施例,而要符合与本文中所公开或建议的原理和特征一致的最宽范围。应注意,当下面将晶体管描述为“导通”时,这意味着那些晶体管在线性区域或饱和区域中正在操作,而不是在截止区域中操作。

38.a.硬件描述

39.现在参考图2描述包括发射器21和接收器22的无线功率传输系统20。发射器21包括被耦合到串行谐振反射器线圈lp和电容cp的ac电压源12。接收器22包括被耦合在节点ac1和ac2之间的串行谐振接收器线圈ls和电容cs、以及由耦合在节点n1与接地之间的晶体

管m1至m4形成的“整流调节器”25(当使用下面所描述的技术来控制时也能够电压调节的桥式整流器)。

40.整流调节器由以下形成:n沟道晶体管m1,具有连接到节点n1的漏极、连接到节点ac1的源极、以及被耦合以接收控制信号g1的栅极;n沟道晶体管m4,具有连接到节点ac1的漏极、连接到接地的源极、以及被耦合以接收控制信号g4的栅极;n沟道晶体管m3,具有连接到节点n1的漏极、连接到节点ac2的源极、以及被耦合以接收控制信号g3的栅极;以及n沟道晶体管m2,具有连接到节点ac2的漏极、连接到接地的源极、以及被耦合以接收控制信号g2的栅极。

41.放大器23具有被耦合以接收参考电压vref的反相输入端子(该参考电压vref被设置为等于在节点n1处的所期望的输出电压vrect)、被耦合到节点n1的非反相输入端子、以及被耦合到控制电路装置24并且生成反馈信号fb的输出。负载被连接在节点n1与接地之间,并且由电阻器r1和电容器cl表示。控制电路装置24本身接收来自反馈信号fb的输入,并且基于该输入生成用于晶体管m1至m4的控制信号g1至g4。

42.如下面将详细解释的,控制电路装置24生成控制信号g1至g4,以便使整流调节器25整流接收器线圈ls中感应到的ac电流以产生经整流的输出电压vrect,并且同时适当调制控制信号g1至g4中的一个或多个控制信号以便耗散过量功率,以由此调节输出电压vrect。通过耗散过量功率,由整流调节器25传递到负载的功率可以被控制并且维持在所期望的水平内,而无需使用单独的分立电压调节电路。

43.因此,放大器23和控制电路装置24形成反馈回路。

44.b.使用同相串行电压调节的操作

45.现在描述在由控制电路24控制的同相串行电压调节方案下的无线功率传输系统20的操作。

46.在图3的图形中所示出的是在节点ac1和节点ac2处的信号的波形轨迹。应注意,当ac1处的信号为正时,它被标记为阶段a,当ac2处的信号为正时,它被标记为阶段b,并且ac1和ac2处的信号彼此反相180

°

。

47.在阶段a期间,对应于ac1的正相位和ac2的负相位,生成控制信号ga并且由控制器24将控制信号ga驱动到高电压(足以完全地开启晶体管m1-m2的电平),并且生成控制信号gb并且由控制器24将控制信号gb拉至低电压(完全地关断晶体管m3-m4的电平)。相反,在阶段b期间,由控制器24将控制信号gb驱动到高电压并且由控制器24将控制信号ga拉至低电压。控制器24生成用于晶体管m1至m4的栅极电压g1至g4,并且g1至g4的值取决于控制信号ga和gb的电压值、反馈信号fb的电压、以及电流相位。

48.当由整流调节器25向负载传递的进入功率大于由负载消耗的功率量时,节点n1处的电压vrect上升到大于参考电压vref,使反馈信号fb上升。当反馈信号fb上升时,控制电路装置24从g1至g4中调制适当的栅极电压,以便将相关联的晶体管m1至m4放置到操作的线性区域(欧姆区域)中,并且增加那些晶体管的漏极到源极的电阻,导致过量进入功率在整流调节器25的经激活的晶体管m1至m4内被耗散。该调制在整个操作中持续,结果是电压vrect保持接近于参考电压vref。

49.当栅极电压g1至g4的调制未发生时,栅极电压g1-g2等于控制信号ga的电压。

50.1.晶体管栅极的模拟控制

51.更详细地,如图3所示,栅极电压g1和g2在阶段a期间被调制,使得晶体管m1和m2未被完全导通,增加晶体管m1和m2的漏极到源极的电阻,导致常规操作之上的晶体管m1和m2中的附加的功率耗散;栅极电压g3和g4保持被拉低,使得晶体管m3和m4保持关断。可以在图4中看到晶体管m1至m4的该配置。

52.在阶段b期间,如图3所示,栅极电压g3和g4被调制,使得晶体管m3和m4未完全导通,增加晶体管m3和m4的漏极到源极的电阻,导致常规操作之上的晶体管m3和m4中的附加的功率耗散;栅极电压g1和g2保持被拉低,使得晶体管m1和m2保持关断。可以在图5中看到晶体管m1至m4的该配置。

53.该操作方案被称为同相串行调节,因为在给定的阶段期间通常完全导通的晶体管m1至m4改为电导率调制,因此如图4和图5所示,在该方法期间,通过增加在到负载的主电流路径中串行的元件内的电导率和电压降来实现功率耗散。

54.应注意,在阶段a期间,栅极电压g1和g2的电压电平无需都被调制以增加它们相应的晶体管m1和m2的漏极到源极的电阻,而是仅可以调制栅极电压g1或g2中的一个栅极电压以增加其相应的晶体管m1或m2的漏极到源极的电阻,并且另一个控制信号可以保持高电平以维持其相应的晶体管m1或m2完全导通。

55.类似地,在阶段b期间,栅极电压g3和g4的电压电平无需都被调制以增加它们相应的晶体管m3和m4的漏极到源极的电阻,而是仅可以调制栅极电压g3或g4中的一个栅极电压以增加其相应的晶体管m3或m4的漏极到源极的电阻,并且另一个控制信号可以保持高电平以维持其相应的晶体管m3或m4完全导通。

56.将技术施加到一个或多个元件的选择将被理解/考虑与由系统要耗散的最大的过量功率量相比。

57.作为一次调制一个晶体管m1至m4并且该调制在栅极电压的每个脉冲上不平坦的该操作形式的示例,图9示出了使用同相串行调节来操作的无线功率传输系统20的附加的波形。这里,可以看出在阶段a期间,晶体管m2的栅极电压g2(该栅极电压g2开启晶体管m2)从5.0v的稳定高电压被拉至小于4v,并且晶体管m1的栅极电压g1(该栅极电压g1开启晶体管m1)保持高电平并且晶体管m3的栅极电压g3和晶体管m4的栅极电压g4保持低电平。这里,还可以看出在阶段b期间,晶体管m4的栅极电压g4(该栅极电压g4开启晶体管m4)从5.0v的稳定高电压被拉至小于4v,并且晶体管m3的栅极电压g3(该栅极电压g3开启晶体管g3)保持高电平并且晶体管m1的栅极电压g1和晶体管m2的栅极电压g2保持低电平。

58.应注意,当栅极电压g2和g4从完全高电平被下拉以便调制晶体管m2和m4的导通电阻时,这是针对那些栅极电压的脉冲的大约一半来执行。然而,如果需要通过该布置消耗附加的功率,则栅极电压g2和g4可以针对大于那些栅极电压的脉冲的一半从完全高电平被下拉,以便使晶体管m2和m4的导通电阻调制更长的时间段。这些技术显然适用于两个晶体管一次被调制的情况。

59.以上所描述的同相串行电压调节方案特别适合于通过整流调节器25的电压输出vrect相对低并且要耗散的预期的过量功率相对低的使用情况。

60.应注意,由放大器23和控制电路装置24形成的反馈回路可以以足够的速度来操作,以便它在周期到周期(cycle-to-cycle)的基础上起作用,当执行同相串行电压调节时使控制电路装置24能够在周期到周期的基础上更改栅极电压g1至g4的生成(意味着栅极电

压g1至g4可以在每个周期期间被调整以具有不同的平坦幅度,或者栅极电压g1至g4可以在每个周期期间被即时修改,使得栅极电压g1至g4可以开始具有一个幅度的周期,但是该幅度可以在该周期的部分期间被改变)。这种反馈技术可以在图9的图形中被观察到,其中在每个阶段期间生成反馈信号fb,使控制信号g1至g4能够在周期到周期的基础上被更改。

61.然而,在一些情况中,由放大器23和控制电路装置24形成的反馈回路与由发射器21正在发射的信号的频率相比可以被缓慢地操作。这样,反馈信号fb的生成不是在周期到周期的基础上,反而反馈信号fb的生成被过滤,允许晶体管m1至m4的栅极被伪静态地驱动。当使用反相并行调节来操作时,可以在图22-图23中看到示出该操作模式的波形,并且当使用同相串行调节来操作时,可以在图24-图25中看到示出该操作模式的波形。

62.2.晶体管栅极的pwm控制

63.在上面给出的描述中,晶体管m1至m4的栅极电压g1至g4由控制电路装置24以模拟方式被调制,以执行同相串行电压调节。现在,描述了用于使用脉宽调制(pwm)来调制晶体管m1至m4的栅极电压g1至g4以执行同相串行电压调节的技术。

64.在其中操作来自要被调节的m1至m4中的晶体管的栅极的第一方式涉及简单的开关pwm。这里,放大器被配置作为比较器以提供反馈信号fb作为数字输出,导致脉冲fb,输出电压vrect在脉冲fb期间超过参考电压vref。在该脉冲期间,通过m1至m4的相应的栅极电压被拉到接地,来自m1至m4中的在当前阶段期间完全导通的晶体管响应于fb的上升而被完全地关断,转而增加了功率耗散。因此,通过反馈,驱动晶体管m1至m4的栅极电压g1至g4的持续时间被调节,使得整流调节器25的输出脉冲持续时间刚好足够长以提供所需的功率但刚好足够短以耗散过量功率。

65.与非pwm同相串行电压整流技术相比,该技术的简单示例可以在图12-图13的迹线中看到,其中可以看到,这里的反馈信号fb被数字化,栅极电压g1在阶段a期间被维持为完全高电平,并且栅极电压g2在通过阶段a的大约一半被拉低以增加晶体管m2的漏极到源极的电阻来增加功率耗散。应注意,如所示出的,尖峰可以出现在正被调制的栅极电压g2中,并且这些尖峰可以通过控制电路装置24(诸如,通过使用去抖动功能)被过滤。

66.在图13的示例中,低侧晶体管(m2和m4)的栅极电压g2和g4被调制,而高侧晶体管(m1和m3)的栅极电压g1和g3没有被调制。然而,低侧晶体管和高侧晶体管两者可以被调制。如图14所示,在阶段a期间,为了提供电压调节,栅极电压g1和g2(响应于反馈信号fb上升,可以看出,当vrect超过vref时发生)比它们将另外使用常规的无线功率传输系统更早地被完全关断,将输出电压vrect维持在所期望的电平并且耗散过量功率。类似地,在阶段b期间,为了提供电压调节,栅极电压g3和g4(响应于反馈信号fb上升)比它们将另外使用常规的无线功率传输系统更早地被完全关断,将输出电压vrect维持在所期望的电平并且耗散过量功率。

67.在其中操作来自要被调节的m1至m4中的晶体管的栅极的第二方式涉及修改整流调节器本身以产生经修改的整流调节器25’。从图15中可以看出,整流调节器25’的每个晶体管被分成两个并联耦合的晶体管,该两个并联耦合的晶体管具有彼此不同的w/l比,以便在单独被控制时提供不同的电阻率,其中每个并联耦合对的晶体管的宽度和长度的总和等于整流调节器25的对应的晶体管的宽度和长度,以便提供与完全导通时的整流调节器25的电阻率完全相同的电阻率。因此,整流调节器25包括:并联耦合的n沟道晶体管m1和m1b,其

中它们的漏极被耦合到节点n1,它们的源极被耦合到节点ac1,并且它们的栅极被分别耦合以接收栅极电压g1和g1a;并联耦合的n沟道晶体管m4和m4b,其中它们的漏极被耦合到节点ac1,它们的源极被耦合到接地,并且它们的栅极被分别耦合以接收控制信号m4和m4a;并联耦合的n沟道晶体管m3和m3b,其中它们的漏极被耦合到节点n1,它们的源极被耦合到节点ac2,并且它们的栅极被分别耦合以接收栅极电压g3和g3a;以及并联耦合的n沟道晶体管m2和m2a,其中它们的漏极被耦合到节点ac2,它们的源极被耦合到接地,并且它们的栅极被分别耦合以接收栅极电压g2和g2a。

68.整流调节器25’中的晶体管m1的面积是整流调节器25中的晶体管m1的面积的90%,并且整流调节器25’中的晶体管m1a的面积是整流调节器25中的晶体管m1的面积的10%;整流调节器25’中的晶体管m2的面积是整流调节器25中的晶体管m2的面积的90%,并且整流调节器25’中的晶体管m2a的面积是整流调节器25中的晶体管m2的面积的10%;整流调节器25’中的晶体管m3的面积是整流调节器25中的晶体管m3的面积的90%,并且整流调节器25’中的晶体管m3a的面积是整流调节器25中的晶体管m3的面积的10%;并且整流调节器25’中的晶体管m4的面积是整流调节器25中的晶体管m4的面积的90%,并且整流调节器25’中的晶体管m4的面积是整流调节器25中的晶体管m4的面积的90%,并且整流调节器25’中的晶体管m4a的面积是整流调节器25中的晶体管m4的面积的10%。应注意,上述晶体管m1至m4的相对尺寸可以改变,并且例如,整流调节器25’的晶体管m1至m4可以是整流调节器25的晶体管m1至m4的面积的80%,而整流调节器25’的晶体管m1a-m4a可以是整流调节器25的晶体管m1至m4的面积的20%。

69.与此一起,如图15所示,控制电路装置24’还被修改以除了栅极电压g1至g4之外还输出栅极电压g1a至g4a。

70.利用该经修改的整流调节器25’,如图14和图16所示,在阶段a期间,栅极电压g1a和g2a针对整个阶段是完全高电平,而栅极电压g1和g2针对阶段的第一部分是完全高电平,并且然后针对阶段的过量部分降低。类似地,在阶段b期间,栅极电压g3a和g4a针对整个阶段是完全高电平,而栅极电压g3和g4针对阶段的第一部分是完全高电平,并且然后针对阶段的过量部分降低。使用该技术帮助避免当完全导通的晶体管被关断时可能导致的噪声的诱发,因为当晶体管g1和g2被关断时,晶体管g1a和g2a针对阶段a的过量部分保持导通,并且因为当晶体管g3和g4被关断时,晶体管g3a和g4a针对阶段b的过量部分保持导通。

71.在其中操作来自要被调节的m1至m4中的晶体管的栅极的第三方式涉及在第一预定的恒定驱动电压与第二预定的恒定驱动电压之间切换栅极电压g1至g4。如图14所示,在阶段a期间,栅极电压g1和g2针对阶段的第一部分是完全高电平(第一恒定驱动电压),并且然后针对阶段的过量部分降到第二恒定驱动电压。类似地,在阶段b期间,栅极电压g3和g4针对阶段的第一部分是完全高电平(第一恒定驱动电压),并且然后针对阶段的过量部分降到第二恒定驱动电压。阶段a和b的第一部分可以是那些阶段的总经过时间的大约90%,而阶段a和b的第二部分可以是那些阶段的总经过时间的过量部分。

72.应注意,尽管图14中操作栅极的第一方式可能诱发当晶体管被关断时可以导致的噪声,而第二方式可能在重复的时间流逝期间导致小型器件(10%)中的高电流密度,第三方式具有数字方法简单的益处,因为它仅使用两个驱动电平,而且将如模拟方法,允许器件中的电流密度的最小化。

73.应注意,由放大器23和控制电路装置24形成的反馈回路可以以足够的速度来操作,以便它在周期到周期的基础上起作用,当执行同相串行电压调节时,使控制电路装置24能够在周期到周期的基础上更改栅极电压g1至g4的生成。该反馈技术可以在图9的图形中观察到,其中在每个阶段期间生成反馈信号fb,使栅极电压g1至g4能够在周期到周期的基础上被更改。

74.然而,在一些情况中,由放大器23和控制电路装置24形成的反馈回路与由发射器21正在发射的信号的频率相比可以被缓慢地操作。这样,反馈信号fb的生成不是在周期到周期的基础上,反而反馈信号fb的生成被过滤,允许晶体管m1至m4的栅极被伪静态地驱动。

75.c.使用反相并行电压调节的操作

76.现在描述在由控制电路装置24控制的反相并行电压调节方案下的无线功率传输系统20的操作。

77.图6的图形示出了在节点ac1和ac2处的信号的波形轨迹。应注意,当ac1处的信号为高电平时,它被标记为阶段a,当ac2处的信号为高电平时,它被标记为阶段b,并且ac1和ac2处的信号彼此反相180

°

。

78.在阶段a期间,驱动栅极电压g1和g2,完全地接通晶体管m1和m2,而在阶段b期间,驱动栅极电压g3和g4,而不是完全地接通晶体管m3和m4。通常,来自m1至m4中的在给定的阶段期间未被接通的晶体管被完全地关断。

79.然而,利用反相并行电压调节方案,当由整流调节器25向负载传递的进入功率大于由负载消耗的功率量时,节点n1处的电压vrect上升至大于参考电压vref,使反馈信号fb上升。当反馈信号fb上升时,控制电路装置24调制来自g1至g4中的适当的栅极电压以接通两个晶体管m1和m2、或m3和m4中的一个或多个晶体管,该一个或多个晶体管通常在当前阶段期间被关断,并且将那些晶体管放置在操作的饱和区域中。结果是被附加接通的这些晶体管m1和m2、或m3和m4吸引适度的电流但具有大的漏极到源极的电压,因此诱发足够的功率损耗以消耗过量进入功率。

80.更详细地,如图6所示,在阶段a中,栅极电压g1和g2处于高电平以完全地接通晶体管m1和m2,并且在阶段a期间维持那些晶体管完全导通。然而,这里,尽管在比栅极电压g1和g2更小的电压幅度处,栅极电压g3和g4也被驱动,以由此充分地接通晶体管m3和m4,该晶体管m3和m4具有足以耗散常规操作上的附加功率的漏极到源极的电压和相关联的阻抗。类似地,在阶段b中,栅极电压g3和g4处于高电平以完全地接通晶体管m3和m4,并且在阶段b期间维持那些晶体管完全导通。然而,这里,尽管在比栅极电压g3和g4更小的电压幅度处,栅极电压g1和g2也被驱动,以由此充分地接通晶体管m1和m2,该晶体管m1和m2具有足以耗散常规操作上的附加功率的漏极到源极的电压和相关联的阻抗。

81.该操作方案被称为反相并行调节,因为在给定的阶段期间通常完全导通的晶体管m1至m4保持完全导通,而来自在给定的阶段期间通常关断的m1至m4中的晶体管被足够接通以耗散未由负载消耗的过量功率,并且因为,如图7-图8所示,功率耗散通过增加元件的导电性并且在器件中创建附加的电流路径来实现,当使用所描述的方法来操作时,该附加的电流路径在常规操作中是关断的,并且该附加的电流路径在接通时实际上与主电流路径并行。

82.应注意,在阶段b期间,栅极电压g1和g2不需要都被调制以在线性操作模式中接通

它们相应的晶体管m1和m2,而栅极电压g3和g4保持高电平以维持它们相应的晶体管m3和m4完全地接通,反而栅极电压g1或g2中的仅一个栅极电压可以被调制而另一个栅极电压可以保持关断以维持其相应的晶体管m1或m2完全关断。

83.类似地,在阶段a期间,栅极电压g3和g4不需要都被调制而栅极电压g1和g2保持高电平以维持它们相应的晶体管m1和m2完全接通,反而栅极电压g3或g4中的仅一个栅极电压可以被调制而另一个栅极电压可以保持关断以维持其相应的晶体管m3或m4完全关断。

84.作为其中一个晶体管m1至m4在它通常将被完全关断的阶段期间被调制的该操作形式的示例,图10示出了使用反相并行调节来操作的无线功率传输系统20的附加波形。这里,可以看出,在每个阶段期间生成反馈信号fb,并且在阶段a期间,栅极电压g1和g2是完全高电平以接通晶体管m1和m2,并且栅极电压g4上升到大约1v以接通晶体管m4,该晶体管m4具有足以在常规操作之上耗散附加功率的漏极到源极的电阻。还可以看出,在阶段b期间,栅极电压g3和g4是完全高电平以接通晶体管m3和m4,并且栅极电压g2上升到大约1v以接通晶体管m2,该晶体管m2具有足以在常规操作之上耗散附加功率的漏极到源极的电阻。

85.上述反相并行电压调节方案特别适合于整流调节器25的电压输出vrect不是相对低并且要被耗散的预期的过量功率也不是相对低的使用情况。因此,当使用反相并行电压调节方案来操作时,整流调节器25能够耗散大量过量功率并且将整流调节器25的晶体管维持在它们的安全操作限制内。

86.应注意,由放大器23和控制电路装置24形成的反馈回路可以以足够的速度来操作,以便它在周期到周期的基础上起作用,当执行反相并行电压调节时,使控制电路装置24能够在周期到周期的基础上更改栅极电压g1至g4的生成。该反馈技术可以在图10的图形中观察到,其中在每个阶段期间生成反馈信号fb,使栅极电压g1至g4能够在周期到周期的基础上被更改。

87.然而,在一些情况中,由放大器23和控制电路24形成的反馈回路与由发射器21正在发射的信号的频率相比可以被缓慢地操作。这样,反馈信号fb的生成不是在周期到周期的基础上,反而反馈信号fb的生成被过滤,允许晶体管m1至m4的栅极被伪静态地驱动。

88.d.同相串行电压调节和反向并行电压调节的组合

89.由于上述同相串行电压调节涉及在给定阶段期间调制通常导通的晶体管中的一个或两个晶体管的栅极电压,并且由于上述反相并行电压调节涉及在给定阶段期间调制通常关断的晶体管中的一个或两个晶体管的栅极电压,因此应理解,这两种技术可以被同时利用。因此,可以根据同相串行调节方案来调制整流调节器25的一个或两个晶体管的栅极电压,同时可以根据反相并行调节方案来调制整流调节器25的一个或两个其它晶体管的栅极电压,并且同时整流调节器25的非调制的晶体管按常规被操作。

90.此外,在一些情况中,可以分别使用同相串行电压调节方案和反向并行电压调节方案。例如,可以在一个阶段期间使用同相串行电压调节方案,并且可以在下一个的阶段期间使用反相并行电压调节方案。

91.作为同相串行电压调节和反相并行电压调节的组合的另一个示例,可以针对给定数目的阶段(例如,针对一个阶段a和随后的阶段b)使用同相串行电压调节方案,并且然后可以针对给定数目的阶段(例如,针对下一个阶段a和随后的阶段b)使用反相并行电压调节方案。

92.作为同相串行电压调节和反相并行电压调节的组合的另一个示例,可以在高侧晶体管(晶体管m1和m3)中的一个或两个晶体管上使用同相串行电压调节方案,同时可以在低侧晶体管(晶体管m2和m4)中的一个或两个晶体管上使用反相并行电压调节方案,反之亦然。

93.作为又一示例,同相串行电压调节方案和反相并行电压调节方案中的哪一个方案被使用可以取决于要被耗散的额外功率来切换。当要被耗散的额外功率低于某个阈值时,栅极电压g1至g4可以被生成以便使用同相串行电压调节方案来操作整流调节器25,并且栅极电压g1至g4然后可以切换到正被生成以便使用反相并行电压调节方案来操作整流调节器25。

94.e.控制信号生成和反馈回路

95.现在参考图17和图19描述控制电路装置24。首先,将描述控制信号ga和gb的生成,其后,将描述从栅极电压ga和gb生成用于晶体管m1至m4的栅极电压。

96.控制电路装置24包括迟滞比较器51,迟滞比较器51具有耦合到节点ac1的非反相端子、耦合到接地的反相端子、以及产生ga的输出。

97.控制电路装置24包括迟滞比较器54,迟滞比较器54具有耦合到节点ac2的非反相端子、耦合到接地的反向端子、以及产生gb的输出。

98.参考图17a,当生成控制电压ga和gb时,控制电路装置24的操作因此是:当节点ac1处的ac信号上升到变得大于迟滞比较器51的第一阈值(在该示例中为0mv)时(参考图17c),比较器51的输出ga被拉低。类似地,当节点ac2处的ac信号下降(发生在节点ac1处的ac信号上升时)并且小于迟滞比较器54的第二阈值(在该示例中为-200mv)时(参考图17d),比较器54的输出gb被拉高。

99.相反地,当节点ac1处的ac信号下降并且结果小于迟滞比较器51的第二阈值时,比较器51的输出ga被拉高。类似地,当节点ac2处的ac信号上升到变得大于迟滞比较器54的第一阈值时,比较器54的输出被拉低。

100.现在参考图18a至图19,针对不使用晶体管栅极的pwm控制的情况描述控制电路装置24的过量部分。

101.应注意,作为针对低侧驱动技术的一般实践,用于驱动m2和m4的栅极的信号被缓冲。此外,应注意,作为针对高侧驱动技术的一般实践,用于驱动栅极m1和m3的信号被电平移位和缓冲。为简化起见,以下描述将假设ga、gb和源自ga、gb、fb的任何复合信号被直接耦合到栅极,并且在实际实现中,缓冲器和电平移位技术将与以上所提及的用于低侧和高侧驱动技术的技术保持一致来使用。

102.当开关m0闭合时,指示整流调节器25作为标准整流器来操作,控制信号ga被耦合到晶体管m1和m2的栅极作为栅极电压g1和g2,而与阶段无关,并且控制信号gb被耦合到晶体管m3和m4的栅极作为栅极电压g3和g4,而与阶段无关。因此,在阶段a期间,晶体管m1和m2被完全地接通而晶体管m3和m4被完全地关断,并且在阶段b期间,晶体管m3和m4被完全地接通而晶体管m3和m4被完全地关断。

103.当开关m1闭合时,指示整流调节器25操作以便执行同相串行电压调节,在阶段a中:从控制信号ga减去反馈电压fb,并且结果被耦合到晶体管m1的栅极作为栅极电压g1;从控制信号ga减去反馈电压fb,并且结果被耦合到晶体管m2的栅极作为栅极电压g2;控制信

号gb被耦合到晶体管m3的栅极作为栅极电压g3;以及控制信号gb被耦合到晶体管m4的栅极作为栅极电压g4。在阶段b中:从控制信号gb减去反馈电压fb,并且结果然后被耦合到晶体管m3的栅极作为栅极电压g3;从控制信号gb减去反馈电压fb,并且结果然后被耦合到晶体管m4的栅极作为栅极电压g4;控制信号ga被耦合到晶体管m1的栅极作为栅极电压g1;以及控制信号ga被耦合到晶体管m2的栅极作为栅极电压g2。因此,在阶段a期间,晶体管m3和m4被完全关断,同时晶体管m1和m2的栅极电压通过反馈电压fb被降低,以由此增加晶体管m1和m2的漏极到源极的电阻到足以耗散过量功率。类似地,在阶段b期间,晶体管m1和m2被完全关断,同时晶体管m3和m4的栅极电压通过反馈电压fb被降低,以由此增加晶体管m3和m4的漏极到源极的电阻到足以耗散过量功率。

104.当开关m2闭合时,指示整流调节器25操作以便执行反相并行电压调节,在阶段a中:电压fb被加到控制信号gb,并且结果然后被耦合到晶体管m3的栅极作为栅极电压g3;电压fb被加到控制信号gb,并且结果然后被耦合到晶体管m4的栅极作为栅极电压g4;控制信号ga被耦合到晶体管m1的栅极作为栅极电压g1;并且控制信号ga被耦合到晶体管t2的栅极作为栅极电压g2。在阶段b中:电压fb被加到控制信号ga,并且结果被耦合到晶体管m1的栅极作为栅极电压g1;电压fb被加到控制信号ga,并且结果被耦合到晶体管m2的栅极作为栅极电压g2;控制信号gb被耦合到晶体管m3的栅极作为栅极电压g3;并且控制信号gb被耦合到晶体管m4的栅极作为栅极电压g4。因此,在阶段a期间,晶体管m1和m2被完全导通,同时晶体管m3和m4的栅极被充分地驱动引起通过晶体管m3和m4的过量功率的耗散但不足以阻止整流。类似地,在阶段b期间,晶体管m3和m4被完全导通,同时晶体管m1和m2的栅极被充分地驱动引起通过晶体管m3和m4的过量功率的耗散但不足以阻止整流。

105.现在参考图18b和图18c,控制电路装置24的过量部分被描述用于晶体管栅极的pwm控制依据图14中的操作栅极的第一方式和第二方式被使用的情况。依据图18a的反馈信号fb已经被分成两部分,其中fba是反馈放大器23的输出(在图2中命名为fb),并且fbd是由比较器23’提供的数字化反馈的输出,并且相应地生成信号到依据图12的时序图。在操作期间,fbd可以采用两个电平,标记为fbd_h和fbd_l。现在假设ga、gb的驱动强度为vdd,信号ga-fbd(相应地gb-fbd)将提供两个电平vdd-vgh和vdd-vgl。因此,在使用vgh=vdd和vgl=0的情况中,信号ga-fbd(相应地gb-fbd)将提供驱动强度的两个电平,0和vdd,以便根据操作图14上的栅极的第一方式来驱动。

106.现在,在使用vgh=vdd-v1和vgh=0的情况中,信号ga-fbd(相应地gb-fbd)将提供驱动强度的两个电平,v1和vdd,以便根据操作图14上的栅极的第三方式来驱动。

107.应注意,当整流调节器25’处于由m1控制的串行模式,或处于由m2控制的并行模式时,并且如果fb信号(相应地fba和fbd)被选通为零,则整流调节器25’表现恰好类似于由m0控制的常规模式中的调节器25’,因为当fba和fbd被选通为零时,ga+fbd、gb+fbd、ga-fba、gb-fba等于ga、gb,这可以发生在例如当vrect远低于目标时。

108.本领域技术人员将从图15中理解如何概括图18b用于支持操作栅极的第三方式。

109.现在描述用于在使用pwm的同相串行电压调节和反相并行电压调节之间自动切换整流调节器25’的硬件和技术。

110.现在参考图20,图示了被包括在控制器24内的硬件,用于在使用pwm的同相串行电压调节和反相并行电压调节之间自动切换整流调节器25’。串行监测电路50包括占空比确

定电路,该占空比确定电路在pwm同相串行电压调节的执行期间利用计数器来确定控制信号ga和gb的占空比(由此确定栅极电压g1至g4),并且因此整流调节器25’的输出的占空比通过对控制信号ga和gb的每个脉冲内的高频计数器时钟hfclk的脉冲的数目进行计数、通过对控制信号ga’和gb’的每个脉冲内的高频计数器时钟的脉冲的数目进行计数(由此确定栅极电压g1a至g4a)、并且将控制信号ga和gb的每个脉冲内的高频时钟hfclk的脉冲的数目除以控制信号ga’和gb’的每个脉冲内的高频时钟的脉冲的数目。占空比在下文中将被称为duty_ser_sh:例如,如果发现整流调节器器25’的占空比为90%,则duty_ser_sh将为90%。串行监测电路50还包括数字比较器52,该数字比较器52将duty_ser_sh的每次出现与建立的占空比限制duty_ser_limit进行比较,并且当duty_ser_sh的当前出现大于duty_ser_limit时锁存器然后断言duty_ser_limit_latch_b信号。当duty_ser_sh的当前出现小于占空比限制duty_ser_limit时,数字比较器52取消断言duty_ser_limit_latch_b信号。应注意,在反相并行模式期间,duty_ser_limit_latch_b信号始终被断言为高电平。

111.控制器24还包括并行监测电路60,该并行监测电路60包括n沟道晶体管m5,n沟道晶体管m5是整流调节器25’中的晶体管中的一个晶体管的副本(说明性地为g1或g2的副本),该副本在其栅极处接收对应的栅极电压g1或g2,具有被耦合到节点ac1的其源极,并且具有被耦合到第一电流镜61的其漏极。第一电流镜61在反相并行电压调节期间将流过副本晶体管m5的电流ipar镜像到第二电流镜62,该第二电流镜62转而将电流镜像到放大器63的反相端子,该放大器63被配置为作为(在晶体管m5是晶体管m1或m3的副本的情况下)iinhs或(在晶体管m5是晶体管m2或m4的副本的情况下)iinls的积分器。应注意,电流镜61可以有利地从vrect节点被供应,并且电流镜的功率消耗并不重要,因为在任何情况下它作为消耗输入功率的过量的总体目标的部分起作用。如此,应理解,比率k1不需要非常高并且镜的好的匹配性能是可行的。积分器63的反相端子被耦合到接地,并且电容器c和重置开关被并联耦合在积分器63的输出和反相端子之间。积分器63输出是int_charge_par信号,该int_charge_par信号通过可锁存比较器64与限制电流ipar_limit进行比较,并且结果由比较器64锁存,其后由反相器65反相以产生ipar_limit_latch_b信号。应注意,ipar_limit_latch_b信号在设计上在同相串行模式期间始终被断言为高电平,因为在反相并行调节hw中没有电流流动。

112.模式切换控制电路装置80包括与门81,该与门81接收duty_ser_limit_latch_b信号和ipar_limit_latch_b信号,执行逻辑与运算,并且产生信号103作为输出。鉴于duty_ser_limit_latch_b信号在反相并行模式期间始终被断言为高电平,并且信号ipar_limit_latch_b在设计上在同相串行模式期间也始终被断言为高电平,与门81确实始终具有处于逻辑一的其两个输入中的一个输入。因此,与门81是两种模式之间自动切换的入口点。

113.与门82接收信号104和初始化信号reset_init作为输入,执行逻辑与运算,并且产生ulp_auto_pre信号作为输出。或门84接收来自与门82的ulp_auto_pre信号作为输入,并且接收来自不可再触发的单稳态83的ulp_auto_0_latch信号作为输入,执行逻辑或运算,并且产生ulp_auto_0信号作为输出。单稳态83接收ulp_auto_0信号作为输入并且产生ulp_auto_0_latch信号作为输出。

114.比较器86在其非反相端子处接收输出电压vrect并且在其反相端子处接收参考电压vref+200mv,并且产生vgate_over信号作为输出。与门87接收vgate_over信号和ulp_

auto_0信号作为输入,执行逻辑与运算,并且生成信号101作为输出,其转而由反相器88反相以产生ulp_auto_en信号作为输出。与门85接收ulp_auto_0信号和ulp_auto_en信号作为输入,执行逻辑与运算,并且生成ulp_auto_1信号作为输出。与门89接收来自与门85的ulp_auto_1信号作为输入、以及作为反相器栅极92的输出的信号110,该反相器栅极92从不可再触发的单稳态91的输出111接收其输入。与门89执行逻辑与运算,以产生ulp_auto信号作为输出,该ulp_auto信号由反相器90反相并且被传到单稳态91的输入。

115.不可再触发的单稳态83和91接收初始化信号reset_init,当期望将单稳态83和91重置为可被再次可触发一次时,该初始化信号reset_init被断言。

116.如将被说明的,当ulp_auto信号为逻辑一时,控制器24生成晶体管m1至m4和m1a至m4a的栅极电压g1至g4和g1a至g4a,以使整流调节器25’执行同相串行电压调节,并且当ulp_auto信号为逻辑零时,控制器24生成晶体管m1至m4和m1a至m4a的栅极电压g1至g4和g1a至g4a,以使整流调节器25’执行反相并行电压调节。

117.现在将附加参考图21来描述模式切换控制电路装置80的操作。

118.在上电和/或重置处,reset_init信号被设置为逻辑零,通过闭合其开关来重置单稳态83和91以及积分器63(框201)。结果,与门82输出ulp_auto_pre信号作为逻辑零并且单稳态83输出ulp_auto_0_latch作为逻辑零,导致或门84输出ulp_auto_0信号作为逻辑零。由于ulp_auto_0信号为逻辑零,与门85将输出ulp_auto_1信号作为逻辑零,并且转而与门89将输出ulp_auto信号作为逻辑零。应注意,此时输入110没有影响,因为ulp_auto_1是逻辑0。然而,如果ulp_auto_1刚刚从逻辑一转变为逻辑零,则输入110会将ulp_auto保持到逻辑0一段时间。

119.接下来,为了退出重置,reset_init信号被设置为逻辑一(框202)。此时,功率输送尚未开始,因此控制信号ga、gb、ga’和gb’为零。控制信号ga、gb、ga’和gb’为零的结果是栅极电压g1至g4和g1a至g4a被生成为零。

120.g1至g4、g1a至g4b为零的结果是:整流调节器25’在异步模式中作为常规的4二极管整流器来操作,并且vrect在进入功率的影响下自由上升,其转而供应控制器24’,转而生成信号g1至g4,g1a至g4b。

121.此时,因为vrect电压仍然为低并且低于目标,所以整流调节器25’如先前强调的常规整流器一样操作,并且作为第一结果,duty_ser_sh信号为高并且比较器52输出duty_ser_limit_latch_b信号作为逻辑一。

122.作为依据常规整流器操作的整流调节器25’的第二效果,电流ipar和iinhs/iinls为零,因为没有发生反相传导,其中结果是放大器63将int_charge_par信号输出为零。作为int_charge_par信号为零的结果,ipar_limit大于int_charge_par,并且比较器64将锁存并且输出逻辑零,该逻辑零由反相器65反相以产生逻辑一处的ipar_limit_latch_b信号。

123.由于duty_ser_limit_latch和ipar_limit_latch_b都处于逻辑一,所以由与门81输出的信号103为逻辑一,并且由于reset_init信号处于逻辑一,所以由与门82输出的ulp_auto_pre信号为逻辑一。作为ulp_auto_pre信号为逻辑一的结果,由或门84输出ulp_auto_0信号作为逻辑一,转而使ulp_auto_0_latch信号上升到逻辑一,转而触发单稳态83,转而将逻辑一施加到ulp_auto_0_latch,ulp_auto_0_latch在单稳态83脉冲的持续时间期间保持逻辑一,这保证了在由单稳态83生成的脉冲的持续时间期间ulp_auto_0上的逻辑一。因

此,每次ulp_auto_0从逻辑零转换为逻辑一时,系统能够在由单稳态脉冲持续时间设置的最小持续时间期间将ulp_auto_0逻辑自锁为逻辑一。

124.由于输出电压vrect将低于vref,因此参考电压vref+200mv大于vrect,导致由比较器86输出的vgate_over信号为逻辑零,并且转而,由与门87输出的信号101为逻辑零并且由反相器88反相以产生ulp_auto_en信号作为逻辑一。换句话说,vgate_over信号在该阶段期间没有任何影响。功能的相关性将被进一步解释。

125.注意,由于ulp_auto在重置期间被产生作为逻辑零,因此反相器90输出逻辑一,使单稳态91在其输出处产生逻辑一作为信号110。由于ulp_auto_0为逻辑一并且由于ulp_auto_en信号为逻辑一,所以由与门85输出的ulp_auto_1信号被产生作为逻辑一。由于ulp_auto_1信号为逻辑一并且由于信号110为逻辑一,所以此时ulp_auto信号将由与门89输出作为逻辑一。

126.处于逻辑一的ulp_auto信号使控制器23生成ga、gb、ga’和gb’,从而在对次级线圈ls中感应的电流进行整流的常规操作之上,它执行同相串行调节(框203)。最初,输出电压vrect将显著小于vref,因此比较器23将不断言反馈信号fb。

127.操作以这种开环方式继续,而输出电压vrect保持小于参考电压vref(框204)。随着操作继续,输出电压vrect将上升。一旦输出电压vrect变得高于或等于参考电压vref(框204),反馈信号fb由比较器23断言,并且闭环串行同相调节开始(框205)。此时,使用pwm的闭环串行同相调节继续,如上文详细描述的,并且继续直到duty_ser_limit_latch_b信号被拉至逻辑低(框206)。这在整流调节器25’的占空比duty_ser_sh下降到10%以下(意味着duty_ser_sh信号下降到10%以下以变得小于duty_ser_limit,该duty_ser_limit被设置为10%,导致比较器52输出duty_ser_limit_latch_b作为逻辑零)时发生。

128.duty_ser_limit_latch_b被输出作为逻辑零,转而使由与门81输出的信号103变为逻辑零,使由与门82输出的ulp_auto_pre变为逻辑零,导致或门84输出ulp_auto_0信号作为逻辑零(因为ulp_auto_0为逻辑零),转而导致由与门85输出ulp_auto_1作为逻辑零,并且因此由与门89输出ulp_auto信号作为逻辑零。

129.输出作为逻辑零的ulp_auto信号使控制器23生成ga、gb、ga’和gb’,以便在执行反相并行调节时对次级线圈ls中感应的电流进行整流(框207)。

130.应注意,ulp_auto从逻辑一到逻辑零的转变在由反相器90反相之后确实触发了单稳态91,单稳态91的输出一旦由反相器栅极92反相,则在输入110上得到逻辑零并且确保在不可再触发的单稳态91的持续时间期间维持与门89上的逻辑零。

131.因此,直到从反相并行调节开始所经过的时间变得大于最小时间(框208),反相并行调节继续。如果所经过的时间变得大于最小时间(框208),但是ipar_limit_latch_b信号和duty_ser_limit_latch_b信号不都是逻辑一,则ulp_auto继续被输出作为逻辑零,并且反相并行调节继续。然而,如果ipar_limit_latch_b信号和duty_ser_limit_latch_b信号两者都变得等于逻辑一(框209),则控制器23再次生成ga、gb、ga’和gb’,以便当执行同相串行调节时对在次级线圈ls中感应的电流进行整流(框210)。

132.系统维持在串行同相调节直到所经过的时间变得大于最小时间(框211)。一旦发生这种情况,则系统继续检查ipar_limit_latch_b信号和duty_ser_limit_latch_b信号两者是否都处于逻辑一,并且如果这两个条件仍然为真,则继续进行同相串行调节。

133.然而,如果在时间尚未过去同时输出超过参考电压加上容差(在示例框212中在200mv处被设置),信号101上升到逻辑一并且ulp_auto_en下降到零,则控制器23返回到生成控制信号g1至g4和g1a至g4a,以便使整流调节器25’的晶体管m1至m4和m1a至m4a执行反相并行调节。因此,系统还具有在vrect过高的情况下自退出具有最高优先级的同相串行回路的能力,这有助于保证如果系统进入同相串行调节的时间少于所经过的时间,但是由于重合进入功率变得过高,系统仍然能够退出同相串行模式并且进入反相并行模式。

134.这样,整流器24’即时在同相串行电压调节和反相并行电压调节之间进行切换,其中同相串行电压调节从上电/重置被使用并且直到闭环同相串行调节使整流调节器24’以小于10%的占空比(由下降到duty_ser_limit信号以下的duty_ser_sh信号指示)来操作,此时使用反相并行电压调节。持续直到反相并行电压调节已使用了给定的时间段以及直到反相并行电流下降到电流阈值以下(在并行调节期间默认断言占空比限制检测duty_ser_limit_latch_b),此时返回到串行调节。然后,如果针对给定的时间段尚未使用串行调节,但输出电压vrect变得大于参考电压vref+200mv,则返回到并行电压调节。否则,串行调节保持并且循环,直到占空比下降太低。

135.因此,总而言之,使用同相串行电压调节直到整流调节器25’的占空比下降到10%以下,这意味着整流调节器25’的功率耗散能力的90%正在被利用。此时,反相并行电压调节被用于其附加的功率耗散能力。假使在给定的时间窗口期间经调节的电压变得太高,并行电压调节具有停止串行调节的能力,并且使用反相电压调节直到它吸引的电流下降到经定义的限制以下。这有利地允许在给定当前操作条件的情况下使用适当的电压调节方案。

136.g.优势

137.同相串行电压调节方案和反相并行电压调节方案具有多种优势,包括:通过消除单独的分立电压调节器(包括功率晶体管和槽路电容器)(诸如,低压差放大器)所提供的显著的面积节省,以及当无线功率传输系统20在均衡时操作的功率节省。此外,这些方案在四个器件(晶体管m1至m4)之上分散过量功率消耗,而不是所有过量功率消耗都由附加的电压调节器内的单个功率晶体管吸收。更进一步,这些方案允许容易地将接收器22用作发射器,因为可以直接访问节点n1(在该节点n1处产生电压vrect)。

138.现有技术的无线功率传输系统与无线功率传输系统20之间的效率差异如下表所示:

[0139][0140]

在其它优势中,应注意系统效率提高了近3%。

[0141]

提供的另一个优势是,当无线功率传输系统20的操作包括数据通信以及功率传输时,诸如当数据传输从接收器22到发射器21传输时通过使用幅移键控(ask),由发射器21接收的数据符号(ask符号)更干净。这可以在图11中看出,其中由使用现有技术的无线功率传输系统20的发射器21接收的信号(被标记为vcoil ldo primary)在其脉冲中包含减小的幅度峰值,但是其中由发射器21接收的信号(被标记为vcoil_3regtifier)使用无线数据传输系统20在其脉冲中包含平坦的幅度峰值,这使得初级侧处的符号提取变得容易。

[0142]

此外,当使用现有技术的功率传输系统执行ask数据传输时,调制深度根据进入功率和输出电压vrect的幅度而变化,因为分立电压调节器的功率晶体管的漏极到源极的电阻将根据进入功率和输出电压vrect的幅度而变化很大。然而,当使用本文中所描述的无线数据传输系统20时,整流调节器的四个晶体管m1至m4的漏极到源极的电阻变化远小于分立电压调节器的单个功率晶体管的漏极到源极的电阻,维持调制深度在一般恒定的水平。

[0143]

虽然已经关于有限数目的实施例描述了本公开,但是受益于本公开的本领域技术人员将理解,可以设想不脱离本文公开的本公开的范围的其它实施例。因此,本公开的范围应仅由所附权利要求限制。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1