同步整流控制器及其控制方法与流程

1.本发明涉及一种同步整流控制器及其控制方法,尤其涉及一种可比较参考电压及整流开关的通道电压,且据以调整整流开关的控制端的电压的同步整流控制器及其控制方法。

背景技术:

2.在电力转换驱动控制器,例如反激式(flyback)电路的架构中,可使用二极管作为整流组件,例如可使用肖特基二极管,因其正向导通压降较低。然而,若以二极管上的跨压为0.5伏特、跨电流的均方根值为10安培为例,根据功率损耗等于电流与跨压的乘积的计算式,将产生约5瓦特的功率损耗。

3.为了降低此功率损耗,可采用晶体管取代二极管。举例而言,可用金氧半场效晶体管(mosfet)的两端(例如漏极及源极)取代二极管的阳极与阴极,从而以晶体管置换二极管。经置换后,假设晶体管导通时的阻抗为10毫欧姆(mω),跨电流仍为10安培,根据功率损耗等于电流的平方与阻抗的乘积的计算式,将产生1瓦特的功率损耗。上述的数值仅为举例,在此例中,由于功率损耗由5瓦特降至1瓦特,可知使用晶体管取代二极管作为电力转换驱动控制器的整流组件,应有降低功率损耗的功效。

4.上述使用晶体管形成的整流组件可设置于二次侧,若该晶体管持续保持完全导通,当二次侧电流下降于较小时,晶体管上导通电压很小,所以很难判断二次侧的整流组件关闭的时点,易于导致整流组件过早关闭,而降低运作效能。

技术实现要素:

5.实施例提供一同步整流控制器,用以控制一整流开关,该整流开关具有一控制端,且该同步整流控制器包括一稳压器。该稳压器具有一输出端,该输出端提供一控制电压至该整流开关的该控制端。该稳压器包括一比较器、一反相器、一上拉电源及一下拉电源。该比较器用以接收该整流开关的一通道电压,比较该通道电压与一参考电压而输出一比较结果信号,当该通道电压大于该参考电压时,该比较结果信号具有一第一逻辑值,当该通道电压小于该参考电压时,该比较结果信号具有一第二逻辑值,该第一逻辑值异于该第二逻辑值。该反相器用以接收该比较结果信号,及产生一反相比较结果信号,其中该比较结果信号及该反相比较结果信号为互补。该上拉电源耦接于该稳压器的该输出端,由该反相比较结果信号所致能,用以当该通道电压小于该参考电压时,该上拉电源被致能以上拉该控制电压。该下拉电源耦接于该稳压器的该输出端,由该比较结果信号所致能,用以当该通道电压大于该参考电压时,该下拉电源被致能以下拉该控制电压。其中,该上拉电源及该下拉电源分别被该比较结果信号及该反相比较结果信号所致能,故该上拉电源及该下拉电源不会同时被致能。

6.实施例提供一种同步整流控制器,用以控制一整流开关,且该整流开关具有一控制端。该同步整流控制器包括一稳压器。一稳压器,具有一输出端,该输出端提供一控制电

压至该整流开关的该控制端,该稳压器包括一第一比较器、一第一反相器、一波形斜率检测电路、一第二反相器、一主上拉电源、一主下拉电源、一辅助上拉电源及一辅助下拉电源。该第一比较器接收该整流开关的一通道电压,及比较该通道电压与一参考电压而输出一比较结果信号,当该通道电压大于该参考电压时,该比较结果信号具有一第一逻辑值,当该通道电压小于该参考电压时,该比较结果信号具有一第二逻辑值。该第一反相器,用以接收该比较结果信号,及产生一反相比较结果信号,使得该比较结果信号及该反相比较结果信号为互补。该波形斜率检测电路接收该整流开关的该通道电压,而输出一波形斜率信号,当该通道电压的波形为上升时,该波形斜率信号具有一第三逻辑值,当该通道电压的波形为下降时,该波形斜率信号具有一第四逻辑值。该第二反相器用以接收该波形斜率信号,及产生一反相波形斜率信号,使得该波形斜率信号及该反相波形斜率为互补。该主上拉电源耦接于该输出端,由该比较结果信号与该反相比较结果信号中的一个所致能,用以上拉该控制电压。该主下拉电源耦接于该输出端,由该比较结果信号与该反相比较结果信号中的另一个所致能,用以下拉该控制电压。该辅助上拉电源耦接于该输出端,由该波形斜率信号与该反相波形斜率信号中的一个所致能,使得该辅助上拉电源选择性地与该主上拉电源共同上拉该控制电压。该辅助下拉电源耦接于该输出端,由该波形斜率信号与该反相波形斜率信号中的另一个所致能,使得该辅助下拉电源选择性地与该主下拉电源共同下拉该控制电压。

7.实施例提供一种同步整流控制器的控制方法。该同步整流控制器包括一稳压器,该稳压器提供一控制电压,该控制电压提供至一整流开关的一控制端以控制该整流开关,该控制方法包括比较该整流开关的一通道电压及一参考电压,以产生一比较结果信号,其中当该通道电压大于该参考电压,则该比较结果信号具有一第一逻辑值,当该通道电压小于该参考电压,则该比较结果信号具有一第二逻辑值,且该第一逻辑值异于该第二逻辑值;根据该比较结果信号产生一反相比较结果信号,其中该比较结果信号及该反相比较结果信号为互补;当该通道电压小于该参考电压时,由该反相比较结果信号致能一上拉电源以上拉该控制电压;及当该通道电压大于该参考电压时,由该比较结果信号致能一下拉电源以下拉该控制电压。

8.实施例提供一种同步整流控制器的控制方法。该同步整流控制器包括一稳压器,该稳压器通过一输出端提供一控制电压,该控制电压提供至一整流开关的一控制端以控制该整流开关,该控制方法包括比较该整流开关的一通道电压与一参考电压而输出一比较结果信号,其中当该通道电压大于该参考电压时,该比较结果信号具有一第一逻辑值,当该通道电压小于该参考电压时,该比较结果信号具有一第二逻辑值;根据该比较结果信号产生一反相比较结果信号,使得该比较结果信号及该反相比较结果信号为互补;接收该整流开关的该通道电压,而输出一波形斜率信号,其中当该通道电压的波形为上升时,该波形斜率信号具有一第三逻辑值,当该通道电压的波形为下降时,该波形斜率信号具有一第四逻辑值;根据该波形斜率信号产生一反相波形斜率信号,使得该波形斜率信号及该反相波形斜率信号为互补;该比较结果信号与该反相比较结果信号中的一个用以选择性地致能一主上拉电源以上拉该控制电压,且该比较结果信号与该反相比较结果信号中的另一个用以选择性地致能一主下拉电源以下拉该控制电压;及该波形斜率信号与该反相波形斜率信号中的一个用以选择性地致能一辅助上拉电源以与该主上拉电源共同上拉该控制电压,且该波形斜率信号与该反相波形斜率信号中的另一个用以选择性地致能一辅助下拉电源以与该主

下拉电源共同下拉该控制电压。

附图说明

9.图1为实施例中,同步整流控制器设置于电压变换器的示意图。

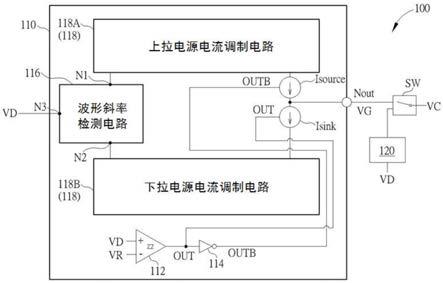

10.图2为实施例中,同步整流控制器的示意图。

11.图3为实施例中,图1及图2的同步整流控制器的示意图。

12.图4为图3的电压及电流的波形图。

13.图5为另一实施例中,图1的同步整流控制器的示意图。

14.图6为图5的信号的波形图。

15.图7为图2及图3的同步整流控制器的控制方法的流程图。

16.图8为图5的同步整流控制器的控制方法的流程图。

17.附图标记:

18.10:电压变换器

19.100:同步整流控制器

20.110:稳压器

21.112,510:比较器

22.114,520,540:反相器

23.116,530:波形斜率检测电路

24.118:电源电流调制电路

25.118a:上拉电源电流调制电路

26.118b:下拉电源电流调制电路

27.120:全开控制器

28.550,560:与门

29.61,62,63,64:箭头

30.700,800:控制方法

31.a,b,c,d,e:阶段

32.b1,b2:电流源

33.c:电容

34.i51:主上拉电源

35.i52:主下拉电源

36.i53:辅助上拉电源

37.i54:辅助下拉电源

38.ia,ib,ip3,in3,ih,il,ig:电流

39.ib1,ib2:参考电流

40.isd:电流

41.isink:下拉电源

42.isource:上拉电源

43.n:节点

44.n1,n2,n3:端

45.nout:输出端

46.out,vsink:比较结果信号

47.outb,vsource:反相比较结果信号

48.r1,r2:电阻

49.s1:一次侧

50.s2:二次侧

51.s710至s780,s810至s880:步骤

52.sw:多任务器

53.swr:整流开关

54.t1,t2,t3,t4,t5,t6,t7,t8:晶体管

55.td:延迟时段

56.vc,vout:电压

57.vd:通道电压

58.vdd,vss:参考电压端

59.vf:全开电压

60.vg:控制电压

61.vin:电压位准

62.vr,v1:参考电压

63.vsink2,vsource2:信号

64.vslope:波形斜率信号

65.vslope':反相波形斜率信号

66.sw

source

,sw

sink

:开关

具体实施方式

67.图1为实施例中,同步整流控制器100设置于电压变换器10的示意图。如图1所示,电压变换器10可包括一次侧s1及二次侧s2,同步整流控制器100可用以控制位于二次侧s2的整流开关swr。如图1所示,同步整流控制器100可提供电压vc至整流开关swr的控制端,以控制整流开关swr的导通或截止的程度。图1中,电流isd可为从整流开关swr的源极流到漏极的电流,电压vout可为电压变换器10转换后于二次侧s2输出的电压。

68.图2为实施例中,同步整流控制器100的示意图。同步整流控制器100包括稳压器(regulator)110。稳压器110具有输出端nout,输出端nout可提供控制电压vg,控制电压vg可选择性地成为电压vc而耦接至整流开关swr的控制端。稳压器110包括比较器112、反相器114、上拉电源isource及下拉电源isink。

69.比较器112可用以接收整流开关swr的通道电压vd,比较通道电压vd与参考电压vr而输出比较结果信号sout。当通道电压vd大于参考电压vr时,比较结果信号out具有第一逻辑值(例如,1);当通道电压vd小于参考电压vr时,比较结果信号out具有第二逻辑值(例如,0),第一逻辑值异于第二逻辑值。

70.反相器114可用以接收比较结果信号out,及据以产生反相比较结果信号outb,其中比较结果信号out及反相比较结果信号outb为互补。

71.上拉电源isource可耦接于稳压器110的输出端nout,由反相比较结果信号outb所致能。当通道电压vd小于参考电压vr时,上拉电源isource可被致能以上拉控制电压vg。

72.下拉电源isink耦接于稳压器110的输出端nout,由比较结果信号out所致能。当通道电压vd大于参考电压vr时,下拉电源isink被致能以下拉控制电压vg。

73.由于上拉电源isource及下拉电源isink分别被反相比较结果信号outb及比较结果信号out所致能,故上拉电源isource及下拉电源isink不会同时被致能。

74.根据实施例,比较器112的操作可具有延迟时段td。图2的比较器112可比较通道电压vd与参考电压vr,且延迟延迟时段td后而输出比较结果信号out。当通道电压vd小于参考电压vr且延迟延迟时段td后,上拉电源isource被致能以上拉控制电压vg。当通道电压vd大于参考电压vr且延迟延迟时段td后,下拉电源isink被致能以下拉控制电压vg。关于延迟时段td,述于后文的波形图。

75.举例而言,若图1的整流开关swr由金氧半晶体管形成,则通道电压vd可为整流开关swr的金氧半晶体管的漏极电压,且电压vc可为整流开关swr的金氧半晶体管的栅极电压。

76.如图2所示,同步整流控制器100可还包括全开控制器(fully

‑

oncontroller)120及多任务器sw。全开控制器120可接收整流开关swr的通道电压vd,当该通道电压vd满足默认条件时,例如:当通道电压vd低于默认开启电压阀值时,全开控制器120可使多任务器sw将全开电压vf耦接至整流开关swr的控制端,以使整流开关swr处于完全导通的全开模式。相对地,当多任务器sw将稳压器110提供的控制电压vg耦接至整流开关swr控制端时,会使整流开关swr处于部分导通的稳压模式。如此多任务器sw可用以切换整流开关swr的控制端接收全开电压vf及稳压器110提供的控制电压vg中的一个;换言之,多任务器sw可用以切换电压vc为全开电压vf及控制电压vg中的一个。

77.如图2所示,同步整流控制器100的稳压器110可还包括波形斜率检测电路116及电源电流调制电路118(包括上拉电源电流调制电路118a与下拉电源电流调制电路118b)。波形斜率检测电路116可接收整流开关swr的通道电压vd,获得通道电压vd的波形变化斜率值。电源电流调制电路118由通道电压vd的波形变化斜率值所控制,当波形变化斜率值较小时,会使上拉电源isource及下拉电源isink各自输出第一电流到输出端nout;当波形变化斜率值较大时,使上拉电源isource及下拉电源isink两者各自输出第二电流到该输出端nout,其中第一电流大于第二电流。

78.图3为实施例中,图1及图2的同步整流控制器100的示意图。图3包括较多细节。图4为图3的电压及电流的波形图。

79.如图3所示,波形斜率检测电路116可包括第一电阻r1、第二电阻r2及电容c。第一电阻r1可耦接于波形斜率检测电路116的第一端n1及节点n之间。第二电阻r2可耦接于波形斜率检测电路116的第二端n2及节点n之间。电容c可耦接于波形斜率检测电路116的第三端n3及节点n之间。波形斜率检测电路116的第三端n3接收通道电压vd。

80.如图4所示,当通道电压vd上升达到参考电压vr时,稳压器110可介入开始调整控制电压vg,使整流开关swr脱离全开模式而进入稳压模式,随着控制电压vg下降,整流开关swr的电阻值增加;如此可避免通道电压vd过小,容易被噪声拉高上升超过关闭阀值电压,错误地关闭整流开关swr而降低整体电能转换效率。

81.当通道电压vd于单位时间的变化量增加时,经过电容c滤波后节点n的电压位准vin的绝对值增加。节点n的电压位准vin可对应于通道电压vd的波形变化斜率值。举例而言,如图4所示,当通道电压vd的波形变化较和缓(也就是,单位时间内的波形电压数值差异较小,正斜率或负斜率绝对值较小时),则电压位准vin的绝对值较小;当通道电压vd的波形变化较陡(也就是,单位时间内的波形电压数值差异较大,正斜率或负斜率绝对值较大时),则电压位准vin的绝对值较大。图4中,延迟时段td2可为通道电压vd及电压位准vin之间的延迟;例如:通道电压vd由正斜率的上升波形转换为负斜率的下降波形时,要经过延迟时段td2后,电压位准vin才会有对应的变化。根据实施例,波形斜率检测电路116可为高通滤波器。

82.根据实施例,如图3所示,电源电流调制电路118可包括第一晶体管t1至第四晶体管t4、第六晶体管t6及第七晶体管t7,以及第一电流源b1及第二电流源b2。电源电流调制电路118可耦接于上拉电源isource及下拉电源isink,上拉电源isource包括第五晶体管t5及开关sw

source

,且下拉电源isink包括第八晶体管t8及开关sw

sink

。

83.第一晶体管t1至第八晶体管t8的每一个包括第一端、第二端及控制端。举例而言,第一晶体管t1、第三晶体管t3、第四晶体管t4及第五晶体管t5的每一个可为p型晶体管,其第一端、第二端及控制端可分别为源极端、漏极端与门极端。第二晶体管t2、第六晶体管t6、第七晶体管t7及第八晶体管t8的每一个可为n型晶体管,其第一端、第二端及控制端可分别为漏极端、源极端与门极端。

84.第一晶体管t1的第一端耦接于第一参考电压端vdd,第二端耦接于波形斜率检测电路116的第一端n1,控制端耦接于第一晶体管t1的第二端,且第一晶体管t1的第二端输出第三电流ia至波形斜率检测电路116的第一端n1。

85.第二晶体管t2的第一端耦接于波形斜率检测电路116的第二端n2,第二端耦接于第二参考电压端vss,且控制端耦接于第二晶体管t2的第一端,其中第二晶体管t2的第一端接收波形斜率检测电路116的第二端n2流出的第四电流ib。第二参考电压端vss可为地端,或提供负电压。

86.第三晶体管t3的第一端耦接于第一参考电压端vdd,且控制端耦接于第一晶体管t1的控制端。

87.第一电流源b1耦接第三晶体管t3的第二端及第二参考电压端vss之间,用以提供第一参考电流ib1。

88.第四晶体管t4的第一端耦接于第一参考电压端vdd,第二端耦接于第三晶体管t3的第二端,且控制端耦接于第四晶体管t4的第二端,其中第五电流ip3流经第四晶体管t4的第一端。

89.第二电流源b2可用以提供第二参考电流ib2。第六晶体管t6的第一端耦接于第二电流源b2,第二端耦接于第二参考电压端vss,且控制端耦接于第二晶体管t2的控制端。

90.第七晶体管t7的第一端耦接于第六晶体管t6的第一端,第二端耦接于第二参考电压端vss,且控制端耦接于第七晶体管t7的第一端,其中第七电流in3流经第七晶体管t7。

91.如图3所示,当反相比较结果信号outb具有致能位准时,上拉电源isource的开关sw

source

可导通以使第六电流ih通过,以上拉控制电压vg。当比较结果信号out具有致能位准时,下拉电源isink的开关sw

sink

可导通以使第八电流il通过,以下拉控制电压vg。

92.上拉电源isource中,第五晶体管t5的第一端耦接于第一参考电压端vdd,第二端耦接于开关sw

source

,且控制端耦接于第四晶体管t4的控制端,其中第六电流ih通过第五晶体管t5流入开关sw

source

。第六电流ih可为上拉电流(source current),可用以上拉控制电压vg。

93.根据实施例,第五电流ip3可正相关于第一参考电流ib1及第三电流ia的差值,其可表示为ip3

∝

(ib1

‑

ia)。举例而言,ip3=(ib1

‑

ia)。

94.根据实施例,第五电流ip3可正相关于第六电流ih,其可表示为ih

∝

ip3。举例而言,ih=n1

×

ip3,其中第四晶体管t4及第五晶体管t5的尺寸比例为1:n1。

95.下拉电源isink中,第八晶体管t8的第一端耦接于开关sw

sink

,第二端耦接于第二参考电压端vss,且控制端耦接于第七晶体管t7的控制端,其中第八电流il流经第八晶体管t8。第八电流il可为下拉电流(sink current),可用以下拉控制电压vg。

96.根据实施例,第七电流in3可正相关于第二参考电流ib2及第四电流ib的差值,其可表示为in3

∝

(ib2

‑

ib)。举例而言,in3=ib2

‑

ib。

97.根据实施例,第八电流il可正相关于第七电流in3,其可表示为il

∝

in3。举例而言,il=n2

×

in3,其中第七晶体管t7及第八晶体管t8的尺寸比例为1:n2。

98.如图4的波形所示,当整流开关swr处于稳压模式下,通道电压vd的单位时间内的变化量随时间而逐渐增加,且控制电压vg变化范围也逐渐减小;故时段p2的通道电压vd的波形斜率大于时段p1的通道电压vd的波形斜率,但时段p2的控制电压vg变化范围却小于时段p1的控制电压vg变化范围(控制电压vg变化的波峰、波谷联机呈现下降趋势),其中时段p2接续于时段p1。也就是,欲对通道电压vd进行稳压时,于时段p1,稳压器110需对控制电压vg施以较大的调制电压;但于时段p2,稳压器110需对控制电压vg施以较小变化范围的调制电压,避免施加过大调制电压,错误地故度拉高通道电压vd,而使整流开关swr过早关闭降低转换效率。

99.为达成上述功效,当通道电压vd于单位时间的变化量逐渐增加时,且节点n的电压位准vin的绝对值逐渐增加时,本发明使流经上拉电源isource的第六电流ih的电流值的绝对值逐渐降低,且流经下拉电源isink的第八电流il的电流值的绝对值逐渐降低,从而可于时段p1以较大的第六电流ih、第八电流il来较大幅度迅速地调整控制电压vg;相对地,可于时段p2以较小的第六电流ih、第八电流il来较精细和缓地调整控制电压vg,以两种不同强度的调制电压来调整整流开关swr的导通程度,从而精确地控制截止整流开关swr的时点,以避免过早关闭整流开关swr。

100.图5为另一实施例中,图1的同步整流控制器100的示意图。图5的同步整流控制器100用以控制整流开关swr。如图5所示,同步整流控制器100包括稳压器110。稳压器110具有输出端nout,输出端nout可提供控制电压vg至整流开关swr的控制端。稳压器110包括比较器510、第一反相器520、波形斜率检测电路530、第二反相器540、主上拉电源i51、主下拉电源i52、辅助上拉电源i53及辅助下拉电源i54。

101.比较器510接收整流开关swr的通道电压vd,比较通道电压vd与参考电压v1而输出比较结果信号vsink,当通道电压vd大于参考电压v1时,比较结果信号vsink具有第一逻辑值(例如,1),当通道电压vd小于参考电压v1时,比较结果信号vsink具有第二逻辑值(例如,0)。

102.第一反相器520用以接收比较结果信号vsink,及产生反相比较结果信号vsource,使得比较结果信号vsink及反相比较结果信号vsource为互补。

103.波形斜率检测电路530接收整流开关swr的通道电压vd,而输出波形斜率信号vslope,当通道电压vd的波形为上升时,波形斜率信号vslope具有第三逻辑值(例如,高态),当通道电压vd的波形为下降时,波形斜率信号vslope具有第四逻辑值(例如,低态)。举例而言,波形斜率检测电路530的结构可同于图3的波形斜率检测电路116,包括电容及两电阻。

104.第二反相器540用以接收波形斜率信号vslope,及产生反相波形斜率信号vslope’,使得波形斜率信号vslope及反相波形斜率信号vslope’为互补。

105.主上拉电源i51耦接于输出端nout,由比较结果信号vsink与反相比较结果信号vsource中的一个所致能,用以上拉控制电压vg。主下拉电源i52耦接于输出端nout,由比较结果信号vsink与反相比较结果信号vsource中的另一个所致能,用以下拉控制电压vg。

106.以图5所示举例而言,主上拉电源i51及主下拉电源i52可分别由反相比较结果信号vsource及比较结果信号vsink所致能,当比较结果信号vsink具有致能位准,可致能主下拉电源i52,例如:使下拉电源i52中的开关导通;当反相比较结果信号vsource具有致能位准,可致能主上拉电源i51,例如:使上拉电源i51中的开关导通。

107.辅助上拉电源i53耦接于输出端nout,波形斜率信号vslope与反相波形斜率信号vslope’中的一个是致能辅助上拉电源i53的必要信号,使得辅助上拉电源i53选择性地与主上拉电源i51共同上拉控制电压vg。辅助下拉电源i54耦接于该输出端nout,波形斜率信号vslope与反相波形斜率信号vslope’中的另一个是致能辅助下拉电源i54的必要信号,使得辅助下拉电源i54选择性地与该主下拉电源i52共同下拉该控制电压。

108.以图5所示举例而言,辅助上拉电源i53及辅助下拉电源i54可分别由信号vsource2及信号vsink2所致能;而信号vsource2及信号vsink2分别是与反相波形斜率信号vslope'与波形斜率信号vslope相关,详细逻辑运算稍后段落叙述。当比较结果信号vsink2具有致能位准,可致能辅助下拉电源i54,当反相比较结果信号vsource2具有致能位准,可致能主上拉电源i51。

109.图5中,主上拉电源i51、主下拉电源i52、辅助上拉电源i53及辅助下拉电源i54的每一个可包括串联的电流源及开关,当开关被导通时,则电流可流过开关,从而致能该电源。

110.相似于图2,图5的同步整流控制器100可包括全开控制器120及多任务器sw,以切换整流开关swr的控制端接收控制电压vg或全开电压vf。

111.图6为图5的信号的波形图。图6仅为举例,用以说明图5,但实施例不限于此。如图5及图6所示,主上拉电源i51由反相比较结果信号vsource所致能,主下拉电源i52由比较结果信号vsink所致能,辅助上拉电源i53由反相波形斜率信号vslope’与反相比较结果信号vsource所共同致能,且辅助下拉电源i54由波形斜率信号vslope与比较结果信号vsink所共同致能。

112.上述以两信号共同致能电源,可使用与门(and gate)。举例而言,如图5所示,同步整流控制器100可包括与门550与与门560。与门550可接收比较结果信号vsink及波形斜率信号vslope以执行与(and)运算,以生成信号vsink2。与门560可接收反相比较结果信号

vsource及反相波形斜率信号vslope’以执行与运算,以生成信号vsource2。信号vsource2及信号vsink2可分别用以控制辅助上拉电源i53及辅助下拉电源i54。当信号vsource2具有致能位准,可致能辅助上拉电源i53,且当信号vsink2具有致能位准,可致能辅助下拉电源i54。

113.如图5及图6所示阶段a,当通道电压vd小于参考电压v1(也就是,vd<v1)且通道电压vd的波形为下降时,辅助上拉电源i53由反相波形斜率信号vslope’与反相比较结果信号vsource所共同致能。

114.如图5及图6所示阶段c,当通道电压vd大于参考电压v1(也就是,vd>v1)且通道电压vd的波形为上升时,辅助下拉电源i54由波形斜率信号vslope与比较结果信号vsink所共同致能。

115.实际比较器510运算输出结果必然会延迟,因此如图6的箭头61所示,自通道电压vd大于参考电压v1起延迟第一延迟时间后,比较结果信号vsink变更为第一逻辑值(例如,高态)。如图6的箭头62所示,自通道电压vd小于参考电压v1起延迟第二延迟时间后,比较结果信号vsink变更为第二逻辑值(例如,低态)。

116.实际波形斜率检测电路530运算输出结果必然会延迟,因此如图6的箭头63所示,自该通道电压vd的波形自下降转变为上升起延迟第三延迟时间后,波形斜率信号vslope变更为第三逻辑值(例如,高态)。如图6的箭头64所示,自通道电压vd的波形自上升转变为下降起延迟第四延迟时间后,波形斜率信号vslope变更为第四逻辑值(例如,低态)。

117.图6中,电流ig为流经图5的输出端nout的电流,用以上拉或下拉控制电压vg。如图6所示,通过控制主上拉电源i51、主下拉电源i52、辅助上拉电源i53及辅助下拉电源i54,电流ig的波形可具有阶段a、阶段b、阶段c及阶段d,其说明如下。

118.阶段a中,主上拉电源i51及辅助上拉电源i53皆被致能,提供较大的上拉电流。阶段b中,主上拉电源i51被致能,但辅助上拉电源i53未被致能,提供较小的上拉电流。阶段c中,主下拉电源i52及辅助下拉电源i54皆被致能,提供较大的下拉电流。阶段d中,主下拉电源i52被致能,但辅助下拉电源i54未被致能,提供较小的下拉电流。于稳压器110根据通道电压vd执行稳压的期间,阶段a、阶段b、阶段c及阶段d可依序重复。通过图5及图6的架构,从而可于阶段a、阶段c中,分别以较大的上拉电流、下拉电流来较大幅度迅速地调整控制电压vg;相对地,可于阶段b、阶段d中,以较小的上拉电流、下拉电流来较精细和缓地调整控制电压vg。如此经由把这4个电流源开启时间予以逻辑组合后,可提供两种不同大小的上拉电流、下拉电流,可更精确地上拉或下拉控制电压vg。

119.图7为实施例中,同步整流控制器100的控制方法700的流程图。控制方法700可用以控制图2及图3的同步整流控制器100。控制方法700可包括以下步骤:

120.s710:全开控制器120关闭;

121.s720:比较整流开关swr的通道电压vd及参考电压vr,以产生比较结果信号out;

122.s730:根据比较结果信号out产生反相比较结果信号outb,其中比较结果信号out及反相比较结果信号outb为互补;

123.s740:判断通道电压vd是否小于参考电压vr?若是,进入步骤s750;若否,进入步骤s760;

124.s750:通道电压vd小于参考电压vr,比较结果信号out具有第二逻辑值,由反相比

较结果信号outb致能上拉电源isource以上拉控制电压vg;

125.s760:通道电压vd大于参考电压vr,比较结果信号out具有第一逻辑值,由比较结果信号out致能下拉电源isink以下拉控制电压vg;

126.s770:判断通道电压vd是否大于关闭整流开关阈值?若是,进入步骤s780;若否,进入步骤s720;及

127.s780:同步整流控制器110关闭整流开关swr。

128.步骤s710中,可使图2的电压vc等于控制电压vg而非全开电压vf。步骤s720至步骤s760的原理及操作已述于上文,不另重述。步骤s770中,可如图4所示,当整流开关swr的通道电压vd尚未增加至大于预定的关闭整流开关阈值时,可进入步骤s720以继续执行稳压操作,以避免过早关闭整流开关swr;而当通道电压vd大于关闭整流开关阈值时,同步整流控制器100可调整控制电压vg至预定值(例如,低电压),以关闭整流开关swr。

129.图8为实施例中,同步整流控制器100的控制方法800的流程图。控制方法800可用以控制图5的同步整流控制器100。控制方法800可包括以下步骤:

130.s810:全开控制器120关闭;

131.s820:比较整流开关swr的通道电压vd与参考电压v1而输出比较结果信号vsink;

132.s830:根据比较结果信号vsink产生反相比较结果信号vsource;

133.s840:判断通道电压vd是否小于参考电压v1?若是,进入步骤s850;若否,进入步骤s860;

134.s850:由反相比较结果信号vsource致能主上拉电源i51以上拉控制电压vg;

135.s852:判断反相波形斜率信号vslope’是否具有致能位准?若是,进入步骤s854;若否,进入步骤s870;

136.s854:致能辅助上拉电源i53;

137.s860:由比较结果信号vsink致能主下拉电源i52以下拉控制电压vg;

138.s862:判断波形斜率信号vslope是否具有致能位准?若是,进入步骤s864;若否,进入步骤s870;

139.s864:致能辅助下拉电源i54;

140.s870:判断通道电压vd是否大于关闭整流开关阈值?若是,进入步骤s880;若否,进入步骤s820;及

141.s880:同步整流控制器110关闭整流开关swr。

142.综上所述,通过实施例提供的同步整流控制器110、控制方法700及控制方法800,可更加精确地调整控制电压vg,从而避免过早关闭整流开关swr,以使一次侧及二次侧的整体电路正常操作。对于处理本领域长期的难题,实有帮助。

143.以上所述仅为本发明的较佳实施例,凡依本发明申请专利范围所做的均等变化与修饰,皆应属本发明的涵盖范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1