正电荷泵电路以及负电荷泵电路的制作方法

1.本实用新型涉及被配置为生成正电压和负电压的电荷泵电路。

背景技术:

2.参考图1a,图1a示出了正电荷泵电路100p的电路图。电路100p 包括:n沟道mos晶体管mn1,其源极端子被耦合到电源节点102、并且漏极端子被耦合到中间节点na1;以及n沟道mos晶体管mn2,其源极端子被耦合到电源节点102、并且漏极端子被耦合到中间节点 na2。电路100p还包括:p沟道mos晶体管mp1,其源极端子被耦合到输出节点104、并且漏极端子被耦合到节点na1;以及p沟道 mos晶体管mp2,其源极端子被耦合到输出节点104并且漏极端子被耦合到中间节点na2。晶体管mn1和mp1的栅极端子被连接在一起并且被进一步连接到中间节点na2。晶体管mn2和mp2的栅极端子被连接在一起并且被进一步连接到中间节点na1。晶体管mn1、 mn2、mp1和mp2形成cmos锁存电路。

3.电容器c1具有的一个端子被耦合到节点na1,并且另一端子被耦合来接收时钟信号ck的逻辑反相,该逻辑反相由cmos反相器电路106生成,cmos反相器电路106由正电源电压vdd供电并且接收时钟信号ck作为输入。电容器c2具有的一个端子被耦合到节点na2,并且另一端子被耦合来接收时钟信号ckn的逻辑反相(它是时钟信号ck的逻辑反相),该逻辑反相由cmos反相器电路108生成,反相器电路108由正电源电压vdd供电并且接收时钟信号ckn作为输入。

4.电路100p的负载107由负载电容器cload示意性地表示,负载电容器cload具有与输出节点104耦合的一个端子以及与接地节点耦合的第二端子以及在输出节点104与接地节点之间耦合的电流源 iload。

5.电源节点102被配置为接收正电源电压vdd。输出节点104被配置为生成倍增的正输出电压vpos,其中vpos大约为2*vdd。

6.参考图1b,图1b示出了针对负电荷泵电路100n的电路图。电路100n包括:p沟道mos晶体管mp1,其源极端子被耦合到电源节点102并且漏极端子被耦合到中间节点na1;以及p沟道mos晶体管mp2,其源极端子被耦合到电源节点102并且漏极端子被耦合到中间节点na2。电路100n还包括:n沟道mos晶体管mn1,其源极端子被耦合到输出节点104并且漏极端子被耦合到中间节点na1;以及n沟道mos晶体管mn2,其源极端子被耦合到输出节点104并且漏极端子被耦合到中间节点na2。晶体管mn1和mp1的栅极端子被连接在一起并且被进一步连接到中间节点na2。晶体管mn2和mp2 的栅极端子被连接在一起并且被进一步连接到中间节点na1。晶体管 mn1、mn2、mp1和mp2形成cmos锁存电路。

7.电容器c1的一个端子被耦合到节点na1,并且另一端子被耦合来接收时钟信号ck的逻辑反相,该逻辑反相由cmos反相器电路 106生成,cmos反相器电路106由正电源电压vdd供电并且接收时钟信号ck作为输入。电容器c2的一个端子被耦合到节点na2,并且另一端子被耦合来接收时钟信号ckn的逻辑反相(它是时钟信号 ck的逻辑反相),该逻辑反相由cmos反相器电路108生成,cmos 反相器电路108由正电源电压vdd供电并且接收时钟信号

ckn作为输入。

8.电路100n的负载107由负载电容器cload示意性地表示,负载电容器具有与输出节点104耦合的一个端子以及与接地节点耦合的第二端子以及在正电源电压vdd与输出节点104之间耦合的电流源 iload。

9.电源节点102被配置为接收接地电压vgnd。输出节点104被配置为生成倍增的负输出电压vneg,其中vneg大约等于-vdd。

10.输出节点104处的输出阻抗与时钟信号ck和ckn的频率以及执行电荷转移的开关晶体管mn1、mn2、mp1和mp2的导通电阻 (rds_on)相关。输出阻抗由以下公式给出:

[0011][0012]

其中:c是飞跨电容器的电容(即,c1或c2与时钟相位相关)。

[0013]

晶体管mn1、mn2、mp1和mp2的导通电阻(rds_on)由以下公式给出:

[0014][0015]

其中:l是晶体管的长度,w是晶体管的宽度,c

ox

是栅极电容,v

gs

是栅源电压,并且v

th

是阈值电压。

[0016]

如果晶体管宽度w减小,导通电阻(rds_on)增加,并且每个开关晶体管两端的电压降更大,效率也对应降低。

[0017]

开关电容由下式给出:

[0018]csw

=c

ox

*w*l

eff

[0019]

其中:l

eff

是晶体管开关的有效长度。

[0020]

注意,如果晶体管宽度w增加,会导致电容器上极板上的电容增加,对应的电荷损失增加,效率降低。

[0021]

现在参考图2a,图2a示出了正电荷泵电路200p的电路图(也参见于2020年6月25日提交的美国专利申请号16/911,967的图2a,其通过引用并入本文)。电路200p包括(正)自举电路,自举电路包括:n沟道mos晶体管mn1,其源极端子被耦合到电源节点202并且漏极端子被耦合到中间节点na1;以及n沟道mos晶体管mn2,其源极端子被耦合到电源节点202并且漏极端子被耦合到中间节点 na2。利用以下方式将晶体管mn1与mn2交叉耦合:在节点na2 处晶体管mn1的栅极端子耦合到晶体管mn2的漏极端子,并且在节点na1处晶体管mn2的栅极端子耦合到晶体管mn1的漏极端子。

[0022]

自举电容器cbs1的一个端子被耦合到节点na1,并且另一端子被耦合来接收时钟信号ck的逻辑反相,该逻辑反相ck1n由cmos 反相器电路206p生成,cmos反相器电路206p由正电源电压vdd 供电并接收时钟信号ck作为输入。自举电容器cbs2的一个端子被耦合到节点na2,并且另一端子被耦合来接收时钟信号ckn的逻辑反相(这是时钟信号ck的逻辑反相),该逻辑反相ck1由cmos反相器电路208p生成,cmos反相器电路208p由正电源电压vdd供电并且接收时钟信号ckn作为输入。

[0023]

cmos切换电路210p具有被耦合来接收正电源电压vdd的第一端子以及在中间节点nb1处的第二端子。切换电路210p中的p沟道 mos晶体管mp1的源极端子被耦合到节点na1,

而切换电路210p 中的n沟道mos晶体管mn3的源极端子被耦合来接收时钟信号ckn。第二端子在晶体管mp1和mn3的共用漏极处。晶体管mp1和mn3 的栅极被耦合到第一端子(vdd)。

[0024]

cmos切换电路212p具有被耦合来接收正电源电压vdd的第一端子以及在中间节点nb2处的第二端子。切换电路212p中的p沟道 mos晶体管mp2的源极端子被耦合到节点na2,并且切换电路212p 中的n沟道mos晶体管mn4的源极端子被耦合来接收时钟信号ck。第二端子位于晶体管mp2和mn4的共用漏极处。晶体管mp2和mn4 的栅极被耦合到第一端子(vdd)。

[0025]

具有自举电路的电路210p和212p形成基于自举的电平移位电路。

[0026]

cmos切换电路220p具有与节点nb1耦合的第一端子以及位于中间节点nc1处的第二端子。切换电路220p中的n沟道mos晶体管mn5的源极端子被耦合到电源节点202,并且切换电路220p中的 p沟道mos晶体管mp3的源极端子被耦合到输出节点204。第二端子在晶体管mn5和mp3的共用漏极处。晶体管mn5和mp3的栅极端子被耦合到第一端子(nb1)。

[0027]

cmos切换电路222p具有与节点nb2耦合的第一端子以及在中间节点nc2处的第二端子。切换电路222p中的n沟道mos晶体管 mn6的源极端子被耦合到电源节点202,并且切换电路222p中的p 沟道mos晶体管mp4的源极端子被耦合到输出节点204。第二端子在晶体管mn6和mp4的共用漏极处。晶体管mn6和mp4的栅极端子被耦合到第一端子(nb2)。

[0028]

电容器c1的一个端子被耦合到节点nc1,并且另一端子被耦合来接收时钟信号ck1n的逻辑反相,该逻辑反相由cmos反相器电路216p生成,cmos反相器电路216p由正电源电压vdd供电并且接收时钟信号ck1n作为输入。电容器c2的一个端子被耦合到节点nc2,并且另一端子被耦合来接收时钟信号ck1的逻辑反相,该逻辑反相由cmos反相器电路218p生成,cmos反相器电路218p由正电源电压vdd供电并且接收时钟信号ck1作为输入。

[0029]

电路200p的负载207由负载电容器cload示意性地表示,负载电容器cload具有与输出节点204耦合的一个端子以及与接地节点耦合的第二端子以及在输出节点204与接地节点之间耦合的电流源 iload。

[0030]

电源节点202被配置为接收正电源电压vdd。输出节点204被配置为生成倍增的正输出电压vpos,其中vpos大约为2*vdd。

[0031]

图2b示出了针对图2a的电路200p的操作的时钟信号ck、ckn、 ck1和ck1n以及节点na1、na2、nb1、nb2、nc1和nc2处的信号的波形。应注意,为了便于理解电路200p的操作,图2b波形中未示出信号传播延迟。将进一步注意,时钟信号的电压电平是理想化的,并且在实现时,电压将基本等于(例如,在1-20%内),但不一定等于理想的vdd和2*vdd电压电平。

[0032]

由晶体管mn1、mn2、自举电容器cbs1、cbs2和反相器206p、 208p形成的电路是正自举电路,正自举电路响应于以电源vdd和接地为基准的时钟信号ck、ckn来运行,以在节点na1、na2处生成以2*vdd和vdd为基准的时钟信号。当时钟信号ck为逻辑高(vdd) 时,反相器206p输出的时钟信号ck1n为逻辑低(gnd)。晶体管 mn1导通,这是因为节点na2通过电容器cbs2升高到2*vdd电压电平(即,由于晶体管mn1的栅极电压在源极端子处超过vdd多于 vth而导通),并且自举电容器cbs1被充电到vdd电压电平。在时钟信号的下一相位,时钟信号ck为逻辑低,并且反相器206p输出的时钟信号ck1n为逻辑高。晶体管mn1关断,这是因为节点na2处于vdd电压电平(即,因为晶体管mn1的栅极电压等于源极电压vdd 并且因此不超过vth而关断),并且节点na1处的电压借助电容器 cbs1上存储的自举电压vdd而升高到2*vdd电压电平。响应于时钟信号ckn和ck1的相位,发生类似的过程。

[0033]

由cmos切换电路210p和212p形成的电路装置作为电平移位级,将节点na1、na2处以2*vdd和vdd为基准的时钟信号移位,以在节点nb1、nb2处生成以2*vdd和接地为基准的时钟信号。关于电路210p的操作考虑如下内容:当时钟信号ckn为逻辑低时,晶体管 mn3被导通(即,因为晶体管mn3的栅极电压在源极端子处超过接地多于vth)并且节点nb1被钳位到接地。晶体管mp1关断,这是因为节点na1处于vdd电平。在时钟信号的下一相位,时钟信号ckn 为逻辑高,导致晶体管mn3关断(即,因为晶体管mn3的栅极电压等于源极电压vdd,并且因此不超过vth)。在同一相位,节点na1 处于2*vdd电压电平(见上文讨论),并且晶体管mp1导通(即,晶体管mp1的vgs超过vth),将2*vdd电压电平传递到节点nb1。响应于时钟信号ck的相位,对于电路212p发生类似的过程。

[0034]

由电容器c1、c2和反相器216p、218p形成的电路装置响应于以电源vdd和接地为基准的时钟信号ck1、ck1n运行,以在节点nc1、 nc2处生成以2*vdd和vdd为基准的时钟信号。考虑与具有电容器 c1和反相器216p的电路有关的以下操作:当时钟信号ck1n为逻辑高时,反相器216p的输出为逻辑低。同时,如下所述,晶体管mn5 被导通并且电容器c1被充电至vdd电压电平。在时钟信号的下一相位处,时钟信号ck1n为逻辑低,并且反相器216p的输出为逻辑高。节点nc1处的电压借助电容器c1升高至2*vdd电压电平。响应于时钟信号ck1的相位,对于具有电容器c2和反相器218p的电路发生类似的过程。

[0035]

由cmos切换电路220p和222p形成的电路装置用作电荷转移驱动级,以将节点nc1、nc2处的2*vdd电压选择性地传递到输出节点204来驱动电容和电流负载207。考虑与电路220p的操作有关的以下内容:当时钟信号ckn和ck1n均为逻辑高时,节点nb1处的电压为2*vdd电压电平,并且晶体管mn5导通(即,晶体管mn5的 vgs超过vth),从而将电容器c1充电至vdd电压电平。在时钟信号的下一相位处,当时钟信号ckn和ck1n二者为逻辑低时,节点nb1 处的电压为接地电平,并且晶体管mp3导通(即,晶体管mp3的 vgs超过vth),以将节点nc1处的2*vdd电压电平传递到输出节点 204。响应于时钟信号ck和ck1的相位,电路222p发生类似的过程。

[0036]

电路实现方式的一个优点是增加电荷转移开关晶体管的vgs来降低导通电阻(rds_on)。例如,与图1a的电荷泵电路相比,输出阻抗对应降低。

[0037]

现在参考图3a,图3a示出了负电荷泵电路200n的电路图(也参见于2020年6月25日提交的美国专利申请号16/911,967的图2e,其通过引用并入本文)。电路200n包括负自举电路,负自举电路包括 p沟道mos晶体管mp1,其源极端子被耦合到电源节点202并且漏极端子被耦合到中间节点na1;以及p沟道mos晶体管mp2,其源极端子被耦合到电源节点202并且漏极端子被耦合到中间节点na2。利用以下方式将晶体管mp1与mp2交叉耦合:在节点na2处晶体管 mp1的栅极端子耦合到晶体管mp2的漏极端子,并且在节点na1处晶体管mp2的栅极端子耦合到晶体管mp1的漏极端子。

[0038]

自举电容器cbs1的一个端子被耦合到节点na1,并且另一端子被耦合来接收时钟信号ck的逻辑反相,该逻辑反相ck1n由cmos 反相器电路206n生成,cmos反相器电路206n由正电源电压vdd 供电并且接收时钟信号ck作为输入。自举电容器cbs2的一个端子被耦合到节点na2,并且另一端子被耦合来接收时钟信号ckn的逻辑反相(它是时钟信号ck的逻辑反相),该逻辑反相ck1由cmos 反相器电路208n生成,cmos反相器电路208n由正电源电压vdd 供电并且接收时钟信号ckn作为输入。

[0039]

cmos切换电路210n具有被耦合来接收接地电压gnd的第一端子以及在中间节点nb1处的第二端子。切换电路210n中的p沟道 mos晶体管mp3的源极端子被耦合来接收时钟信号ckn,并且切换电路210n中的n沟道mos晶体管mn1的源极端子被耦合到节点na1。第二端子位于晶体管mp3和mn1的共用漏极处。晶体管mp3和mn1 的栅极被耦合到第一端子(gnd)。

[0040]

cmos切换电路212n具有被耦合来接收接地电压gnd的第一端子以及在中间节点nb2处的第二端子。切换电路212n中的p沟道 mos晶体管mp4的源极端子被耦合来接收时钟信号ck,并且切换电路212n中的n沟道mos晶体管mn2的源极端子被耦合到na2。第二端子位于晶体管mp4和mn2的共用漏极处。晶体管mp4和mn2 的栅极端子被耦合到第一端子(gnd)。

[0041]

具有自举电路的电路210n和212n形成基于自举的电平移位电路。

[0042]

cmos切换电路220n具有与节点nb1耦合的第一端子和位于中间节点nc1处的第二端子。切换电路220n中的p沟道mos晶体管 mp5的源极端子被耦合到电源节点202,并且切换电路220n中的n 沟道mos晶体管mn3的源极端子被耦合到输出节点204。第二端子在晶体管mp5和mn3的共用漏极处。晶体管mp5和mn3的栅极被耦合到第一端子(nb1)。

[0043]

cmos切换电路222n具有与节点nb2耦合的第一端子和在中间节点nc2处的第二端子。切换电路222n中p沟道mos晶体管mp6 的源极端子被耦合到节点202,并且切换电路222n中的n沟道mos 晶体管mn4的源极端子被耦合到输出节点204。第二端子在晶体管 mp6和mn4的共用漏极处。晶体管mp6和mn4的栅极被耦合到第一端子(nb2)。

[0044]

电容器c1的一个端子被耦合到节点nc1,并且另一端子被耦合来接收时钟信号ck1n的逻辑反相,该逻辑反相由cmos反相器电路216n生成,cmos反相器电路216n由正电源电压vdd供电并且接收时钟信号ck1n作为输入。电容器c2的一个端子被耦合到节点nc2,并且另一端子被耦合来接收时钟信号ck1的逻辑反相,该逻辑反相由cmos反相器电路218n生成,cmos反相器电路218n由正电源电压vdd供电并且接收时钟信号ck1作为输入。

[0045]

电路200n的负载207由负载电容器cload示意性地表示,负载电容器cload具有与输出节点204耦合的一个端子以及与接地节点耦合的第二端子以及在正电源电压vdd与输出节点204之间耦合的电流源iload。

[0046]

电源节点202被配置为接收接地电压vgnd。输出节点204被配置为生成倍增的负输出电压vneg,其中vneg大约为-vdd。

[0047]

图3b示出了针对图3a的电路200n的操作的时钟信号ck、ckn、 ck1和ck1n以及节点na1、na2、nb1、nb2、nc1和nc2处的信号的波形。应注意,为了便于理解电路200n的操作,图3b波形中未示出信号传播延迟。将进一步注意到,时钟信号的电压电平是理想化的,并且在实现时,电压将基本上等于(例如,在1-20%内)但不一定等于vdd和-vdd电压电平。

[0048]

由晶体管mp1、mp2、自举电容器cbs1、cbs2和反相器206n、 208n形成的电路装置是负自举电路,负自举电路响应于以电源vdd 和接地为基准的时钟信号ck、ckn运行,以在节点na1、na2处生成以-vdd和接地为基准的时钟信号。当时钟信号ckn为逻辑低 (gnd)时,反相器208n输出的时钟信号ck1将为逻辑高(vdd)。晶体管mp2导通,这是因为节点na1借助电容器cbs1升高到-vdd 电压电平(即,由于晶体管mp2的栅极电压比源极端子处的接地电压低vth以上而导通)并且自举电容器cbs2在节点na2处被充电到接地电压电平。在时钟信号的下一相位处,时钟信号ckn为逻辑高,并且反相器208n输出的时钟信号ck1为逻辑低。晶体管mp2关断,这是因为节点na1处于接地电压电平(即,因为晶体管mp2的栅极电压等于源极

电压接地并且因此不超过vth而关断)并且节点na2 处的电压借助电容器cbs2上存储的自举接地电压而升高到-vdd电压电平。响应于时钟信号ck和ck1n的相位,发生类似的过程。

[0049]

由cmos切换电路210n和212n形成的电路装置用作电平移位级,以将节点na1、na2处以-vdd和接地为基准的时钟信号移位,从而在节点nb1、nb2处生成以-vdd和+vdd为基准的时钟信号。考虑与电路212n的操作有关的以下内容:当时钟信号ck为逻辑高时,晶体管mp4导通(即,因为晶体管mp4的栅极电压比源极端低vth以上而导通),晶体管mn2关断(即,因为节点na2接地),并且节点 nb2被钳位到vdd。在时钟信号的下一相位中,时钟信号ck为逻辑低,导致晶体管mp4关断(即,因为晶体管mp4的栅极电压等于源极电压接地,并且因此不超过vth)。在同一相位中,节点na2处于

ꢀ‑

vdd电压电平(参见上文讨论),并且晶体管mn2导通(即,晶体管mn2的vgs超过vth),从而将-vdd电压电平传递到节点nb2。响应于时钟信号ckn的相位,对于电路210n发生类似的过程。

[0050]

由电容器c1、c2和反相器216n、218n形成的电路响应于以电源 vdd和接地为基准的时钟信号ck1、ck1n运行,以在节点nc1、nc2 处生成以-vdd和接地为基准的时钟信号。考虑与具有电容器c2和反相器218n的电路有关的以下操作:当时钟信号ck1为逻辑低时,反相器218n的输出为逻辑高。同时,如下文将讨论的,晶体管mp6被导通并且电容器c2被放电至接地电压电平。在时钟信号的下一相位中,时钟信号ck1为逻辑高,并且反相器218n的输出为逻辑低。节点nc2处的电压借助电容器c2而升高至-vdd电压电平。响应于时钟信号ck1n的相位,具有电容器c1和反相器216n的电路发生类似的过程。

[0051]

由cmos切换电路220n和222n形成的电路装置用作电荷转移驱动级,以将节点nc1、nc2处的-vdd电压选择性地传递到输出节点 204来驱动电容和电流负载207。考虑与电路222n的操作有关的以下内容:当时钟信号ck和ck1均为逻辑低时,节点nb2处的电压处于-vdd电压电平,并且晶体管mp6导通(即,晶体管mp6的vgs 超过vth),从而将电容器c2放电至接地电压电平。在时钟信号的下一相位中,当时钟信号ck和ck1均为逻辑高时,节点nb2处的电压处于vdd电平并且晶体管mn4导通(即,晶体管mn4的vgs超过vth),从而将节点nc2处的-vdd电压电平传递到节点204。响应于时钟信号ckn和ck1n的相位,电路220n发生类似的过程。

[0052]

电路实现方式的一个优点是增加电荷转移开关晶体管的vgs来降低导通电阻(rds_on)。例如,与图1b的电荷泵电路相比,输出阻抗对应降低。

技术实现要素:

[0053]

本公开的目的是提供正电荷泵电路与负电荷泵电路,以至少部分地解决现有技术中存在的上述问题。

[0054]

本公开的一方面提供了一种正电荷泵电路,被配置为从输入电压生成输出电压,其中输出电压的正电压电平比输入电压的电压电平更正,正电荷泵电路包括:负自举电路,被配置为响应于第一时钟信号而生成控制信号,其中控制信号在接地电压与负电压之间切换;升压电路,被配置为响应于第二时钟信号而生成正升压电压;以及电荷转移晶体管,其漏极端子被耦合来接收正升压电压并且其源极端子被耦合至输出节点,其中电荷转移晶体管的栅极端子由控制信号的负电压偏置而导通并且将正升压电压传递至输出节点并且生成输出电压。

[0055]

根据一个或多个实施例,其中第一时钟信号是第二时钟信号的逻辑反相。

[0056]

根据一个或多个实施例,正电荷泵电路还包括电平移位电路,电平移位电路被配置为接收控制信号并且生成在正升压电压的电平与负电压的电平之间切换的电平移位控制信号,并且其中电平移位控制信号被施加到电荷转移晶体管的栅极端子。

[0057]

根据一个或多个实施例,其中电平移位电路包括:第一导电类型的第一mos晶体管,其具有被耦合来接收控制信号的源极;以及第二导电类型的第二mos晶体管,其具有被耦合来接收处于正升压电压的电平的信号的源极,其中第一mos晶体管和第二mos晶体管的共用漏极被配置为生成电平移位控制信号。

[0058]

根据一个或多个实施例,其中第一mos晶体管由第一电压栅极偏置,并且其中第二mos晶体管由第二电压栅极偏置,其中第二电压的电平比第一电压的电平更正。

[0059]

根据一个或多个实施例,其中升压电路包括:晶体管,具有与输入电压耦合的源极端子以及生成正升压电压的漏极端子;电容器,具有与晶体管和电荷转移晶体管的漏极端子耦合的第一端子;以及反相器电路,具有被耦合来接收第二时钟信号的输入以及与电容器的第二端子耦合的输出。

[0060]

根据一个或多个实施例,其中负自举电路包括:晶体管,具有与接地电压耦合的源极端子并且具有生成控制信号的漏极端子;电容器,具有与晶体管的漏极端子耦合的第一端子;以及反相器电路,具有被耦合来接收第一时钟信号的输入以及与电容器的第二端子耦合的输出。

[0061]

本公开的另一方面提供了一种负电荷泵电路,被配置为从输入电压生成输出电压,其中输出电压的负电压电平比输入电压的电压电平更负,负电荷泵电路包括:正自举电路,被配置为响应于第一时钟信号而生成控制信号,其中控制信号在第一正电压与第二正电压之间切换,其中第二正电压的电压电平比第一正电压的电压电平更正;升压电路,被配置为响应于第二时钟信号而生成负升压电压;以及电荷转移晶体管,其漏极端子被耦合来接收负升压电压并且源极端子被耦合到输出节点,其中电荷转移晶体管的栅极端子由控制信号的第二正电压偏置而导通并且将负升压电压传递至输出节点并且生成输出电压。

[0062]

根据一个或多个实施例,其中第一时钟信号是第二时钟信号的逻辑反相。

[0063]

根据一个或多个实施例,负电荷泵电路还包括电平移位电路,电平移位电路被配置为接收控制信号并且生成在负升压电压的电平与第二正电压的电平之间切换的电平移位控制信号,并且其中电平移位控制信号被施加到电荷转移晶体管的栅极端子。

[0064]

根据一个或多个实施例,其中电平移位电路包括:第一导电类型的第一mos晶体管,其具有被耦合来接收控制信号的源极;以及第二导电类型的第二mos晶体管,其具有被耦合来接收处于负升压电压的电平的信号的源极,其中第一mos晶体管和第二mos晶体管的共用漏极被配置为生成电平移位控制信号。

[0065]

根据一个或多个实施例,其中第一mos晶体管由第一电压栅极偏置,并且其中第二mos晶体管由第二电压栅极偏置,其中第一电压的电平比第二电压的电平更正。

[0066]

根据一个或多个实施例,其中升压电路包括:晶体管,具有与输入电压耦合的源极端子以及生成负升压电压的漏极端子;电容器,具有与晶体管以及电荷转移晶体管的漏极端子耦合的第一端子;以及反相器电路,具有被耦合来接收第二时钟信号的输入以及与电容器的第二端子耦合的输出。

[0067]

根据一个或多个实施例,其中正自举电路包括:晶体管,具有与正电源电压耦合的源极端子并且具有生成控制信号的漏极端子;电容器,具有与晶体管的漏极端子耦合的第一端子;以及反相器电路,具有被耦合来接收第一时钟信号的输入以及与电容器的第二端子耦合的输出。

[0068]

本公开的额外方面提供了一种正电荷泵电路,被配置为从输入电压生成输出电压,其中输出电压的正电压电平比输入电压的电压电平更正,正电荷泵电路包括:负自举电路,被配置为响应于第一时钟信号而生成第一控制信号,其中第一控制信号在接地电压与负电压之间切换;正自举电路,被配置为响应于第一时钟信号而生成第二控制信号,其中第二控制信号在第一正电压与第二正电压之间切换,其中第二正电压的电压电平比第一正电压的电压电平更正;升压电路,被配置为响应于第二时钟信号而在中间节点处生成正升压电压;第一电荷转移晶体管,其漏极端子被耦合到中间节点并且源极端子被耦合来接收输入电压,其中第一电荷转移晶体管的栅极端子由第二控制信号的第二正电压偏置而导通,以将第一电荷转移晶体管导通并且将输入电压传递至中间节点;以及第二电荷转移晶体管,其漏极端子被耦合到中间节点并且源极端子被耦合到输出节点,其中第二电荷转移晶体管的栅极端子由第一控制信号的负电压偏置,以将第二电荷转移晶体管导通并且将正升压电压传递到输出节点并且生成输出电压。

[0069]

根据一个或多个实施例,其中第一时钟信号是第二时钟信号的逻辑反相。

[0070]

根据一个或多个实施例,其中第一电荷转移晶体管和第二电荷转移晶体管的栅极端子被彼此连接来接收第三控制信号,其中第三控制信号在第一控制信号的负电压与第二控制信号的第二正电压之间切换。

[0071]

根据一个或多个实施例,正电荷泵电路还包括电平移位电路,电平移位电路被配置为接收第一控制信号和第二控制信号并且生成第三控制信号。

[0072]

根据一个或多个实施例,其中电平移位电路包括:第一导电类型的第一mos晶体管,其具有被耦合来接收第一控制信号的源极;以及第二导电类型的第二mos晶体管,其具有被耦合来接收第二控制信号的源极,其中第一mos晶体管和第二mos晶体管的共用漏极被配置为生成第三控制信号。

[0073]

根据一个或多个实施例,其中第一mos晶体管由第一电压栅极偏置,并且其中第二mos晶体管由第二电压栅极偏置,其中第二电压的电平比第一电压的电平更正。

[0074]

根据一个或多个实施例,其中升压电路包括:电容器,其第一端子被耦合到第一电荷转移晶体管和第二电荷转移晶体管的漏极端子;以及反相器电路,其输入被耦合来接收第二时钟信号并且输出被耦合到电容器的第二端子。

[0075]

根据一个或多个实施例,其中负自举电路包括:晶体管,具有与接地电压耦合的源极端子以及生成第一控制信号的漏极端子;电容器,具有与晶体管的漏极端子耦合的第一端子;以及反相器电路,具有被耦合来接收第一时钟信号的输入以及与电容器的第二端子耦合的输出。

[0076]

根据一个或多个实施例,其中正自举电路包括:晶体管,具有与输入电压耦合的源极端子以及生成第二控制信号的漏极端子;电容器,具有与晶体管的漏极端子耦合的第一端子;以及反相器电路,具有被耦合来接收第一时钟信号的输入以及与电容器的第二端子耦合的输出。

[0077]

本公开的另一方面提供了一种负电荷泵电路,被配置为从输入电压生成输出电压,其中输出电压的负电压电平比输入电压的电压电平更负,负电荷泵电路包括:负自举电路,被配置为响应于第一时钟信号而生成第一控制信号,其中第一控制信号在接地电压与负电压之间切换;正自举电路,被配置为响应于第一时钟信号而生成第二控制信号,其中第二控制信号在第一正电压与第二正电压之间切换,其中第二正电压的电压电平比第一正电压的电压电平更正;升压电路,被配置为响应于第二时钟信号而在中间节点处生成负升压电压;第一电荷转移晶体管,其漏极端子被耦合到中间节点并且源极端子被耦合来接收输入电压,其中第一电荷转移晶体管的栅极端子由第一控制信号的负电压偏置,以将第一电荷转移晶体管导通并且将输入电压传递至中间节点;以及第二电荷转移晶体管,其漏极端子被耦合到中间节点并且源极端子被耦合到输出节点,其中第二电荷转移晶体管的栅极端子由第二控制信号的第二正电压偏置,以将第二电荷转移晶体管导通并且将负升压电压传递到输出节点并且生成输出电压。

[0078]

根据一个或多个实施例,其中第一时钟信号是第二时钟信号的逻辑反相。

[0079]

根据一个或多个实施例,其中第一电荷转移晶体管和第二电荷转移晶体管的栅极端子被彼此连接来接收第三控制信号,其中第三控制信号在第一控制信号的负电压与第二控制信号的第二正电压之间切换。

[0080]

根据一个或多个实施例,负电荷泵电路还包括电平移位电路,电平移位电路被配置为接收第一控制信号和第二控制信号并且生成第三控制信号。

[0081]

根据一个或多个实施例,其中电平移位电路包括:第一导电类型的第一mos晶体管,其具有被耦合来接收第一控制信号的源极;以及第二导电类型的第二mos晶体管,其具有被耦合来接收第二控制信号的源极,其中第一mos晶体管和第二mos晶体管的共用漏极被配置为生成第三控制信号。

[0082]

根据一个或多个实施例,其中第一mos晶体管由第一电压栅极偏置,并且其中第二mos晶体管由第二电压栅极偏置,其中第二电压的电平比第一电压的电平更正。

[0083]

根据一个或多个实施例,其中升压电路包括:电容器,其第一端子被耦合到第一电荷转移晶体管和第二电荷转移晶体管的漏极端子;以及反相器电路,其输入被耦合来接收第二时钟信号并且输出被耦合到电容器的第二端子。

[0084]

根据一个或多个实施例,其中负自举电路包括:晶体管,具有与接地电压耦合的源极端子以及生成第一控制信号的漏极端子;电容器,具有与晶体管的漏极端子耦合的第一端子;以及反相器电路,具有被耦合来接收第一时钟信号的输入以及与电容器的第二端子耦合的输出。

[0085]

根据一个或多个实施例,其中正自举电路包括:晶体管,具有与输入电压耦合的源极端子以及生成第二控制信号的漏极端子;电容器,具有与晶体管的漏极端子耦合的第一端子;以及反相器电路,具有被耦合来接收第一时钟信号的输入以及与电容器的第二端子耦合的输出。

[0086]

本公开的另一方面提供了一种正电荷泵电路,被配置为从输入电压生成输出电压,其中输出电压的正电压电平比输入电压的电压电平更正,正电荷泵电路包括:负自举电路,被配置为响应于第一时钟信号而生成负电压;升压电路,被配置为响应于第二时钟信号而生成正升压电压;切换电路,被耦合来接收来自负自举电路的负电压并且接收来自升压

电路的正升压电压,并且被配置为在负电压与正升压电压之间切换控制信号;以及电荷转移晶体管,其漏极端子被耦合来接收正升压电压并且源极端子被耦合至输出节点,其中控制信号被施加到电荷转移晶体管的栅极端子,其中控制信号的负电压控制导通电荷转移晶体管,以将正升压电压传递到输出节点并且生成输出电压。

[0087]

本公开的一方面提供了一种负电荷泵电路,被配置为从输入电压生成输出电压,其中输出电压的负电压电平比输入电压的电压电平更负,负电荷泵电路包括:正自举电路,被配置为响应于第一时钟信号而生成正电压;升压电路,被配置为响应于第二时钟信号而生成负升压电压;切换电路,被耦合来接收来自正自举电路的正电压并且接收来自升压电路的负升压电压,并且被配置为在正电压与负升压电压之间切换控制信号;以及电荷转移晶体管,其漏极端子被耦合来接收负升压电压并且源极端子被耦合到输出节点,其中控制信号被施加到电荷转移晶体管的栅极端子,其中控制信号的正电压控制导通电荷转移晶体管,以将负升压电压传递到输出节点并且生成输出电压。

[0088]

本公开的又一方面提供了一种正电荷泵电路,被配置为从输入电压生成输出电压,其中输出电压的正电压电平比输入电压的电压电平更正,正电荷泵电路包括:负自举电路,被配置为响应于第一时钟信号而生成负电压;正自举电路,被配置为响应于第一时钟信号而生成正电压;升压电路,被配置为响应于第二时钟信号而生成正升压电压;切换电路,被耦合来接收来自负自举电路的负电压并且接收来自正自举电路的正电压,并且被配置为在负电压与正电压之间切换控制信号;以及电荷转移晶体管,其漏极端子被耦合来接收正升压电压并且源极端子被耦合至输出节点,其中控制信号被施加到电荷转移晶体管的栅极端子,其中控制信号的负电压控制导通电荷转移晶体管,以将正升压电压传递到输出节点并且生成输出电压。

[0089]

本公开的一方面提供了一种负电荷泵电路,被配置为从输入电压生成输出电压,其中输出电压的负电压电平比输入电压的电压电平更负,负电荷泵电路包括:正自举电路,被配置为响应于第一时钟信号而生成正电压;负自举电路,被配置为响应于第一时钟信号而生成负电压;升压电路,被配置为响应于第二时钟信号而生成负升压电压;切换电路,被耦合来接收来自正自举电路的正电压并且接收来自负自举电路的负电压,并且被配置为在正电压与负电压之间切换控制信号;以及电荷转移晶体管,其漏极端子被耦合来接收负升压电压并且源极端子被耦合到输出节点,其中控制信号被施加到电荷转移晶体管的栅极端子,其中控制信号的正电压控制导通电荷转移晶体管,以将负升压电压传递到输出节点并且生成输出电压。

[0090]

利用本公开的实施例有利地增加电荷转移开关晶体管的栅源电压来降低导通电阻。

附图说明

[0091]

为了更好地理解实施例,现在将仅以示例的方式参考附图,其中:

[0092]

图1a是正电荷泵电路的电路图;

[0093]

图1b是负电荷泵电路的电路图;

[0094]

图2a是正电荷泵电路的电路图;

[0095]

图2b图示了图2a的电路的操作波形;

[0096]

图3a是负电荷泵电路的电路图;

[0097]

图3b图示了图3a的电路的操作波形;

[0098]

图4a是正电荷泵电路的电路图;

[0099]

图4b图示了图4a的电路的操作波形;

[0100]

图4c示出了图4a的正电荷泵电路的更通用的电路配置;

[0101]

图5a是负电荷泵电路的电路图;

[0102]

图5b图示了图5a的电路的操作波形;

[0103]

图5c示出了图5a的负电荷泵电路的更通用的电路配置;

[0104]

图6a是正电荷泵电路的电路图;

[0105]

图6b图示了图6a的电路的操作波形;

[0106]

图6c示出了图6a的正电荷泵电路的更通用的电路配置;

[0107]

图7a是负电荷泵电路的电路图;

[0108]

图7b图示了图7a的电路的操作波形;以及

[0109]

图7c示出了图7a的负电荷泵电路的更通用的电路配置。

具体实施方式

[0110]

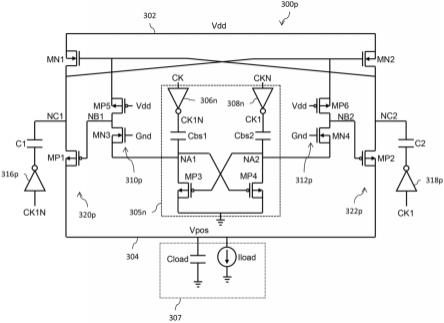

参考图4a,图4a示出了正电荷泵电路300p的电路图。电路300p 包括:n沟道mos晶体管mn1,其源极端子被耦合到电源节点302 并且漏极端子被耦合到中间节点nc1;以及n沟道mos晶体管mn2,其源极端子被耦合到电源节点302并且漏极端子被耦合到中间节点 nc2。利用以下方式将晶体管mn1与mn2交叉耦合:在节点nc2 处晶体管mn1的栅极端子耦合到晶体管mn2的漏极端子,并且在节点nc1处晶体管mn2的栅极端子耦合到晶体管mn1的漏极端子。电路300p还包括:p沟道mos晶体管mp1,其源极端子被耦合到输出节点304并且漏极端子被耦合到节点nc1;以及p沟道mos晶体管mp2,其源极端子被耦合到输出节点304并且漏极端子被耦合到中间节点nc2。晶体管mn1和mp1形成cmos切换电路320p,并且晶体管mn2和mp2形成cmos切换电路322p。

[0111]

正电荷泵电路300p还包括负自举电路305n,负自举电路305n包括:p沟道mos晶体管mp3,其源极端子被耦合到接地节点并且漏极端子被耦合到中间节点na1;以及p沟道mos晶体管mp4,其源极端子被耦合到接地节点并且漏极端子被耦合到中间节点na2。利用以下方式将晶体管mp3与mp4交叉耦合:在节点na2处晶体管mp3 的栅极端子耦合到晶体管mp4的漏极端子,并且在节点na1处晶体管mp4的栅极端子耦合到晶体管mp3的漏极端子。

[0112]

自举电容器cbs1的一个端子被耦合到节点na1并且另一端子被耦合来接收时钟信号ck的逻辑反相,该逻辑反相ck1n由cmos 反相器电路306n生成,cmos反相器电路306n由正电源电压vdd 供电并且接收时钟信号ck作为输入。自举电容器cbs2的一个端子被耦合到节点na2并且另一端子被耦合来接收时钟信号ckn的逻辑反相(这是时钟信号ck的逻辑反相),该逻辑反相ck1由cmos反相器电路308n生成,cmos反相器电路308n由正电源电压vdd供电并且接收时钟信号ckn作为输入。

[0113]

cmos切换电路310p的第一端子接收正电源电压vdd,第二端子被耦合来接收接地电压gnd并且第三端子位于中间节点nb1处。切换电路310p中的p沟道mos晶体管mp5的源极端子被耦合到 cmos切换电路320p中的晶体管mn1的栅极端子(即,中间节点 nc2),并且切

换电路310p中的n沟道mos晶体管mn3的源极端子被耦合到负自举电路305n的中间节点na1。第三端子在晶体管mp5 和mn3的共用漏极处,共用漏极被连接到cmos切换电路320p中的晶体管mp1的栅极端子。晶体管mp5的栅极被耦合到第一端子 (vdd)并且晶体管mn3的栅极被耦合到第二端子(gnd)。

[0114]

cmos切换电路312p的第一端子接收正电源电压vdd,第二端子被耦合来接收接地电压gnd并且第三端子位于中间节点nb2处。切换电路312p中的p沟道mos晶体管mp6的源极端子被耦合到 cmos切换电路322p中的晶体管mn2的栅极端子(即,中间节点 nc1),并且切换电路312p中的n沟道mos晶体管mn4的源极端子被耦合到负自举电路305n的中间节点na2。第三端子位于晶体管 mp6和mn4的共用漏极处。晶体管mp6的栅极被耦合到第一端子 (vdd)并且晶体管mn4的栅极被耦合到第二端子(gnd)。

[0115]

具有自举电路305n的电路310p和312p形成基于自举的电平移位电路。

[0116]

电容器c1的一个端子被耦合到节点nc1,并且另一端子被耦合来接收时钟信号ck1n的逻辑反相,该逻辑反相由cmos反相器电路316p生成,cmos反相器电路316p由正电源电压vdd供电并接收时钟信号ck1n作为输入。电容器c2的一个端子被耦合到节点nc2 并且另一端子被耦合来接收时钟信号ck1的逻辑反相,该逻辑反相由cmos反相器电路318p生成,cmos反相器电路318p由正电源电压vdd供电并且接收时钟信号ck1作为输入。

[0117]

电路300p的负载307由负载电容器cload示意性地表示,负载电容器cload具有与输出节点304耦合的一个端子以及与接地节点耦合的第二端子以及在输出节点304与接地节点之间耦合的电流源iload。

[0118]

电源节点302被配置为接收正电源电压vdd。输出节点304利用该正电荷泵电路300而被配置为相应地生成倍增的正输出电压vpos,其中vpos约为2*vdd。

[0119]

图4b示出了针对图4a的电路300p的操作的时钟信号ck、ckn、 ck1和ck1n以及节点na1、na2、nb1、nb2、nc1和nc2处的信号的波形。应注意,为了便于理解电路300p的操作,图4b波形中未示出信号传播延迟。将进一步注意到,时钟信号的电压电平是理想化的,并且在实现时,电压将基本上等于(例如,在1-20%内)但不一定等于理想的

±

vdd和2*vdd电压电平。

[0120]

由晶体管mp3、mp4、自举电容器cbs1、cbs2和反相器306n、 308n形成的电路装置是负自举电路,负自举电路响应于以电源vdd 和接地为基准的时钟信号ck、ckn运行,以在节点na1、na2处生成以-vdd和接地为基准的时钟信号。当时钟信号ckn为逻辑低 (gnd)时,由反相器308n输出的时钟信号ck1将为逻辑高(vdd)。晶体管mp4导通,这是因为节点na1借助电容器cbs1升高到-vdd 电压电平(即,因为晶体管mp4的栅极电压比源极端子的接地电压低vth以上而导通)并且自举电容器cbs2在节点na2处被充电到接地电压电平。在时钟信号的下一相位中,时钟信号ckn为逻辑高并且反相器308n输出的时钟信号ck1为逻辑低。晶体管m4关断,这是因为节点na1处于接地电压电平(即,因为晶体管mp4的栅极电压等于源极电压接地并且因此不超过vth而关断)并且节点na2处的电压借助电容器cbs2上存储的自举接地电压而升高到-vdd电压电平。响应于时钟信号ck和ck1n的相位,发生类似的过程。

[0121]

由电容器c1、c2和反相器316p、318p形成的电路装置响应于以电源vdd和接地为基准的时钟信号ck1、ck1n运行,以在节点nc1、 nc2处生成以2*vdd和vdd为基准的时钟信号。考虑与具有电容器 c1和反相器316p的电路有关的以下操作:当时钟信号ck1n为逻辑高时,反相器316p的输出为逻辑低。同时,如下所述,晶体管mn1 导通并且电容器c1被充电至vdd

电压电平。在时钟信号的下一相位中,时钟信号ck1n为逻辑低,并且反相器316p的输出为逻辑高。节点nc1处的电压借助电容器c1升高至2*vdd电压电平。响应于时钟信号ck1的相位,对于具有电容器c2和反相器318p的电路发生类似的过程。

[0122]

由cmos切换电路310p和312p形成的电路装置作为电平移位级,将节点na1、na2处以-vdd和接地为基准的时钟信号移位,以在节点nb1、nb2处生成以-vdd和+2*vdd为基准的时钟信号。考虑与电路312p的操作有关的以下内容:当节点na2接地时,晶体管mn4 关断(即,因为晶体管mn4的栅极电压等于源极电压接地并且因此不超过vth)。同时,节点nc1处的电压已通过反相器316p和电容器 c1响应于时钟ck1n的操作而升高到电压电平2*vdd。在这种情况下,晶体管mp6导通(即,因为晶体管mp6的栅极电压比源极端子低 vth以上)并且节点nb2处的电压被驱动到2*vdd。相反,当节点 na2处于-vdd时,晶体管mn4导通(即,因为晶体管mn4的栅极电压比源极端子低vth以上)并且节点nb2处的电压被驱动至-vdd。关于电路210p发生类似的过程。

[0123]

由cmos切换电路320p和322p形成的电路装置用作电荷转移驱动级,以将节点nc1、nc2处的2*vdd电压选择性地传递到输出节点304来驱动电容和电流负载307。考虑与电路322p的操作有关的以下内容:当由于晶体管mn2导通,节点nc2处的电压为vdd时,节点nb2处的电压为2*vdd。在这种情况下,晶体管mp2关断(即,因为晶体管mp2的栅极电压大于源极电压并且因此不超过vth)。当节点nc2处的电压升高至2*vdd时,节点nb2处的电压为-vdd,并且晶体管mp2导通(即,晶体管mp2的vgs超过vth),从而将节点 nc2处的2*vdd电压电平传递到输出节点304。响应于相反的相位,对于电路320p发生类似的过程。

[0124]

电路实现方式的一个优点是当栅极由-vdd驱动时,特别是结合晶体管mp1和mp2的操作时,增加了有关的电荷转移开关晶体管的vgs,以降低导通电阻(rds_on)。

[0125]

图4c中示出了图4a的正电荷泵电路300p的更通用的电路配置。电路300p被配置为增加电荷转移晶体管(开关)mp1和mp2的栅极

ꢀ‑

源极电压(vgs)来降低它们的“导通”电阻。负电压自举电路305n 在节点na1和na2处生成负电压(-vdd)。该电压响应于时钟电路生成的时钟信号而被选择性地切换来用于施加到晶体管mp1和mp2 的栅极端子,从而提供升压。在切换电路310p和312p的控制下,针对晶体管mp1和mp2的栅极驱动信号响应于时钟信号而在-vdd与 2*vdd之间交替。2*vdd的升压电压在节点nc1和nc2处生成并且在晶体管mp1和mp2的栅极端子被-vdd电压栅极偏置时,由晶体管 mp1和mp2通过。晶体管mp1和mp2在电荷转移相位期间的有效 vgs相应地为3*vdd,这导致显著降低的开关电阻。

[0126]

参考图5a,图5a示出了负电荷泵电路300n的电路图。电路300n 包括:p沟道mos晶体管mp1,其源极端子被耦合到电源节点302 并且漏极端子被耦合到中间节点nc1;以及p沟道mos晶体管mn2,其源极端子被耦合到电源节点302并且漏极端子被耦合到中间节点 nc2。利用以下方式将晶体管mp1与mp2交叉耦合:在节点nc2处晶体管mp1的栅极端子耦合到晶体管mp2的漏极端子,并且在节点 nc1处晶体管mp2的栅极端子耦合到晶体管mp1的漏极端子。电路 300n还包括:n沟道mos晶体管mn1,其源极端子被耦合到输出节点304并且漏极端子被耦合到节点nc1;以及n沟道mos晶体管 mn2,其源极端子被耦合到输出节点304并且漏极端子被耦合到中间节点nc2。晶体管mp1和mn1形成cmos切换电路320n,并且晶体管mp2和mn2形成cmos切换电路322n。

[0127]

负电荷泵电路300n还包括正自举电路305p,正自举电路305p包括:n沟道mos晶体

管mn3,其源极端子被耦合到电源电压节点vdd 并且漏极端子被耦合到中间节点na1;以及n沟道mos晶体管mn4,其源极端子被耦合到电源电压节点vdd并且漏极端子被耦合到中间节点na2。利用以下方式将晶体管mn3与mn4交叉耦合:在节点na2处晶体管mn3的栅极端子耦合到晶体管mn4的漏极端子,并且在节点na1处晶体管mn4的栅极端子耦合到晶体管mn3的漏极端子。

[0128]

自举电容器cbs1的一个端子被耦合到节点na1,并且另一端子被耦合来接收时钟信号ck的逻辑反相,该逻辑反相ck1n由cmos 反相器电路306p生成,cmos反相器电路306p由正电源电压vdd 供电并且接收时钟信号ck作为输入。自举电容器cbs2的一个端子被耦合到节点na2并且另一端子被耦合来接收时钟信号ckn的逻辑反相(这是时钟信号ck的逻辑反相),该逻辑反相ck1由cmos反相器电路308p生成,cmos反相器电路308p由正电源电压vdd供电并且接收时钟信号ckn作为输入。

[0129]

cmos切换电路310n具有被耦合来接收接地电压gnd的第一端子、被耦合来接收电源电压vdd的第二端子以及在中间节点nb1处的第三端子。切换电路310n中的n沟道mos晶体管mn5的源极端子被耦合到cmos切换电路320n中的晶体管mp1的栅极端子(即,中间节点nc2)并且切换电路310n中的p沟道mos晶体管mp3的源极端子被耦合到正自举电路305p的中间节点na1。第三端子在晶体管mn5和mp3的共用漏极处,共用漏极被连接到cmos切换电路320n中的晶体管mn1的栅极端子。晶体管mn5的栅极被耦合到第一端子(gnd),而晶体管mp3的栅极被耦合到第二端子(vdd)。

[0130]

cmos切换电路312n具有被耦合来接收接地电压gnd的第一端子、被耦合来接收电源电压vdd的第二端子以及在中间节点nb2处的第三端子。切换电路312n中的n沟道mos晶体管mn6的源极端子被耦合到cmos切换电路322n中的晶体管mp2的栅极端子(即,中间节点nc1)并且切换电路312n中的p沟道mos晶体管mp4中的源极端子被耦合到正自举电路305p的中间节点na2。第三端子位于晶体管mn6和mp4的共用漏极处。晶体管mn6的栅极被耦合到第一端子(gnd),而晶体管mp4的栅极被耦合到第二端子(vdd)。

[0131]

具有自举电路305p的电路310n和312n形成基于自举的电平移位电路。

[0132]

电容器c1的一个端子被耦合到节点nc1,并且另一端子被耦合来接收时钟信号ck1n的逻辑反相,该逻辑反相由cmos反相器电路316n生成,cmos反相器电路316n由正电源电压vdd供电并且接收时钟信号ck1n作为输入。电容器c2的一个端子被耦合到节点nc2 并且另一端子被耦合来接收时钟信号ck1的逻辑反相,该逻辑反相由cmos反相器电路318n生成,cmos反相器电路318n由正电源电压vdd供电并且接收时钟信号ck1作为输入。

[0133]

电路300n的负载307由负载电容器cload示意性地表示,负载电容器cload具有与输出节点304耦合的一个端子以及与接地节点耦合的第二端子以及在输出节点304和电源电压vdd之间耦合的电流源 iload。

[0134]

电源节点302被配置为接收接地电压vgnd。输出节点304利用该负电荷泵电路300配置来相应地生成倍增的负输出电压vneg,其中vneg近似为-vdd。

[0135]

图5b示出了针对图5a的电路300n的操作的时钟信号ck、ckn、 ck1和ck1n以及节点na1、na2、nb1、nb2、nc1和nc2处的信号的波形。应注意,为了便于理解电路300n的操作,图5b波形中未示出信号传播延迟。将进一步注意到,时钟信号的电压电平是理想化的,并且在实现时,电压将基本上等于(例如,在1-20%内)但不一定等于理想的

±

vdd和2*vdd电压电平。

[0136]

由晶体管mn3、mn4、自举电容器cbs1、cbs2和反相器306p、 308p形成的电路装置是正自举电路,正自举电路响应于以电源vdd 和接地为基准的时钟信号ck、ckn运行,以在节点na1、na2处生成以2*vdd和vdd为基准的时钟信号。当时钟信号ck为逻辑高 (vdd)时,反相器306p输出的时钟信号ck1n将为逻辑低(gnd)。晶体管mn3导通,这是因为节点na2借助电容器cbs2升高到2*vdd 电压电平(即,因为晶体管mn3的栅极电压在源极端子处超过vdd 多于vth而导通)并且自举电容器cbs1被充电到vdd电压电平。在时钟信号的下一相位中,时钟信号ck为逻辑低并且反相器306p输出的时钟信号ck1n为逻辑高。晶体管mn3关断,这是因为节点na2 处于vdd电压电平(即,因为晶体管mn1的栅极电压等于源极电压 vdd并且因此不超过vth而关断),并且节点na1处的电压借助电容器cbs1上存储的自举电压vdd而升高到2*vdd电压电平。响应于时钟信号ckn和ck1的相位,发生类似的过程。

[0137]

由电容器c1、c2和反相器316n、318n形成的电路装置响应于以电源vdd和接地为基准的时钟信号ck1、ck1n运行,以在节点nc1、 nc2处生成以-vdd和接地为基准的时钟信号。考虑与具有电容器c2 和反相器318n的电路有关的以下操作:当时钟信号ck1为逻辑低时,反相器318n的输出为逻辑高。同时,如下所述,晶体管mp2导通并且电容器c2被放电至接地电压电平。在时钟信号的下一相位中,时钟信号ck1为逻辑高并且反相器318n的输出为逻辑低。节点nc2 处的电压借助电容器c2升高至-vdd电压电平。响应于时钟信号 ck1n的相位,具有电容器c1和反相器316n的电路发生类似的过程。

[0138]

由cmos切换电路310n和312n形成的电路装置用作电平移位级,将节点na1、na2处以vdd和+2*vdd为基准的时钟信号移位,从而在节点nb1、nb2处生成以-vdd和+2*vdd为基准的时钟信号。考虑与电路312n的操作有关的以下内容:当节点na2处于vdd时,晶体管mp4被关断(即,因为晶体管mp4的栅极电压等于源极电压并且因此不超过vth)。同时,节点nc1处的电压已通过反相器316n和电容器c1响应于时钟ck1n的操作而升高到电压电平-vdd。在这种情况下,晶体管mn6导通(即,因为晶体管mp6的栅极电压比源极端子低vth以上)并且节点nb2处的电压被驱动到-vdd。相反,当节点na2处于2*vdd时,晶体管mp4导通(即,因为晶体管mp4的栅极电压比源极端子低vth以上)并且节点nb2处的电压被驱动到 2*vdd。对于电路310n发生类似的过程。

[0139]

由cmos切换电路320n和322n形成的电路装置用作电荷转移驱动级,以将节点nc1、nc2处的-vdd电压选择性地传递到输出节点304来驱动电容和电流负载307。考虑以下关于电路322n的操作:当节点nc2处的电压由于晶体管mp2导通而处于接地gnd时,节点 nb2处的电压处于-vdd。在这种情况下,晶体管mn2关断(即,因为晶体管mn2的栅极电压不超过vth)。当节点nc2的电压升高至

ꢀ‑

vdd时,节点nb2处的电压为2*vdd,并且晶体管mn2导通(即,晶体管mn2的vgs超过vth),以将节点nc2处的-vdd电压电平传递到输出节点304。响应于相反的相位,对于电路320n发生类似的过程。

[0140]

电路实现方式的一个优点是当栅极由+2*vdd驱动时,特别是结合晶体管mn1和mn2的操作,增加了电荷转移开关晶体管的vgs,以降低导通电阻(rds_on)。

[0141]

图5c中示出了图5a的负电荷泵电路300n的更通用的电路配置。电路300n被配置为增加电荷转移晶体管(开关)mn1和mn2的栅源电压(vgs)来降低它们的“导通”电阻。正电压自举电路305p在节点na1和na2处生成正电压(2*vdd)。该电压响应于时钟电路生成的时钟信号而被选择性地切换,以施加到晶体管mn1和mn2的栅极端子来提供升压。针对晶体管mn1

和mn2的栅极驱动信号在切换电路310n和312n的控制下在-vdd与2*vdd之间交替。-vdd的升压电压在节点nc1和nc2处生成,并且在晶体管mn1和mn2的栅极端子被2*vdd电压栅极偏置时,通过晶体管mn1和mn2。晶体管 mn1和mn2在电荷转移相位期间的有效vgs相应地为3*vdd,这导致显著降低的开关电阻。

[0142]

参考图6a,图6a示出了正电荷泵电路400p的电路图。电路400p 包括:n沟道mos晶体管mn1,其源极端子被耦合到电源节点402 并且漏极端子被耦合到中间节点nc1;以及n沟道mos晶体管mn2,其源极端子被耦合到电源节点402并且漏极端子被耦合到中间节点 nc2。电路400p还包括:p沟道mos晶体管mp1,其源极端子被耦合到输出节点404并且漏极端子被耦合到节点nc1;以及p沟道mos 晶体管mp2,其源极端子被耦合到输出节点404并且漏极端子被耦合到中间节点nc2。晶体管mn1与mp1的栅极被耦合到节点nd1,并且晶体管mn2与mp2的栅极被耦合到节点nd2。晶体管mn1和 mp1形成cmos切换电路420p,并且晶体管mn2和mp2形成cmos 切换电路422p。

[0143]

正电荷泵电路400p还包括正自举电路405p,正自举电路405p包括:n沟道mos晶体管mn3,其源极端子被耦合到电源电压节点vdd 并且漏极端子被耦合到中间节点na1;以及n沟道mos晶体管mn4,其源极端子被耦合到电源电压节点vdd并且漏极端子被耦合到中间节点na2。利用以下方式将晶体管mn3与mn4交叉耦合:在节点 na2处晶体管mn3的栅极端子耦合到晶体管mn4的漏极端子,并且在节点na1处晶体管mn4的栅极端子耦合到晶体管mn3的漏极端子。

[0144]

自举电容器cbs1的一个端子被耦合到节点na1,并且另一端子被耦合来接收时钟信号ck的逻辑反相,该逻辑反相ck1n由cmos 反相器电路406生成,cmos反相器电路406由正电源电压vdd供电并且接收时钟信号ck作为输入。自举电容器cbs2的一个端子被耦合到节点na2并且另一端子被耦合来接收时钟信号ckn的逻辑反相 (它是时钟信号ck的逻辑反相),该逻辑反相ck1由cmos反相器电路408生成,cmos反相器电路408由正电源电压vdd供电并接收时钟信号ckn作为输入。

[0145]

正电荷泵电路400p还包括负自举电路405n,负自举电路405n包括:p沟道mos晶体管mp3,其源极端子被耦合到接地节点并且漏极端子被耦合到中间节点nb1;以及p沟道mos晶体管mp4,其源极端子被耦合到接地节点并且漏极端子被耦合到中间节点nb2。利用以下方式将晶体管mp3与mp4交叉耦合:在节点nb2处晶体管mp3 的栅极端子耦合到晶体管mp4的漏极端子,并且在节点nb1处晶体管mp4的栅极端子耦合到晶体管mp3的漏极端子。

[0146]

自举电容器cbs3的一个端子被耦合到节点nb1并且另一端子被耦合来接收由cmos反相器电路406生成的时钟信号ck的逻辑反相。自举电容器cbs4的一个端子被耦合到节点nb2并且另一端子被耦合来接收由cmos反相电路408生成的时钟信号ckn的逻辑反相。

[0147]

cmos切换电路410p的第一端子被耦合来接收正电源电压vdd,第二端子被耦合来接收接地电压gnd并且第三端子位于中间节点 nd1处。切换电路410p中的p沟道mos晶体管mp5的源极端子在正自举电路405p的输出处被耦合到节点na1,并且切换电路410p 中的n沟道mos晶体管mn5的源极端子在负自举电路405n的输出处被耦合到中间节点nb1。第三端子在晶体管mp5和mn5的共用漏极处,共用漏极被连接到cmos切换电路420p中的晶体管mp1和 mn1的栅极端子。晶体管mp5的栅极被耦合至第一端子(vdd),而晶体管mn5的栅极被耦合至第二端子(gnd)。

[0148]

cmos切换电路412p的第一端子被耦合以接收正电源电压vdd,第二端子被耦合以接收接地电压gnd,并且第三端子位于中间节点 nd2处。切换电路412p中的p沟道mos晶体管mp6的源极端子在正自举电路405p的输出处被耦合到节点na2,并且切换电路412p 中的n沟道mos晶体管mn6的源极端子在负自举电路405n的输出处被耦合到中间节点nb2。第三端子在晶体管mp6和mn6的共用漏极处,共用漏极被连接到cmos切换电路422p中的晶体管mp2和 mn2的栅极端子。晶体管mp6的栅极被耦合到第一端子(vdd),而晶体管mn6的栅极被耦合到第二端子(gnd)。

[0149]

具有自举电路405p和405n的电路410p和412p形成基于自举的电平移位电路。

[0150]

电容器c1的一个端子被耦合到节点nc1并且另一端子被耦合来接收时钟信号ck1n的逻辑反相,该逻辑反相由cmos反相器电路 416p生成,cmos反相器电路416p由正电源电压vdd供电并且接收时钟信号ck1n作为输入。电容器c2的一个端子被耦合到节点nc2 并且另一端子被耦合来接收时钟信号ck1的逻辑反相,该逻辑反相由cmos反相器电路418p生成,cmos反相器电路418p由正电源电压vdd供电并接收时钟信号ck1作为输入。

[0151]

电路400p的负载407由负载电容器cload示意性地表示,负载电容器cload具有与输出节点404耦合的一个端子以及与接地节点耦合的第二端子以及在输出节点404与接地节点之间耦合的电流源 iload。

[0152]

电源节点402被配置为接收正电源电压vdd。输出节点404利用该正电荷泵电路400p来配置,以相应地生成倍增的正输出电压vpos,其中vpos约为2*vdd。

[0153]

图6b示出了针对图6a的电路400p的操作的时钟信号ck、ckn、 ck1和ck1n以及节点na1、na2、nb1、nb2、nd1、nd2、nc1 和nc2处的信号的波形。应注意,为了便于理解电路400p的操作,图6b波形中未示出信号传播延迟。将进一步注意到,时钟信号的电压电平是理想化的,并且在实现时,电压将基本上等于(例如,在1-20%内)但不一定等于理想的

±

vdd和2*vdd电压电平。

[0154]

由电路410p和412p与自举电路405p和405n形成的基于自举的电平移位电路装置操作为在节点nd1和nd2处生成在-vdd电压电平与+2*vdd电压电平之间切换的相应时钟信号。具体地,正自举电路 405p操作为在节点na1与na2处(以本文别处详细描述的方式)生成在vdd电压电平与2*vdd电压电平之间切换的时钟信号。电路410p 和412p的晶体管mp5和mp6分别响应于2*vdd电压电平而导通并且将该电压传递到节点nd1和nd2。负自举电路405n操作为在节点 nb1和nb2处(以本文别处详细描述的方式)生成在-vdd电压电平与接地电压电平之间切换的时钟信号。电路410p和412p的晶体管 mn5和mn6分别响应于-vdd电压电平而导通并且将该电压传递到节点nd1和nd2。

[0155]

由电容器c1、c2和反相器416p、418p形成的电路装置响应于以电源vdd和接地为基准的时钟信号ck1、ck1n运行,以在节点nc1、 nc2处生成以2*vdd和vdd为基准的时钟信号。考虑与具有电容器 c1和反相器416p的电路有关的以下操作:当时钟信号ck1n为逻辑高时,反相器416p的输出为逻辑低。同时,晶体管mn1被节点nd1 处的2*vdd电压电平导通,并且电容器c1被充电至vdd电压电平。在时钟信号的下一相位中,时钟信号ck1n为逻辑低,并且反相器 416p的输出为逻辑高。节点nc1处的电压借助电容器c1升压至 2*vdd电压电平。响应于时钟信号ck1的相位,对于具有电容器c2 和反相器318p的电路发生类似的过程。

[0156]

当节点nc1和nc2处的电压分别处于升高的2*vdd电压电平时,电荷转移晶体管mp1

和mp2响应于节点nd1和nd2处的-vdd电压电平,从而将该电压传递到输出节点404。

[0157]

电路实现方式的一个优点是当栅极由-vdd驱动时,特别是结合晶体管mp1和mp2的操作,增加了电荷转移开关晶体管的vgs,从而降低导通电阻(rds_on)。

[0158]

图6c中示出了针对图6a的正电荷泵电路400p的更通用的电路配置。电路400p被配置为增加电荷转移晶体管(开关)mp1和mp2 的栅源电压(vgs)来降低它们的“导通”电阻。负电压自举电路405n 在节点nb1和nb2处生成负电压(-vdd)并且正电压自举电路405p 在节点na1和na2处生成正电压(2*vdd)。这些电压响应于由时钟电路生成的时钟信号而被选择性地切换,从而施加到晶体管mn1、 mn2、mp1和mp2的共用栅极端子。具体地,-vdd电压为晶体管 mp1和mp2提供升压。在切换电路410p和412p的控制下,晶体管 mp1和mp2的栅极驱动信号响应于时钟信号而在-vdd与2*vdd之间交替。2*vdd的升压电压在节点nc1和nc2处生成,并且在晶体管 mp1和mp2的栅极端子被-vdd电压栅极偏置时,由晶体管mp1和 mp2通过。晶体管mp1和mp2在电荷转移相位期间的有效vgs相应地为3*vdd,这导致显著降低的开关电阻。

[0159]

参考图7a,图7a示出了负电荷泵电路400n的电路图。电路400n 包括:p沟道mos晶体管mp1,其源极端子被耦合到电源节点402 并且漏极端子被耦合到中间节点nc1;以及p沟道mos晶体管mp2,其源极端子被耦合到电源节点402并且漏极端子被耦合到中间节点 nc2。电路400n还包括:n沟道mos晶体管mn1,其源极端子被耦合到输出节点404并且漏极端子被耦合到节点nc1;以及n沟道mos 晶体管mn2,其源极端子被耦合到输出节点404并且漏极端子被耦合到中间节点nc2。晶体管mn1与mp1的栅极被耦合到节点nd1,并且晶体管mn2与mp2的栅极被耦合到节点nd2。晶体管mn1和 mp1形成cmos切换电路420n,并且晶体管mn2和mp2形成cmos 切换电路422n。

[0160]

负电荷泵电路400n还包括正自举电路405p,正自举电路405p包括:n沟道mos晶体管mn3,其源极端子被耦合到电源电压节点vdd 并且漏极端子被耦合到中间节点na1;以及n沟道mos晶体管mn4,其源极端子被耦合到电源电压节点vdd并且漏极端子被耦合到中间节点na2。晶体管mn3和mn4在节点na2处与耦合到晶体管mn4 的漏极端子的晶体管mn3的栅极端子交叉耦合并且在节点na1处与耦合到晶体管mn3的漏极端子的晶体管mn4的栅极端子交叉耦合。

[0161]

自举电容器cbs1的一个端子被耦合到节点na1,并且另一端子被耦合来接收时钟信号ck的逻辑反相,该逻辑反相ck1n由cmos 反相器电路406生成,cmos反相器电路406由正电源电压vdd供电并接收时钟信号ck作为输入。自举电容器cbs2的一个端子被耦合到节点na2并且另一端子被耦合来接收时钟信号ckn的逻辑反相 (它是时钟信号ck的逻辑反相),该逻辑反相ck1由cmos反相器电路408生成,cmos反相器电路408由正电源电压vdd供电并接收时钟信号ckn作为输入。

[0162]

负电荷泵电路400n还包括负自举电路405n,负自举电路405n包括:p沟道mos晶体管mp3,其源极端子被耦合到接地节点并且漏极端子被耦合到中间节点nb1;以及p沟道mos晶体管mp4,其源极端子被耦合到接地节点并且漏极端子被耦合到中间节点nb2。利用以下方式将晶体管mp3与mp4交叉耦合:在节点nb2处晶体管mp3 的栅极端子耦合到晶体管mp4的漏极端子,并且在节点nb1处晶体管mp4的栅极端子耦合到晶体管mp3的漏极端子。

[0163]

自举电容器cbs3的一个端子被耦合到节点nb1并且另一端子被耦合来接收由cmos

反相器电路406生成的时钟信号ck的逻辑反相。自举电容器cbs4的一个端子被耦合到节点nb2并且另一端子被耦合来接收由cmos反相电路408生成的时钟信号ckn的逻辑反相。

[0164]

cmos切换电路410n的第一端子被耦合来接收正电源电压vdd、第二端子被耦合来接收接地电压gnd并且第三端子位于中间节点 nd1处。切换电路410p中的p沟道mos晶体管mp5的源极端子在正自举电路405p的输出处被耦合到节点na1,并且切换电路410p 中的n沟道mos晶体管mn5的源极端子在负自举电路405n的输出处被耦合到中间节点nb1。第三端子在晶体管mp5和mn5的共用漏极处,共用漏极被连接到cmos切换电路420n中的晶体管mp1和 mn1的栅极端子。晶体管mp5的栅极被耦合到第一端子(vdd),而晶体管mn5的栅极被耦合到第二端子(gnd)。

[0165]

cmos切换电路412n的第一端子被耦合来接收正电源电压vdd,第二端子被耦合来接收接地电压gnd并且第三端子位于中间节点 nd2处。切换电路412n中的p沟道mos晶体管mp6的源极端子在正自举电路405p的输出处被耦合到节点na2,并且切换电路412p 中的n沟道mos晶体管mn6的源极端子在负自举电路405n的输出处被耦合到中间节点nb2。第三端子在晶体管mp6和mn6的共用漏极处,共用漏极被连接到cmos切换电路422n中的晶体管mp2和 mn2的栅极端子。晶体管mp6的栅极被耦合到第一端子(vdd),而晶体管mn6的栅极被耦合到第二端子(gnd)。

[0166]

具有自举电路405p和405n的电路410n和412n形成基于自举的电平移位电路。

[0167]

电容器c1的一个端子被耦合到节点nc1,并且另一端子被耦合来接收时钟信号ck1n的逻辑反相,该逻辑反相由cmos反相器电路416n生成,cmos反相器电路416n由正电源电压vdd供电并接收时钟信号ck1n作为输入。电容器c2的一个端子被耦合到节点nc2 并且另一端子被耦合来接收时钟信号ck1的逻辑反相,该逻辑反相由cmos反相器电路418n生成,cmos反相器电路418n由正电源电压vdd供电并接收时钟信号ck1作为输入。

[0168]

电路400n的负载407由负载电容器cload示意性地表示,负载电容器cload具有与输出节点404耦合的一个端子以及与接地节点耦合的第二端子以及在输出节点404和电源节点vdd之间耦合的电流源 iload。

[0169]

电源节点402被配置为接收接地电压vgnd。输出节点404利用该负电荷泵电路400n来配置,以相应地生成倍增的负输出电压vneg,其中vneg近似为-vdd。

[0170]

图7b示出了针对图7a的电路400n的操作的时钟信号ck、ckn、 ck1和ck1n以及节点na1、na2、nb1、nb2、nd1、nd2、nc1 和nc2处的信号的波形。应注意,为了便于理解电路400n的操作,图7b波形中未示出信号传播延迟。将进一步注意到,时钟信号的电压电平是理想化的,并且在实现时,电压将基本上等于(例如,在1-20%内)但不一定等于理想的

±

vdd和2*vdd电压电平。

[0171]

由电路410n和412n与自举电路405p和405n形成的基于自举的电平移位电路装置操作为在节点nd1和nd2处生成在-vdd电压电平和+2*vdd电压电平之间切换的相应时钟信号。具体地,正自举电路 405p操作为在节点na1和na2处(以本文别处详细描述的方式)生成在vdd电压电平与2*vdd电压电平之间切换的时钟信号。电路410n 和412n的晶体管mp5和mp6分别响应于2*vdd电压电平而导通并且将该电压传递到节点nd1和nd2。负自举电路405n操作为在节点 nb1和nb2处(以本文别处详细描述的方式)生成在-vdd电压电平与接地电压电平之间切换的时钟信号。电路410n和412n的晶体管 mn5和mn6分别响应于-vdd电压电平

而导通并将该电压传递到节点 nd1和nd2。

[0172]

由电容器c1、c2和反相器416n、418n形成的电路装置响应于以电源vdd和接地为基准的时钟信号ck1、ck1n运行,以在节点nc1、 nc2处生成以-vdd和接地为基准的时钟信号。考虑与具有电容器c1 和反相器416n的电路有关的以下操作:当时钟信号ck1n为逻辑低时,反相器416n的输出为逻辑高。同时,晶体管mp1被节点nd1 处的-vdd电压电平导通并且电容器c1被充电到接地电压电平。在时钟信号的下一相位中,时钟信号ck1n为逻辑高,并且反相器416n 的输出为逻辑低。节点nc1处的电压借助电容器c1升高至-vdd电压电平。响应于时钟信号ck1的相位,对于具有电容器c2和反相器 418n的电路发生类似的过程。

[0173]

当节点nc1和nc2处的电压分别处于升高的-vdd电压电平时,电荷转移晶体管mn1和mn2响应节点nd1和nd2处的+2*vdd电压电平,以将该电压传递到输出节点404。

[0174]

电路实现方式的一个优点是当栅极由2*vdd驱动时,特别是结合晶体管mn1和mn2的操作,增加了电荷转移开关晶体管的vgs,以降低导通电阻(rds_on)。

[0175]

图7c中示出了针对图7a的负电荷泵电路400n的更通用的电路配置。电路400n被配置为增加电荷转移晶体管(开关)mn1和mn2 的栅源电压(vgs)来降低它们的“导通”电阻。负电压自举电路405n 在节点nb1和nb2处生成负电压(-vdd)并且正电压自举电路405p 在节点na1和na2处生成正电压(2*vdd)。这些电压响应于时钟电路生成的时钟信号而被选择性地切换,以施加到晶体管mn1、mn2、 mp1和mp2的共用栅极端子。具体地,2*vdd电压为晶体管mn1和 mn2提供升压。在切换电路410n和412n的控制下,晶体管mn1和 mn2的栅极驱动信号响应于时钟信号而在-vdd与2*vdd之间交替。当晶体管mn1和mn2的栅极端子被2*vdd电压栅极偏置时,在节点nc1和nc2处生成的-vdd的升压电压由晶体管mn1和mn2传递。晶体管mn1和mn2在电荷转移相位期间的有效vgs相应地为3*vdd,这导致显著降低的开关电阻。

[0176]

在一个实施例中,正电荷泵电路被配置为从输入电压生成输出电压,其中输出电压的正电压电平比输入电压的电压电平更正。正电荷泵电路包括:负自举电路,被配置为响应于第一时钟信号而生成控制信号,其中控制信号在接地电压与负电压之间切换;升压电路,被配置为响应于第二时钟信号而生成正升压电压;以及电荷转移晶体管,其漏极端子被耦合来接收所述正升压电压并且源极端子被耦合至输出节点,其中电荷转移晶体管的栅极端子被控制信号的负电压偏置而导通并且将正升压电压传递至输出节点并生成所述输出电压。

[0177]

在一个实施例中,负电荷泵电路被配置为从输入电压生成输出电压,其中输出电压的负电压电平比输入电压的电压电平更负。负电荷泵电路包括:正自举电路,被配置为响应于第一时钟信号而生成控制信号,其中控制信号在第一正电压与第二正电压之间切换,其中第二正电压的电压电平比第一正电压的电压电平更正;升压电路,被配置为响应于第二时钟信号而生成负升压电压;以及电荷转移晶体管,其漏极端子被耦合来接收所述负升压电压并且源极端子被耦合至输出节点,其中电荷转移晶体管的栅极端子被控制信号的第二正电压偏置而导通并且将负升压电压传递至输出节点并且生成所述输出电压。

[0178]

在一个实施例中,正电荷泵电路被配置为从输入电压生成输出电压,其中输出电压的正电压电平比输入电压的电压电平更正。正电荷泵电路包括:负自举电路,被配置为响应于第一时钟信号而生成第一控制信号,其中第一控制信号在接地电压与负电压之间切换;正自举电路,被配置为响应于所述第一时钟信号而生成第二控制信号,其中第二控制信

号在第一正电压与第二正电压之间切换,其中第二正电压的电压电平比第一正电压的电压电平更正;升压电路,被配置为响应于第二时钟信号而在中间节点处生成正升压电压;第一电荷转移晶体管,其漏极端子被耦合至所述中间节点并且源极端子被耦合至输入电压,其中第一电荷转移晶体管的栅极端子被第二控制信号的第二正电压栅极偏置而导通从而支持升压电路;以及第二电荷转移晶体管,其漏极端子被耦合至所述中间节点并且源极端子被耦合至输出节点,其中第二电荷转移晶体管的栅极端子被第一控制信号的负电压栅极偏置而导通并且将正升压电压传递到输出节点并且生成所述输出电压。

[0179]

在一个实施例中,负电荷泵电路被配置为从输入电压生成输出电压,其中输出电压的负电压电平比输入电压的电压电平更负。负电荷泵电路包括:负自举电路,被配置为响应于第一时钟信号而生成第一控制信号,其中第一控制信号在接地电压与负电压之间切换;正自举电路,被配置为响应于所述第一时钟信号而生成第二控制信号,其中第二控制信号在第一正电压与第二正电压之间切换,其中第二正电压的电压电平比第一正电压的电压电平更正;升压电路,被配置为响应于第二时钟信号而在中间节点处生成负升压电压;第一电荷转移晶体管,其漏极端子被耦合到所述中间节点,并且源极端子被耦合至输入电压,其中第一电荷转移晶体管的栅极端子被第一控制信号的负电压栅极偏置而导通从而支持升压电路;以及第二电荷转移晶体管,其漏极端子被耦合至所述中间节点并且源极端子被耦合至输出节点,其中第二电荷转移晶体管的栅极端子被第二控制信号的第二正电压栅极偏置而导通并且将负升压电压传递至输出节点并且生成所述输出电压。

[0180]

前面的描述已通过示例性和非限制性示例的方式提供了对本实用新型示例性实施例的完整和翔实的描述。然而,当结合附图和所附权利要求阅读时,鉴于上述描述,相关领域的技术人员可以清楚地了解各种修改和变化。然而,本实用新型教导的所有此类和类似修改仍将落入如所附权利要求所限定的本实用新型范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1