一种不加反并联续流二极管的全SiC功率模块的制作方法

一种不加反并联续流二极管的全sic功率模块

技术领域

1.本实用新型涉及芯片技术,特指功率模块。

背景技术:

2.智能功率模块是以igbt为内核的先进混合集成功率部件,由高速低功耗管芯(igbt)和优化的门极驱动电路,以及快速保护电路构成。ipm内部集成了能连续检测igbt电流和温度的实时检测电路,当发生严重过载甚至直接短路时,以及温度过热时,igbt将被有控制地软关断,同时发出故障信号。目前市场上功率模块基本都是由si基功率芯片或si基功率芯片和sic功率芯片混合封装而成,由于si基igbt芯片本身特征的限制,必须并联一续流的肖特基二极管才能正常工作,如图1所示,每个igbt芯片1`并联续流二极管2`,mos管体二极管导通电阻较大,采用mos管体二极管续流将带来额外的损耗,影响着模块整体的成本、尺寸及散热。

技术实现要素:

3.本实用新型的目的在于提供一种低模块成本、高模块功率密度、工艺制程简单、模块成品率高的不加反并联续流二极管功率模块。

4.为达成上述目的,本实用新型一种不加反并联续流二极管的全sic功率模块,在dbc模板上设有两个并设的模组,在每个模组上均设有两组mosfet并联组和一组sic sdb并联组,其中,所述的每组mosfet并联组由七片额定电压1200v、额定电流40a的sic mosfet裸片并联组成,每个sic mosfet并联组电路由门极和体二极管组成;sic sdb并联组由5片额定电压1200v、额定电流50a的sic sdb裸片并联,两组sic mosfet并联组和sic sdb并联组分别连接dbc外接电路端子。

5.采用上述方案后,本实用新型模块采用全sic芯片,且采用的sic mos管不另外再并联续流二极管方式;全sic功率模块与传统的si基igbt模块相比损耗降低30%以上,最高工作温度与si基igbt模块相比提高25℃以上,同时降低了全sic模块的材料成本,使得整体成本与增加反并联续流二极管的全sic功率模块相比降低30%以上。

附图说明

6.图1为现有dbc基板拓扑图;

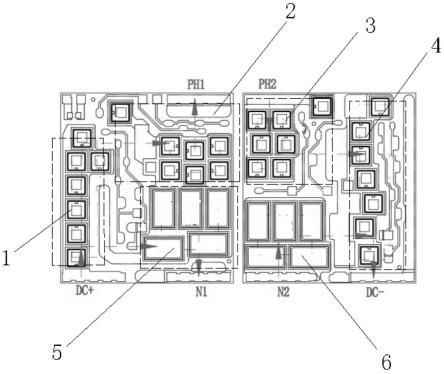

7.图2为本实用新型结构示意图;

8.图3为本实用新型npc三电平拓扑结构;

9.图4为本实用新型npc三电平拓扑在双脉冲测试条件下的开关过程示意图(一);

10.图5为本实用新型npc三电平拓扑在双脉冲测试条件下的开关过程示意图(二);

11.图6为本实用新型npc三电平拓扑在双脉冲测试条件下的开关过程示意图(三)。

具体实施方式

12.为详细说明本实用新型的技术内容、构造特征、所实现目的及效果,以下结合实施方式并配合附图详予说明。

13.如图2所示,在dbc模板并排设置左右两块模组,左侧模组设有两组sic mosfet并联组m1与m2(附图中虚线框标记1、2),在右侧模组设有两组sic mosfet并联组m3与m4(附图中虚线框标记3、4),每个模组上分别设有一sic sbd并联组d1与d2(附图中虚线框标记5、6)。为满足整个模块额定工作电压1000v,额定工作电流200a的技术指标,每组mos管采用7片的sic mosfet(额定电压1200v,额定电流40a)裸片并联;每组二极管采用5片sic sdb(额定电压1200v,额定电流50a)裸片并联。

14.如图2所示,dc+、ph1、ph2、n1、n2、dc-皆为dbc接端子区域,电流走势为:

15.dc+

→

m1

→

m2和d1

→

ph1和n1

→

ph2和n2

→

m3和d2

→

m4

→

dc-。

16.ph1和ph2在外接电路实现相连,n1和n2在外接电路实现相连,共同组成模块功率回路。

17.如图3所示本实用新型dbc基板拓扑图,四组sic mosfet并联组m1、m2、m3、m4由门极11和体二极管12组成,利用sic mos管自身的体二极管进行续流,由于相比于并联肖特基二极管,mos管体二极管导通电阻较大,单单采用mos管体二极管续流将带来额外的损耗,致使系统效率降低,本实用新型通过模块应用端配合调节,优化mos管的续流时间,在保证系统正常运行的前提下,减小系统损耗,提升系统效率。对于传统的igbt+sic sbd来说,整个续流阶段,电流均从sbd流过,在此阶段产生的损耗为:il*vd1,其中:il为负载电流,vd1为sbd管压降。对于sic mosfet来说,在续流的初始阶段,电流从其体二极管流过,产生的损耗为:il*vd2,其中:il为负载电流,vd2为体二极管管压降。sic mosfet体二极管的压降大于sic sbd的压降,因此,在续流初始阶段,sic mosfet的损耗偏大。在续流阶段后期,通过调节mosfet门极驱动信号,开通mosfet,利用mosfet导电通道进行续流,此时,产生的损耗为:il2*rds(on),其中:rds(on)为sic mosfet的导通内阻。由于sic mosfet导通内阻较小(不大于0.1欧姆),因此,系统的损耗也相应减小。

18.图4-6为npc三电平拓扑在双脉冲测试条件下的开关过程,(a)状态c,(b)状态4,(c)状态4-》状态6,(d)状态6,(e)状态2,(f)状态2-》状态3,(g)状态3,(h)状态3-》状态2,(i)状态2,(j)状态6,(k)状态6-》状态4,(l)状态4。

19.状态c:t0~t1

20.在t0~t1时间段,m1、m2开通,m3、m4关断,npc拓扑的等效电路如图4(a)所示。此时,负载电流通过m1、m2续流,ac端电压为vdc+。

21.状态4:t1~t2

22.在t1~t2时间段,m2开通,m3、m4关断,m1由开通变为关断,npc拓扑的等效电路如图4(b)所示。此时,负载电流通过m2及m1的体二极管续流,ac端电压保持为vdc+。

23.状态4——》状态6:t2~δt2

24.在t2~δt2时间段,m2开通,m1、m4关断,m3由关断变为开通,npc拓扑的等效电路如图4(c)所示。在m3开通过程中,负载电流由m2及m1的体二极管向m3转移,ac端电压由vdc+变为0。由于sic mosfet开关速度较快,在电路寄生参数的作用下,ac端电压在此过程中会产生较为明显的振荡。

25.状态6:δt2~t3

26.在δt2~t3时间段,m2、m3开通,m1、m4关断,npc拓扑的等效电路如图4(d)所示。此时,负载电流回路为:dc+—》m3—》m4—》dc-。需要注意到:尽管m2处于开通状态,但是流过其导电沟道的电流为0。

27.状态2:t3~t4

28.在t3~t4时间段,m3开通,m1、m4关断,m2由开通变为关断,npc拓扑的等效电路如图5(e)所示。此时,负载电流回路为:dc+—》m3—》d2—》0,ac端电压保持为0。

29.状态2——》状态3:t4~δt4

30.在t4~δt4时间段,m3开通,m1、m2关断,m4由关断变为开通,npc拓扑的等效电路如图5(f)所示。在m4开通过程中,负载电流由钳位二极管d2向m4转移,ac端电压由0变为vdc-。由于sic mosfet开关速度较快,在电路寄生参数的作用下,ac端电压在此过程中会产生较为明显的振荡。

31.状态3:δt4~t5

32.在δt4~t5时间段,m3、m4开通,m1、m2关断,npc拓扑的等效电路如图5(g)所示。此时,负载电流回路为:dc+—》m3—》m4—》dc-,ac端电压保持为vdc-。

33.状态3——》状态2:t5~δt5

34.在t5~δt5时间段,m3开通,m1、m2关断,m4由开通变为关断,npc拓扑的等效电路如图5(h)所示。在m4关断过程中,负载电流由m4向钳位二极管d2转移,ac端电压由vdc-变为0。由于sic mosfet开关速度较快,在电路寄生参数的作用下,ac端电压在此过程中会产生较为明显的振荡。

35.状态2:δt5~t6

36.在δt5~t6时间段,m3开通,m1、m2、m4关断,npc拓扑的等效电路如图6(i)所示。此时,负载电流回路为:dc+—》m3—》d2—》0,ac端电压保持为0。

37.状态6:t6~t7

38.在t6~t7时间段,m3开通,m1、m4关断,m2由关断变为开通,npc拓扑的等效电路如图6(j)所示。此时,负载电流回路为:dc+—》m3—》d2—》0,ac端电压保持为0。需注意到:尽管m2处于开通状态,但是流过其导电沟道的电流为0。

39.状态6——》状态4:t7~δt7

40.在t7~δt7时间段,m2开通,m1、m4关断,m3由开通变为关断,npc拓扑的等效电路如图6(k)所示。在m3关断过程中,负载电流由m3向m2及m1的体二极管转移,ac端电压由0变为vdc+。由于sic mosfet开关速度较快,在电路寄生参数的作用下,ac端电压在此过程中会产生较为明显的振荡。

41.状态4:δt7~t8

42.在δt7~t8时间段,m2开通,m1、m3、m4关断,npc拓扑的等效电路如图6(l)所示。此时,负载电流通过m2及m1的体二极管续流,ac端电压保持为vdc+。

43.在上述应用过程中,为保证系统效率,本实用新型减少状态4:t1~t2的作用时间,在保证电路正常工作的情况下,缩短续流时间。

44.以上所述仅为本实用新型的实施例,并非因此限制本实用新型的专利范围,凡是利用本实用新型说明书及附图内容所作的等效形状或结构变换,或直接或间接运用在其他

相关的技术领域,均同理包括在本实用新型的专利保护范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1