一种带有端口短路检测的整流桥驱动电路的制作方法

1.本发明属于模拟集成电路技术领域,具体的说是涉及一种带有端口短路检测的整流桥驱动电路。

背景技术:

2.如图1所示,为全nmos型h桥及相应的控制和驱动电路框图示意。其中,m1、m2、m3和m4分别为构成整流h桥的四个nmos型功率管,控制逻辑(control logic)通过对电感两端的sw1和sw2信号进行处理,产生hson1、hson2、lson1和lson2信号(分别为m1导通信号、m2导通信号、m3导通信号和m4导通信号,且这些信号都是高电平有效),并通过驱动电路(driver)分别产生m1、m2、m3、m4的驱动信号hg1、hg2、lg1、lg2。c1为boot1电压的自举电容,c2为boot2电压的自举电容,d1和d2为二极管,图中有三个不同电压:vin、boot1/boot2和avdd。因为电感l1在芯片外部,通过sw1和sw2连接到芯片内,sw1和sw2可能因为意外原因被短路到地,此时m1或者m2导通,将会有大电流流过功率管m1和m2,烧毁芯片。因此需要设计相关保护电路来应对这种情况。

3.当sw因意外情况短接(如制造、应用中的短接)到gnd时,而此时整流h桥的hg1/hg2(以nmos h桥高侧驱动管为例,其栅极电压为hg1、hg2)为高电平,整流桥的电源电压将通过高侧驱动管的小电阻(mω级别)接到地,大电流将直接通过高侧驱动管,烧毁驱动管和芯片。当h桥正常工作,而boot掉电(短路),或者当boot还在上电的过程中,此时电路的hg将处于高阻态,h桥高侧驱动管的cgs和cgd在sw ring的过程中(例如sw为低电平)将对h桥电源电压有分压作用,在hg有部分电压降,将会引起此高侧驱动管导通,带来大电流问题,而且hg上的电压和高阻也将带来大电流的问题,严重影响功率管的正常工作和芯片的效率。目前虽然也有解决的方法,但是通常比较复杂且不易实现,成本高。

技术实现要素:

4.针对上述问题,本发明提出了一种带有端口短路检测的整流桥驱动电路,当sw短接到地时,迅速将hg拉到低电平,并产生一个hs short信号用以关闭相关电路,起到保护h桥,保护芯片的目的,同时本发明还提出了掉电保护功能。

5.本发明的技术方案是:

6.一种带有端口短路检测的整流桥驱动电路,所述整流桥包括第一功率管、第二功率管、第三功率管、第四功率管,所述驱动电路包括控制逻辑单元和驱动单元;其中第一功率管和第二功率管为上管,第三功率管和第四功率管为下管,第一功率管的漏极接输入电压,其源极接第三功率管的漏极,第一功率管的栅极接第一驱动信号;第二功率管的漏极接输入电压,其源极接第四功率管的漏极,第二功率管的栅极接第二驱动信号;第三功率管的栅极接第三驱动信号,其源极接地,第四功率管的栅极接第四驱动信号,其源极接地;将第一功率管与第三功率管的连接点定义为第一端口,第二功率管与第四功率管的连接点定义为第二端口,所述第一端口和第二端口直接连接有电感;第一端口通过第一电容后接第一

自举电压,第二端口通过第二电容后接第二自举电压,模拟电源电压通过第一二极管后接第一电容,模拟电源电压通过第二二极管后接第二电容;所述逻辑控制单元的输入端接第一端口和第二端口,逻辑控制单元输出第一功率管导通信号、第二功率管导通信号、第三功率管导通信号和第四功率管导通信号到驱动单元,驱动单元根据接收到的导通信号产生第一驱动信号、第二驱动信号、第三驱动信号和第四驱动信号;其特征在于,所述驱动电路还包括端口短路检测模块;

7.所述端口短路检测模块包括第一电平转换模块、第二电平转换模块、第一反相器、第二反相器、第三反相器、第四反相器、第五反相器、第六反相器、第七反相器、第八反相器、第九反相器、第十反相器、第十一反相器、第十二反相器、第十三反相器、第十四反相器、第十五反相器、第十六反相器、第十七反相器、第十八反相器、第十九反相器、第一与非门、第二与非门第、第三与非门、第四与非门第、第五与非门、第六与非门、第七与非门、第八与非门、第九与非门、第一nmos管、第二nmos管、第三nmos管、第四nmos管、第五nmos管、第一pmos管、第一电阻、第二电阻、第三电阻和缓冲器;

8.将第一功率管导通信号和第二功率管导通信号定义为上管导通信号,将第一功率管驱动信号和第二功率管驱动信号定义为上管驱动信号,则上管通过信号通过串联的第一反相器和第二反相器后接第一电平转换模块的输入端和第七与非门的一个输入端,第一电平转换模块的输出端接第二电平转换模块的输入端,第二电平转换模块的输出端接第一与非门的一个输入端和第六与非门的一个输入端,第六与非门的另一个输入端接第五与非门的输出端,第六与非门的输出端接第一与非门的另一个输入端;第五与非门的一个输入端接第六与非门的输出端,第五与非门的另一个输入端接第十五反相器的输出端,第十五反相器的输入端接第十四反相器的输出端,第十四反相器的输入端通过第二电阻后接自举电压,所述自举电压为第一自举电压或第二自举电压;第四nmos管的漏极通过第二电阻后接自举电压,其栅极接第二nmos管的源极,第四nmos管的源极接端口电压,所述端口电压为第一端口电压或第二端口电压;第二nmos管的漏极接输入电压,其栅极接第十三反相器的输出端;第三nmos管的漏极接第二nmos管的源极,第三nmos管的栅极接第四与非门的输出的,其源极接端口电压;第十三反相器的输入端接第四与非门的输出端,第四与非门的一个输入端接第九反相器的输出端,第四与非门的另一个输入端接第三反相器的输出端,第三反相器的输入端接第一与非门的输出端;第八反相器和第九反相器串联,第八反相器的输入端接第七反相器的输出端;第四反相器、第五反相器、第六反相器、第七反相器依次串联,第四反相器的输入端接第三反相器的输出端,第七反相器的输出端接缓冲器的输入端,缓冲器的输出端接第二与非门的一个输入端,第二与非门的另一个输入端接第六与非门的输出端,第二与非门的输出端接第三与非门的一个输入端,第三与非门的另一个输入端接第四反相器的输出端,第三与非门的输出端接第十反相器的输入端;第十反相器、第十一反相器、第十二反相器依次串联,第十反相器的输入端还通过第一电阻后接端口电压,第十二反相器的输出端接第一nmos管的栅极,第一nmos管的源极接端口电压,第一nmos管的漏极和第七反相器输出端连接后输出上管驱动信号;

9.第十六反相器和第十七反相器串联,第十六反相器的输入端接第六与非门的输出端,第十七反相器的输出端接第五nmos管的漏极;第五nmos管的栅极接模拟电源电压,其源极接第十八反相器的输入端,第十八反相器的输出端接第七与非门的另一个输入端;第一

pmos管的源极接模拟电源电压,其栅极接第十八反相器的输出端,其漏极接第五nmos管的源极,第一pmos管的源极和漏极之间还练级有第三电阻;第七与非门的输出端接第八与非门的一个输入端,第八与非门的另一个输入端接第九与非门的输出端,第九与非门的一个输入端接第八与非门的输出端,第九与非门的另一个输入端接短路信号,所述短路信号为第六与非门输出信号取反后的信号;第九与非门的输出端接第十九反相器的输入端,第十九反相器的输出端输出端口短路标记信号,所述端口短路标记信号用于反馈逻辑控制单元端口是否处于短路状态。

10.进一步的,还包括掉电保护模块,所述掉电保护模块包括第二pmos管、第三pmos管、第四pmos管、第六nmos管、第七nmos管、第八nmos管、第九nmos管、第四电阻和第五电阻;所述第二pmos管的源极接端口电压,其栅极与漏极互连;所述第三pmos管的源极接上管驱动信号,其栅极接第二pmos管的漏极;所述第四pmos管的源极接上管驱动信号,其栅极接端口电压;所述第八nmos管的漏极接第三pmos管的漏极和第四pmos管的漏极,第八nmos管的栅极接欠压保护信号,其源极接地;第九nmos管的漏极接第二pmos管的漏极,第九nmos管的栅极接欠压保护信号,其源极通过第五电阻后接地;所述第六nmos管的漏极通过第四电阻后接上管驱动信号,其栅极接第三与非门的输出端,其源极接端口电压;所述第七nmos管的漏极接上管驱动信号,其栅极接第六nmos管的漏极,第七nmos管的源极接端口信号;所述欠压保护信号为在电源电压低于正常工作电压时为低电平。

11.进一步的,所述端口短路检测模块用于在端口短路到地时,第五与非门输出高电平,第二电平转换模块输出高电平,此时通过第一与非门和第三反相器将低电平信号发送到上管驱动信号,从而关闭上管。

12.进一步的,当端口短路到地时,还将第六与非门输出的低电平信号通过第十六反相器和第十七反相器传递到第七与非门,从而使第九与非门输出低电平,使得端口短路标记信号为高,将端口短路的信息传递到逻辑控制模块。

13.进一步的,所述第一电平转换模块和第二电平转换模块用于将模拟电源电压到地的电压域转换为自举电压到端口电源的电压域。

14.本发明的有益效果是:本发明通过逻辑电路将sw短路到地的信号反馈到控制信号,把高侧驱动信号拉低,同时将高侧驱动管短路的信号送到其他控制电路,进行锁存;通过在boot掉电或者启动过程中,将高侧驱动信号钳位在sw附近,从而保证高侧功率管的关断状态,保证功率管关断的同时,提高效率。本发明的电路具有结构简单,成本低,易实现的优点。

附图说明

15.图1为全nmos型h桥及相应的控制和驱动电路框图示意。

16.图2为本发明的端口短路到地的检测保护电路。

17.图3为本发明的掉电保护电路示意图。

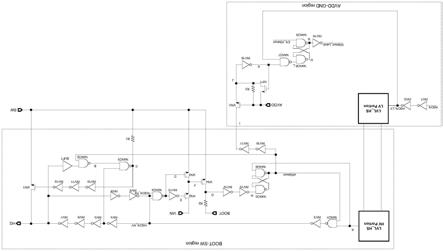

18.图4为本发明的同时带有sw到地短路检测功能的掉电保护驱动电路图。

具体实施方式

19.下面结合附图对本发明进行详细的描述。

20.在发明内容部分已经对本发明的具体电路结构进行了详细描述,下面主要对从原理方面对本发明进行说明。

21.图2所示为本发明的sw短路到地的检测保护电路部分。因为h桥的m1、m2两个功率管都有可能出现sw短路到地的情况,所以每个高侧功率管都有对应的本发明的sw短路到地的检测保护电路。其中的hg指的是图1所示的m1/m2的栅极驱动电压信号,boot指的是图1所示的boot1/boot2电压信号,sw指的是sw1/sw2电压信号,而hson信号也指的是hson1/hson2信号。图2中上半部分虚线内的器件模块所在的电压域为boot-sw电压域,下半部分中虚线内的器件模块的电压域为avdd-gnd电压域。其中的lvl_hs lv portion和lvl_hs hv portion构成电平转换模块,将原来的avdd-gnd电压域向boot-sw电压域转换,而从这个电平转换模块输入的信号只是发生了电平转换,并没有逻辑的变化,例如输入的hson_lv信号原来为高电平(avdd),经过这个模块之后,输出的信号a仍为高电平(boot电压)。

22.图2中所示的inv(反相器)后面的数字仅仅作序号用,不作驱动能力表示,同理,nand(与非门)、r(电阻)、mn(nmos管)、mp(pmos管)和buf(缓冲器)后面的数字也仅作序号用,没有其它含义。图2中所示的器件连接导线上的字母即代表相应的导线上的电压。图2中所示的hson_lv信号表示低电压域的高侧功率管导通信号,为1代表导通信号,为0代表关断信号(这里以1为高电平导通信号,0为低电平关断信号,在boot-sw电压域和avdd-gnd电压域及其他电压域均为相应高低电平),同理hson_hv信号表示高电压域的高侧功率管导通信号;en_hsshort信号为控制模块发送过来的信号,sw短路到地发生时,为高电平信号,短路状态解除后,会通过控制模块先产生低电平信号进行reset,再产生高电平,开始正常工作;inv19输出的信号hsshort_latch表示高侧驱动管短路标志信号,高电平有效,此信号用于为控制模块提供高侧驱动管短路信号,控制模块将锁存此信号并控制相应模块关闭以保护芯片,等待短路状态解除再恢复正常控制逻辑;xhsshort表示高侧功率管sw短路到地的信号。

23.芯片正常工作时,前一个状态上管关闭,hson=0,hson_lv=0,a=0,通过nand6,输出信号xhsshort=1,en_hsshort=1,hsshort_latch=0,表示没有发生sw短路到地的情况。于是,hson_hv=0,d=1,e=0,f被拉到sw电位,mn4关断,g=1,h=1;同时hson_hv的低电平信号通过inv4反相之后传到nand3,而此时b=1,则c=0,mn1的栅极为高电平,mn1导通,hg被拉到和sw相同电位。

24.当高侧功率管导通信号到来时,即hson=1,hson_lv=1,a=1,此时xhsshort=1,hson_hv=1,hg=1,高侧功率管导通,vin电压和sw端电压相等。相应地,hson_fb=1,nand4输出为低电平,即d=0,e=1,mn2导通,f端电压被拉到vin电压,mn4的栅源电压相同,mn4保持关断,g=1,h=1,xhsshort保持为高电平。

25.此时,如果发生sw端被短路到地的情况,由于hg=1,即高侧功率管为导通状态,则vin被直接拉到地,产生大电流,烧毁芯片。在这种情况下,本发明的驱动电路可以提供保护作用:当sw电位被拉到地,mn4导通,g=0,h=0,nand5输出高电平,此时a=1,则xhsshort=0,通过nand1和inv3这条通路迅速把低电平信号传到hg,即hson_hv=0,hg=0,关掉高侧功率管,保护芯片。同时,hson_fb=0,nand4输出为高电平,即d=1,e=0,f=0,mn4关断,g=1,h=1,nand5保持输出高电平,xhsshort保持低电平。而此时b=1,则c=0,mn1的栅极为高电平,mn1导通,hg再次被拉到和sw相同电位,保证hg不会因意外的glitch信号被拉为高电

平。

26.同时,sw短路到地的信息,即xhsshort=0将通过inv16和inv17传到下面的支路,此时i变为0,j=0,k=1,和hson_lv的高电平一起经过nand7输出低电平,即l=0,m=1,和en_hsshort的高电平一起经过nand9输出低电平,即n=0,hsshort_latch=1,hsshort_latch的高电平信号将被送到控制逻辑电路进行处理,从而保证芯片在sw短路到地这段时间不会产生其他错误的逻辑信号。

27.当sw短路到地的情况解除,由于f=0,mn4保持关断,g=1,h=1,xhsshort的低电平信号保持。同时,控制电路检测到sw短路到地的情况已经解除之后,会将en_hsshort信号reset掉,即先让en_hsshort=0,n=1,hsshort_latch=0,再产生高电平的en_hsshort信号,恢复sw短路到地检测输出的功能,并通过控制逻辑恢复其他电路。同时,i=0,j=0,k=1,l=0,m=1,hsshort_latch将被锁存在低电平,直到sw短路到地的情况再次发生才改变。

28.如图3所示,为boot掉电保护电路。当电源电压低于正常工作电压,发生uvlo时,图3中的uvlo信号为高电平,mn8和mn9导通,此时,如果sw点有电压,为了保护功率管,通过mp2和mp3组成的电流镜会将hg点的电荷泄放到地,把hg点的电压拉到地,并以mp4做辅助管进行强下拉,保证高侧功率管在uvlo时处于关闭状态;而当芯片正常上电以后,uvlo为低电平,而boot掉电(短路),或者当boot还在上电的过程中,此时电路的hg将处于高阻态,c≠1,mn6关闭,mn7通过r4构成二极管连接,此时hg被钳位到比sw高一个mn7的vgs7的电压处,而通过下面的mp2、mp3和mp4,也会把hg钳位到比sw高一个mp4的vgs4的电压,通过两个钳位电路,把hg钳位到sw附近,使得高侧功率管处于关断状态,避免启动过程中,或者boot掉电过程中的大电流问题,保证功率管的正常工作和芯片的效率。

29.图4为本发明的整个带有sw到地短路检测功能的掉电保护驱动电路图。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1