具有有源钳位器的同步整流栅极驱动器的制作方法

具有有源钳位器的同步整流栅极驱动器

1.本技术是申请日为2018年12月26日、中国国家申请号为201811605309.8、发明名称为“具有有源钳位器的同步整流栅极驱动器”的发明专利申请的分案申请。

技术领域

2.本公开针对用于谐振转换器和其他拓扑的同步整流驱动器。

背景技术:

3.一般地,谐振转换器将具有第一电压电平的输入电压转换成具有第二电压电平的输出电压,并且调节用于负载的输出电压。谐振转换器通常被用于为电子设备(诸如用于电视、计算机和移动设备的显示器)供电。谐振转换器是高效的,并且对于具有功率限制的应用(诸如电池操作的设备)已经变得越来越普及了。

4.许多谐振转换器包括整流器,整流器利用多个晶体管以将交流(ac)信号转换成直流(dc)信号。电压尖峰通常被生成在晶体管的漏极上,并且有时可能损坏谐振转换器。这些电压尖峰可能由于各种原因引起,诸如由于整流器的延迟关断以及谐振转换器高于谐振的操作导致的电流反转以及晶体管的体二极管恢复时间。

技术实现要素:

5.本公开针对包括同步整流驱动器的谐振转换器。同步整流驱动器通过在晶体管的漏极与谐振转换器的输出端子之间放置有源钳位器来减小在谐振转换器内的晶体管的漏极上的电压尖峰。有源钳位器通过将在晶体管的漏极处的电流吸收到谐振转换器的输出端子来减少电压尖峰。附加地,通过将电流吸收到输出端子,功率损耗被最小化,并且谐振转换器的效率得到改善。

6.根据一个实施例,谐振转换器包括输入端子、输出端子、开关网络、谐振回路、变压器、整流器、以及输出电容器。开关网络是半桥,半桥在输出端子处接收输入电压,使用输入电压生成方波,并且将方波提供给谐振回路。谐振回路接收由开关网络所生成的方波信号,并且基于方波信号来生成交流(ac)信号。变压器在变压器的初级侧上接收来自谐振回路的ac信号,并且将ac信号传递到变压器的次级侧。整流器从变压器的次级侧接收信号,将ac信号转换成直流(dc)信号,并且将dc信号提供给输出电容器。输出电容器被电耦合到输出端子。输出电容器确保输出电压保持稳定、并且针对负载被适当调节。

7.根据一个实施例,整流器包括第一晶体管、第二晶体管、以及具有有源钳位器的同步整流驱动器。同步整流驱动器包括:第一输入,第一输入被电耦合到第一晶体管的漏极;第二输入,第二输入被电耦合到第二晶体管的漏极;第一输出,第一输出被电耦合到第一晶体管的栅极;第二输出,第二输出被电耦合到第二晶体管的栅极;以及第三输出,第三输出被电耦合到输出电容器。有源钳位器通过吸收在晶体管的漏极处的电流来将整流器内的晶体管的漏极上的电压限制到期望的值。有源钳位器恢复并且使用钳位电流,以对输出电容器充电。

8.根据一个实施例,有源钳位器包括第一二极管、第二二极管、第三二极管、第四二极管、晶体管、第一电阻器、第二电阻器、以及电容器。第三二极管、第四二极管以及晶体管形成钳位模块,该钳位模块实施了有源钳位器电路,以用于在整流器的晶体管的漏极处吸收钳位电流。第一二极管、第二二极管、第一电阻器、第二电阻器、以及电容器形成阈值设定模块,该阈值设定模块设定用于钳位模块的阈值。

9.根据一个实施例,钳位模块利用达林顿mosfet(darlington mosfet)配置来增加有源钳位器的干预时间。在该实施例中,钳位模块包括晶体管、齐纳二极管、以及第三电阻器。

10.根据一个实施例,阈值设定模块利用驱动模块代替,驱动模块被配置为动态激活钳位模块。驱动模块包括二极管、电容器和驱动器。

11.根据一个实施例,钳位模块包括p沟道金属氧化物半导体场效应晶体管(mosfet),并且阈值设定模块被去除。在该实施例中,钳位模块由外部电压动态激活。

12.根据各种实施例,提供了谐振转换器包括:整流器,包括:第一晶体管,具有漏极、栅极和源极,上述第一晶体管的源极被接地;第一驱动器,被配置为向上述第一晶体管的栅极提供第一驱动信号;以及有源钳位器,被配置为从上述第一晶体管的漏极接收第一电流,并且基于上述第一电流来输出第二电流;以及第一电容器,被配置为接收上述第二电流。

13.根据各种实施例的谐振转换器,其中上述整流器包括:第二晶体管,具有漏极、栅极和源极,上述第二晶体管的源极被接地;以及第二驱动器,被配置为向上述第二晶体管的栅极提供第二驱动信号。

14.根据各种实施例的谐振转换器,其中上述有源钳位器被配置为从上述第二晶体管的漏极接收第三电流,并且基于上述第三电流来输出第四电流,以及上述第一电容器被配置为接收上述第四电流。

15.根据各种实施例的谐振转换器,其中上述有源钳位器包括:第一二极管,被电耦合到上述第一晶体管的漏极;以及第二晶体管,具有漏极、栅极和源极,上述第二晶体管的漏极被电耦合到上述第一二极管,上述第二晶体管的源极被电耦合到上述第一电容器。

16.根据各种实施例的谐振转换器,其中上述有源钳位器包括:第二二极管,被电耦合到上述第一晶体管的漏极;电阻器,被电耦合到上述第二二极管以及上述第二晶体管的栅极;以及第二电容器,被电耦合到上述第二二极管。

17.根据各种实施例的谐振转换器,其中上述有源钳位器包括:第二二极管,被电耦合到上述第二晶体管的栅极以及上述第一电容器;电阻器,被电耦合到上述第二晶体管的栅极以及上述第一电容器;以及第三晶体管,具有漏极、栅极和源极,上述第三晶体管的漏极被电耦合到上述第一二极管,上述第三晶体管的源极被电耦合到上述第一电容器。

18.根据各种实施例的谐振转换器,其中上述第二二极管是齐纳二极管。

19.根据各种实施例的谐振转换器,其中上述有源钳位器包括:第二二极管,被电耦合到上述第二晶体管的源极以及上述第二晶体管的栅极;第二电容器,被电耦合到上述第二晶体管的栅极;以及第二驱动器,被电耦合到上述第二电容器。

20.根据各种实施例的谐振转换器,其中上述有源钳位器包括:第一二极管,被电耦合到上述第一晶体管的漏极;以及第二晶体管,具有漏极、栅极和源极,上述第二晶体管的源极被电耦合到上述第一二极管,上述第二晶体管的栅极被电耦合到外部信号,上述第二晶

体管的漏极被电耦合到上述第一电容器。

21.根据各种实施例,提供了一种整流器,包括:第一晶体管,具有漏极、栅极和源极,上述第一晶体管的源极被接地;第二晶体管,具有漏极、栅极和源极,上述第二晶体管的源极被接地;第一驱动器,其在操作中向上述第一晶体管的栅极提供第一驱动信号;第二驱动器,其在操作中向上述第二晶体管的栅极提供第二驱动信号;以及有源钳位器,包括:输出端子;第一输入端子,被电耦合到上述第一晶体管的漏极,上述有源钳位器在操作中经由上述第一输入端子接收来自上述第一晶体管的漏极的第一电流,并且向上述输出端子提供基于上述第一电流的第二电流;第二输入端子,被电耦合到上述第二晶体管的漏极,上述有源钳位器在操作中经由上述第二输入端子接收来自上述第二晶体管的漏极的第三电流,并且向上述输出端子提供基于上述第三电流的第四电流。

22.根据各种实施例的整流器,其中上述有源钳位器包括:第一二极管,被电耦合到上述第一输入端子;第二二极管,被电耦合到上述第二输入端子;以及第三晶体管,具有漏极、栅极和源极,上述第三晶体管的漏极被电耦合到上述第一二极管和上述第二二极管,上述第三晶体管的源极被电耦合到上述输出端子。

23.根据各种实施例的整流器,其中上述有源钳位器包括:第三二极管,被电耦合到上述第一输入端子;第四二极管,被电耦合到上述第二输入端子;以及电阻器,被电耦合到上述第三二极管、上述第四二极管、以及上述第三晶体管的栅极;以及电容器,被电耦合到上述第三二极管和上述第四二极管。

24.根据各种实施例的整流器,其中上述有源钳位器包括:第三二极管,被电耦合到上述第三晶体管的栅极以及上述输出端子;电阻器,被电耦合到上述第三晶体管的栅极以及上述输出端子;以及第四晶体管,具有漏极、栅极和源极,上述第四晶体管的漏极被电耦合到上述第一二极管和上述第二二极管,上述第三晶体管的源极被电耦合到上述输出端子。

25.根据各种实施例的整流器,其中上述第三二极管是齐纳二极管。

26.根据各种实施例的整流器,其中上述有源钳位器包括:第三二极管,被电耦合到上述第三晶体管的源极以及上述第三晶体管的栅极;电容器,被电耦合到上述第三晶体管的栅极;以及第三驱动器,被电耦合到上述电容器。

27.根据各种实施例的整流器,其中上述有源钳位器包括:第三输入端子;第一二极管,被电耦合到上述第一输入端子;以及第二二极管,被电耦合到上述第二输入端子;以及第三晶体管,具有漏极、栅极和源极,上述第三晶体管的源极被电耦合到上述第一二极管,上述第三晶体管的栅极被电耦合到上述第三输入端子,上述第三晶体管的漏极被电耦合到上述输出端子。

28.根据各种实施例,提供了一种设备,包括:第一晶体管,具有漏极、栅极和源极,上述第一晶体管的源极被接地;第二晶体管,具有漏极、栅极和源极,上述第二晶体管的源极被接地;第一驱动器,被配置为向上述第一晶体管的栅极提供第一驱动信号;第二驱动器,被配置为向上述第二晶体管的栅极提供第二驱动信号;第一二极管,被电耦合到上述第一晶体管的漏极;第二二极管,被电耦合到上述第二晶体管的漏极;以及第三晶体管,具有漏极、栅极和源极,上述第三晶体管的漏极被电耦合到上述第一二极管和上述第二二极管,上述第三晶体管的源极被电耦合到上述设备的输出端子。

29.根据各种实施例的设备,还包括:第三二极管,被电耦合到上述第一晶体管的漏

极;第四二极管,被电耦合到上述第二晶体管的漏极;以及电阻器,被电耦合到上述第三二极管、上述第四二极管、以及上述第三晶体管的栅极;以及电容器,被电耦合到上述第三二极管和上述第四二极管。

30.根据各种实施例的设备,还包括:第三二极管,被电耦合到上述第三晶体管的栅极以及上述设备的输出端子;电阻器,被电耦合到上述第三晶体管的栅极以及上述设备的输出端子;以及第四晶体管,具有漏极、栅极和源极,上述第四晶体管的漏极被电耦合到上述第一二极管和上述第二二极管,上述第四晶体管的源极被电耦合到上述设备的输出端子。

31.根据各种实施例的设备,还包括:第三二极管,被电耦合到上述第三晶体管的源极以及上述第三晶体管的栅极;电容器,被电耦合到上述第三晶体管的栅极;以及第三驱动器,被电耦合到上述电容器。

32.根据各种实施例,提供了一种设备,包括:第一晶体管,具有漏极、栅极和源极,上述第一晶体管的源极被接地;第二晶体管,具有漏极、栅极和源极,上述第二晶体管的源极被接地;第一驱动器,被配置为向上述第一晶体管的栅极提供第一驱动信号;第二驱动器,被配置为向上述第二晶体管的栅极提供第二驱动信号;第一二极管,被电耦合到上述第一晶体管的漏极;第二二极管,被电耦合到上述第二晶体管的漏极;第三晶体管,具有漏极、栅极和源极,上述第三晶体管的漏极被电耦合到上述第一二极管和上述第二二极管,上述第三晶体管的源极被电耦合到上述设备的输出端子;第三二极管,被电耦合到上述第一晶体管的漏极;第四二极管,被电耦合到上述第二晶体管的漏极;以及第一电阻器,被电耦合到上述第三二极管、上述第四二极管、以及上述第三晶体管的栅极;以及电容器,被电耦合到上述第三二极管和上述第四二极管。

33.根据各种实施例的设备,还包括:第二电阻器,被电耦合到上述第二电阻器。

34.根据各种实施例的设备,还包括:变压器,上述变压器被耦合在上述第一晶体管的漏极与上述第二晶体管的漏极之间。

附图说明

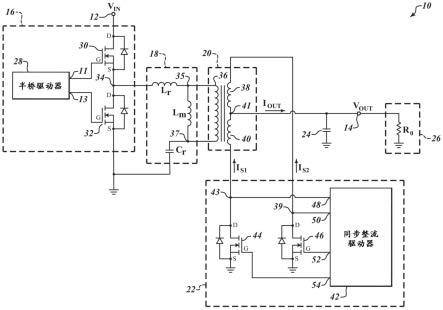

35.图1示出了根据在本文中所公开的一个实施例的谐振转换器的示图。

36.图2示出了根据在本文中所公开的一个实施例的、包括具有有源钳位器的同步整流驱动器的谐振转换器的示图。

37.图3示出了根据在本文中所公开的第一实施例的有源钳位器的详细示图。

38.图4示出了根据在本文中所公开的第二实施例的有源钳位器的详细示图。

39.图5示出了根据在本文中所公开的第三实施例的有源钳位器的详细示图。

40.图6示出了根据在本文中所公开的一个实施例的、图5的有源钳位器的波形的示图。

41.图7示出了根据在本文中所公开的第四实施例的有源钳位器的详细示图。

具体实施方式

42.在以下描述中,阐述了某些具体细节,以便提供对本公开的各种实施例的透彻理解。然而,本领域技术人员将理解,可以在没有这些具体细节的情况下实践本公开。在一些实例中,没有描述与谐振转换器、整流器、以及各种电子组件(诸如,变压器、晶体管、二极

管、电容器、以及电感器)相关联的公知细节,以避免模糊本公开的实施例的描述。

43.贯穿本说明书中对于“一个实施例”或者“实施例”的引用意味着结合实施例所描述的特定特征、结构或特点被包括在至少一个实施例中。因此,贯穿本说明书在各处出现的短语“在一个实施例中”或者“在实施例中”不一定全部指代同一实施例。此外,特定特征、结构或特点可以在一个或多个实施例中以任何合适的方式组合。

44.在附图中,相同的附图标记标识相似的特征或元件。附图中特征的尺寸和相对位置不必按比例绘制。

45.图1示出了根据在本文中所公开的一个实施例的谐振转换器10的示图。谐振转换器10包括输入端子12、输出端子14、开关网络16、谐振回路18、变压器20、整流器22、以及输出电容器24。

46.谐振转换器10在输入端子12处接收输入电压v

in

,并且在输出端子14处调节输出电压v

out

。谐振转换器10调节用于负载26的输出电压v

out

。负载26由图1中的电阻器ro表示。负载26可以是任何由谐振转换器10供电的任何电子设备。

47.谐振转换器10的输入-输出增益是基于谐振转换器10的直接传递功能的模块。由于谐振转换器10包括多谐振电抗电路,因此谐振转换器10即使在低负载下也能够提供有限的增益。

48.谐振转换器10使用电路电容和电感的谐振来实现软开关。特别地,谐振转换器10的特征在于在谐振转换器10的初级侧(即,如图1所示的变压器20的左侧)上的零电压开关(zvs),以及在谐振转换器10的次级侧(即,如图1所示的变压器20的右侧)上的零电流开关(zcs)。通过使用zvs和zcs,谐振转换器10能够以高效率在高开关频率下操作。

49.开关网络16被耦合到谐振回路18。开关网络16包括半桥驱动器28和晶体管30、32。在一个实施例中,如图1所示,晶体管30、32是金属氧化物半导体场效应晶体管(mosfet)。半桥驱动器28具有第一输出11和第二输出13。第一输出11被电耦合到晶体管30的栅极,而第二输出13被电耦合到晶体管32的栅极。晶体管30的漏极被电耦合到输入端子12。晶体管30的源极和晶体管32的漏极彼此电耦合。晶体管32的源极被电耦合到接地。

50.开关网络16是半桥。开关网络16接收输入电压v

in

,使用输入电压v

in

生成方波,并且将方波提供给谐振回路18。在一个实施例中,由开关网络16生成的方波信号具有基本上等于谐振回路18的谐振频率的频率。输出电压v

out

的调节是通过改变方波的开关频率来实现的。

51.为了生成方波信号,半桥驱动器28使晶体管30、32在第一状态与第二状态之间交替。

52.在第一状态中,半桥驱动器28通过将高电压(即,比晶体管30的电压阈值(有时被称为栅极电压)更大的电压)从第一输出11输出到晶体管30的栅极来接通晶体管30(即,导通状态),并且通过将低电压(即,比晶体管32的电压阈值更小的电压)从第二输出13输出到晶体管32的栅极来关断晶体管32(即,非导通状态)。因此,在第一状态中,输入电压v

in

穿过晶体管30到达节点34,并且被供应给谐振回路18。

53.在第二状态中,半桥驱动器28通过将低电压(即,比晶体管30的电压阈值更小的电压)从第一输出11输出到晶体管30的栅极来关断晶体管30,并且通过将高电压(即,比晶体管32的电压阈值更大的电压)从第二输出13输出到晶体管32的栅极来接通晶体管32。因此,

在第二状态中,输入电压v

in

没有穿过晶体管30,并且节点34被接地。

54.因此,通过使晶体管30、32在第一状态与第二状态之间交替,开关网络16能够生成方波信号,方波信号具有基本上等于输入电压v

in

的高值和基本上等于零伏的低值。

55.谐振回路18被耦合到开关网络16和变压器20。谐振回路18包括第一电感器lr、第二电感器lm、以及电容器cr。

56.第一电感器lr、第二电感器lm、以及电容器cr被彼此串联地电耦合。即,第一电感器lr被电耦合在节点34与节点35之间,第二电感器lm被电耦合在节点35与节点37之间,并且电容器cr被电耦合在节点37与接地之间。

57.谐振回路18接收由开关网络16生成的方波信号,并且基于该方波信号生成电流信号。如先前所讨论的,在一个实施例中,由开关网络16生成的方波信号具有基本上等于谐振回路18的谐振频率的频率。在该实施例中,谐振回路18起调谐滤波器作用,并且由谐振回路18生成的电流信号是由傅里叶级数展开的单个基本谐波形成的正弦交流(ac)信号。

58.变压器20被耦合到谐振回路18、整流器22、以及输出电容器24。变压器20包括:在变压器20的初级侧上的第一绕组36;以及在变压器20的次级侧上的第一半绕组38和第二半绕组40。第一绕组36被并联地电耦合到第二电感器lm。即,第一绕组36被电耦合到节点35和节点37。第一半绕组38和第二半绕组40被彼此串联地电耦合。特别地,第一半绕组38被电耦合在节点39与节点41之间,而第二半绕组40被电耦合在节点41与节点43之间。

59.变压器20在变压器20的初级侧(即,如图1所示的变压器20的左侧)上接收来自谐振回路18的ac信号,并且将ac信号传递到变压器20的次级侧(即,如图1所示的变压器20的右侧)。响应于ac信号而在变压器20的次级侧处所生成的电压取决于变压器20的绕组比。在第一半绕组38和第二半绕组40中的每个半绕组处的次级电压(vs)可以是使用方程(1)来计算:

[0060][0061]

其中,第一绕组36具有n

p

数目的匝数,第一半绕组38和第二半绕组40各自具有ns数目的匝数,并且在第一绕组36处的初级电压等于v

p

。在一个实施例中,匝数ns与n

p

的绕组比被选择成使得在稳定状态条件下,次级电压vs允许交流电在第一半绕组38和第二半绕组40中的每个半绕组中循环。

[0062]

整流器22被耦合到变压器22和输出电容器24。整流器22包括同步整流驱动器42和晶体管44、46。在一个实施例中,如图1所示,晶体管44、46是mosfet。同步整流驱动器42包括第一输入48、第二输入50、第一输出52和第二输出54。第一输入48被电耦合到节点43,第二输入50被电耦合到节点39,第一输出52被电耦合到晶体管46的栅极,而第二输出54被电耦合到晶体管44的栅极。晶体管44的漏极被电耦合到节点43,而晶体管44的源极被电耦合到接地。晶体管46的漏极被电耦合到节点39,而晶体管46的源极被电耦合到接地。

[0063]

整流器22从变压器20的次级侧接收ac信号,将ac信号转换成直流(dc)信号,并且将dc信号通过节点41提供到输出电容器24。整流器22通过将电流的方向固定在单一方向上来将ac信号转换成dc信号。特别地,整流器22将电流的方向固定在如图1中的电流i

s1

、i

s2

和i

out

所指示的方向上。为了固定电流的方向并且将ac信号转换成dc信号,同步整流驱动器42基于第一半绕组38和第二半绕组40是否导通,通过接通晶体管44、46(即,导通状态)或关断

晶体管44、46(即,非导通状态)来控制晶体管44、46以仿真理想二极管。

[0064]

如先前所讨论的,变压器20在变压器20的初级侧上接收来自谐振回路18的ac信号,并且将ac信号传递到变压器20的次级侧。结果,在第一半绕组38和第二半绕组40上的ac信号将彼此相位相差180度,并且在第一周期与第二周期之间交替。在第一周期中,在第一半绕组38上的ac信号将为高,而在第二半绕组40上的ac信号将为低。相反地,在第二周期中,在第一半绕组38上的ac信号将为低,而在第二半绕组40上的ac信号将为高。

[0065]

在第一周期中(即,当在第一半绕组38上的ac信号为低时),同步整流驱动器42通过将高电压(即,比晶体管46的电压阈值(有时被称为栅极电压)更大的电压)从第一输出52输出到晶体管46的栅极来接通晶体管46,并且通过将低电压(即,比晶体管44的电压阈值更小的电压)从第二输出54输出到晶体管44的栅极来关断晶体管44。结果,当第一半绕组38导通时,电流i

s2

能够流过晶体管46、第一半绕组38、以及节点41,并且流出到输出电容器24。

[0066]

同样地,在第二周期中(即,在第二半绕组40上的ac信号将为低),同步整流驱动器42通过将高电压(即,比晶体管44的电压阈值更大的电压)从第二输出54输出到晶体管44的栅极来接通晶体管44,并且通过将低电压(即,比晶体管46的电压阈值更小的电压)从第一输出54输出到晶体管46的栅极来关断晶体管46。结果,当第二半绕组40开始导通时,电流i

s1

能够流过晶体管44、第二半绕组40、以及节点41,并且流出到输出电容器24。

[0067]

在一个实施例中,同步整流驱动器42基于晶体管44、46的体二极管是否导通来确定半绕组38、40何时开始导通。同步整流驱动器42确定当电流在第一输入48处被感测到时第二半绕组40开始导通。同样地,同步整流驱动器42确定当电流在第二输入50处被感测到时第一半绕组38开始导通。

[0068]

通过使用晶体管44、46来取代二极管,由于同步整流驱动器42能够控制晶体管44、46以最小化晶体管44、46的沟道导通时间,因此整流器22的效率得到改善。

[0069]

输出电容器24被耦合到变压器20和整流器22。特别地,输出电容器24被电耦合到节点48。

[0070]

输出电容器24从整流器22接收和存储电流i

out

,并且在输出节点14处提供输出电压v

out

。输出电容器24确保输出电压v

out

保持稳定,并且针对负载26进行适当调节。

[0071]

如先前所讨论的,同步整流驱动器42基于第一半绕组38和第二半绕组40是否导通来接通或关断晶体管44、46。结果,当谐振转换器10处于稳定状态条件时(即,当输出电容器24被充分地充电时),在晶体管44、46的漏极处的电压将在高状态与低状态之间交替。在第一周期中(即,当晶体管44关断并且晶体管46接通时),在晶体管44(v

dvs44

)和晶体管46(v

dvs46

)的漏极处的电压可以使用方程(2)和(3)进行计算:

[0072]vdvs44

=2

·vout

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(2)

[0073]vdvs46

=0

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(3)

[0074]

同样地,在第二周期中(即,当晶体管44接通并且晶体管46关断时),在晶体管44(v

dvs44

)和晶体管46(v

dvs46

)的漏极处的电压可以使用方程(4)和(5)进行计算:

[0075]vdvs44

=0

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(4)

[0076]vdvs46

=2

·vout

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(5)

[0077]

使用晶体管44、46以及同步整流驱动器42的潜在问题在于当晶体管44、46被关断时在晶体管44、46的漏极处可能会生成电压尖峰。当电压尖峰v

spike

存在时,在晶体管44、46

的漏极处的电压可以使用方程(6)进行计算:

[0078]vdvs44

=v

dvs46

=2

·vout

+v

spike

ꢀꢀꢀꢀꢀꢀꢀ

(6)

[0079]

电压尖峰有时由电流反转引起。例如,当晶体管44、46中的一个晶体管具有延迟的关断时,在变压器20的次级侧中循环的电流可能被反转。归因于变压器20耦合以及归因于变压器20的次级侧中的寄生设备,因此可以生成电压尖峰。电压尖峰还可能归因于谐振转换器10在谐振之上工作而生成。当谐振转换器10在谐振之上工作时,可能归因于例如在晶体管44、46的体二极管中循环的电流、归因于寄生设备、以及归因于变压器20耦合而生成电压尖峰。在晶体管44、46的漏极上所生成的电压尖峰是危险的,并且有时可能会损坏谐振转换器10。

[0080]

为了减少在晶体管44、46的漏极上的电压尖峰,图1的同步整流驱动器42利用具有有源钳位器的同步整流驱动器来代替。图2示出了包括整流器22的谐振转换器55的示图,其中整流器22包括具有有源钳位器74的同步整流驱动器56。

[0081]

类似于谐振转换器10,谐振转换器55包括输入端子12、输出端子14、开关网络16、谐振回路18、变压器20、整流器22、以及输出电容器24。然而,与谐振转换器10的差别在于,整流器22包括具有有源钳位器74的同步整流驱动器56。同步整流驱动器56包括第一输入58、第二输入60、第一输出62、第二输出64、第三输出66、第一栅极驱动器70、第二栅极驱动器72和有源钳位器74。

[0082]

第一输入58被电耦合到节点43,而第二输入60被电耦合到节点39。第一输出62被电耦合到晶体管44的栅极,第二输出64被电耦合到晶体管46的栅极,而第三输出66被电耦合到节点68。

[0083]

第一栅极驱动器70和第二栅极驱动器72如关于图1的同步整流驱动器42所讨论的来控制晶体管44、46。特别地,第一栅极驱动器70和第二栅极驱动器72基于第一半绕组38和第二半绕组40是否导通,通过接通或关断晶体管44、46来控制晶体管44、46,以仿真理想二极管。当第二半绕组40开始导通时,第一栅极驱动器70通过将高电压从第一输出62输出到晶体管44的栅极来接通晶体管44,而第二栅极驱动器72通过将低电压从第二输出64输出到晶体管46的栅极来关断晶体管46。结果,当第二半绕组40开始导通时,电流i

s1

能够流过晶体管44、第二半绕组40、以及节点41,并且流出到输出电容器24。同样地,当第一半绕组38开始导通时,第二栅极驱动器72通过将高电压从第二输出64输出到晶体管46的栅极来接通晶体管46,而第一栅极驱动器70通过将低电压从第一输出62输出到晶体管44的栅极来关断晶体管44。结果,当第一半绕组38导通时,电流i

s2

能够流过晶体管46、第一半绕组38、以及节点41,并且流出到输出电容器24。

[0084]

有源钳位器74通过钳位在晶体管44、46的漏极处所吸收的电流来将在晶体管44、46的漏极上的电压限制到期望的值。有源钳位器74通过吸收在节点43、39处的电流来在晶体管44、46的漏极处钳位电流。当电流i

s1

流过晶体管44时,有源钳位器74吸收从节点43进入第一输入58中的钳位电流i

clamp

。同样地,当电流i

s2

流过晶体管46时,有源钳位器74吸收从节点39进入第二输入60中的电流i

clamp

。通过在晶体管44、46的漏极处吸收钳位电流,有源钳位器74能够减少在晶体管44、46的漏极处的电压尖峰。

[0085]

有源钳位器74还恢复并使用钳位电流i

clamp

来对输出电容器24充电。有源钳位器74通过将在晶体管44、46的漏极处的电流吸收到第三输出66来恢复钳位电流i

clamp

。当晶体管

44被关断并且紧接在电流i

s1

的过零点之后,有源钳位器74恢复在节点43处的钳位电流i

clamp

,并且将钳位电流i

clamp

输出到第三输出66。同样地,当晶体管46被关断并且紧接在电流i

s2

的过零点之后,有源钳位器74恢复在节点39处的电流i

clamp

,并且将钳位电流i

clamp

输出到第三输出66。通过将钳位电流i

clamp

吸收到第三输出66,除了电流i

out

之外,通过限制在晶体管44、46的漏极处的电压所引起的任何功率损耗被恢复,并且被用于对输出电容器24充电。结果,谐振转换器55的效率得到改善。

[0086]

图3示出了根据在本文中所公开的第一实施例的有源钳位器74的详细示图。在图3所示的实施例中,有源钳位器74包括电路系统76。电路系统76包括第一二极管78、第二二极管80、第三二极管82、第四二极管84、晶体管86、第一电阻器88、第二电阻器90、以及电容器92。同步整流驱动器56的第一输入58被电耦合到电路系统76的节点96,同步整流驱动器56的第二输入60被电耦合到电路系统76的节点94,而同步整流驱动器56的第三输出66被电耦合到晶体管86的源极。

[0087]

第一二极管78被电耦合在节点94与节点98之间,第二二极管80被电耦合在节点96与节点98之间,第三二极管82被电耦合在节点96与节点100之间,而第四二极管84被电耦合在节点94与节点100之间。晶体管86的漏极被电耦合到节点100,晶体管86的源极被电耦合到同步整流驱动器56的第三输出66,而晶体管86的栅极被电耦合到节点102。在一个实施例中,如图3所示,晶体管86是n沟道mosfet。第一电阻器88被电耦合在节点98与节点102之间,而第二电阻器90被电耦合在节点102与接地之间。电容器92被电耦合在节点98与接地之间。

[0088]

电路系统76钳位在晶体管44、46的漏极处的电压,并且使用钳位电流i

clamp

来对输出电容器24充电。结果,在节点43、39处的电压尖峰减少,并且谐振转换器55的效率得到改善。当时间常数r

88

*c

gs86

小于钳位在晶体管44、46的漏极上的电压尖峰所需的时间时,电路系统76是有效的,其中r

88

是第一电阻器88的电阻,而c

gs86

是晶体管86的栅极与源极之间的电容。

[0089]

电路系统76包括钳位模块104和阈值设定模块106。钳位模块104包括第三二极管82、第四二极管84、以及晶体管86。阈值设定模块106包括第一二极管78、第二二极管80、第一电阻器88、第二电阻器90、以及电容器92。

[0090]

钳位模块104实施了有源钳位器电路,以用于在节点39、43处吸收钳位电流i

clamp

。晶体管86是有源元件、并且被设计为设定用于最大化钳位电流i

clamp

的所期望的电流电平。由于钳位电流i

clamp

等于当晶体管86在其饱和区域(i

dsat

)中工作时的漏极电流,因此可以通过选择用于晶体管86的沟道宽度和长度来固定用于钳位电流i

clamp

的所期望的电流电平。在一个实施例中,钳位电流i

clamp

使用方程(7)和(8)进行计算:

[0091][0092]

k'=μ

·cox

ꢀꢀꢀꢀꢀꢀꢀꢀ

(8)

[0093]

其中,w是晶体管86的沟道宽度,l是晶体管86的沟道长度,μ(晶体管86的电子迁移率)是恒定的,c

ox

(晶体管86的氧化物电容)是恒定的,v

gs

是晶体管86的栅极与源极之间的电压,v

th86

是晶体管86的电压阈值(即,栅极电压),λ是谐振转换器55的谐振频率,而v

ds86

是晶体管86的漏极源极电压。因此,通过选择晶体管86的沟道宽度和长度,可以针对钳位电流i

clamp

来选择所期望的电流电平。

[0094]

第三二极管82和第四二极管84被包括在钳位模块104中,使得单个有源组件(即,晶体管86)可以被用于在节点43处所恢复的钳位电流i

clamp

和在节点39处所恢复的钳位电流i

clamp

两者。当晶体管46被关断并且电压尖峰紧接在电流i

s2

的过零点之后在节点39处形成时,有源钳位器74恢复在节点39处的钳位电流i

clamp

,钳位电流i

clamp

流过第三二极管82、晶体管86,并且流出第三输出66。同样地,当晶体管44被关断并且电压尖峰紧接在电流i

s1

的过零点之后在节点43处形成时,有源钳位器74恢复在节点43处的钳位电流i

clamp

,钳位电流i

clamp

流过第四二极管84、晶体管86,并且流出第三输出66。通过使用单个晶体管86,电路系统76的整体面积最小化。

[0095]

在通过钳位模块104的钳位期间,钳位电流i

clamp

在第三二极管82或第四二极管84上产生电压降。电压降依赖于第三二极管82和第四二极管84的内部串联电阻。当与v

out

相比较的电压降不限制漏极电流时,获得针对电路系统76的正确设计。这表明,对于最大钳位电流,当晶体管86在其饱和区域中工作时,晶体管86的漏极源极电压(v

ds86

)大于在晶体管86的漏极处的电压。

[0096]

阈值设定模块106通过控制晶体管86来限制或设定晶体管44、46的漏极处的最大电压。节点98处的电压是基于晶体管44、46的漏极处的经整流的峰值电压、以及第一二极管78和第二二极管80上的电压降。在第一周期中(即,当晶体管44被关断并且晶体管46被接通时),在节点98处的电压可以使用方程(9)进行计算:

[0097]vnode98

=v

ds44-v

d80

ꢀꢀꢀꢀꢀꢀꢀ

(9)

[0098]

其中,v

node98

是在节点98处的电压,v

dvs44

是在晶体管44的漏极处的电压,而v

d80

是第二晶体管80的电压降。在第二周期中(即,当晶体管44被接通并且晶体管46被关断时),在节点98处的电压可以使用方程(10)进行计算:

[0099]vnode98

=v

ds46-v

d78

ꢀꢀꢀꢀꢀꢀ

(10)

[0100]

其中,v

node98

是在节点98处的电压,v

dvs46

是在晶体管46的漏极处的电压,而v

d78

是第一晶体管78的电压降。第一电阻器88和第二电阻器90的电阻被选择成使得通过第一电阻器88和第二电阻器90的电流ir被限制到几毫安(例如,1毫安至3毫安)。结果,可以忽略第一二极管78和第二二极管80上的二极管电阻电压降。在该条件下,在节点102处的电压可以使用方程(11)和(12)进行计算:

[0101]vnode102

=α

·vnode98

ꢀꢀꢀꢀꢀꢀ

(11)

[0102][0103]

其中,v

node102

是在节点102处的电压,r

88

是第一电阻器88的电阻,而r

90

是第二电阻器90的电阻。然后,电阻器86的栅极源极电压可以使用方程(13)进行计算:

[0104]vgs86

=v

node102-v

out

=v

out

·

(2α-1)+α

·

(v

max-v

d78,80

)

ꢀꢀ

(13)

[0105]

其中,v

gs86

是晶体管86的栅极源极电压,而v

max

是在晶体管44、46的漏极处的最大电压电平。由于当晶体管86的栅极与源极之间的电压(v

gs86

)等于晶体管86的电压阈值(即,栅极电压)时晶体管86开始导通,因此在晶体管44的漏极处的最大电压可以使用方程(14)进行计算:

[0106]

[0107]

同样地,在晶体管46的漏极处的最大电压可以使用方程(15)进行计算:

[0108][0109]

如先前所讨论的,当时间常数r

88

*c

gs86

小于钳位在晶体管44、46的漏极上的电压尖峰所需的时间时,电路系统76是有效的,其中r

88

是第一电阻器88的电阻,而c

gs86

是晶体管86的栅极与源极之间的电容。在其中时间常数r

88

*c

gs86

高于钳位在晶体管44、46的漏极上的电压尖峰所需的时间的情况下,可以使用允许快速干预时间的有源钳位器。图4示出了根据在本文中所公开的第二实施例的有源钳位器74的详细示图。在第二实施例中,有源钳位器74包括电路系统108。类似于在图3中所示的电路系统76,电路系统108包括第一二极管78、第二二极管80、第三二极管82、第四二极管84、晶体管86、第一电阻器88、第二电阻器90、以及电容器92。然而,与电路系统76的差别在于,电路系统108利用达林顿mosfet(darlington mosfet)配置以便减小时间常数r

88

*c

gs86

。电路系统108(具体地,钳位模块104)包括晶体管110、齐纳二极管(zener diode)112、以及第三电阻器114。

[0110]

晶体管110的漏极被电耦合到节点100,晶体管110的栅极被电耦合到节点102,而晶体管110的源极被电耦合到晶体管86的栅极。齐纳二极管112被电耦合在晶体管86的栅极与同步整流驱动器56的第三输出66之间。第三电阻器114被电耦合在晶体管86的栅极与同步整流驱动器56的第三输出66之间。

[0111]

为了减小时间常数r

88

*c

gs86

,具有小的沟道宽度的晶体管被用于晶体管110。即,晶体管110的沟道宽度被选择为小于晶体管86的沟道宽度。通过针对晶体管110使用较小的沟道宽度,可以减小晶体管86的栅极与源极之间的电容(即,c

gs86

)。结果,与电路系统76相比,电路系统108具有较快的钳位干预时间。此外,在晶体管86、110的栅极与漏极之间的电容有助于增加钳位干预的速度。

[0112]

对于其中在晶体管44、46的漏极处的电压(v

dvs44

、v

dvs46

)具有非常快的通信时间的应用,可以使用驱动模块来动态地激活有源钳位器74的钳位模块104。图5示出了根据在本文中所公开的第三实施例的有源钳位器的详细示图。在图5所示的实施例中,有源钳位器74包括电路系统116。类似于在图3中所示的电路系统76,电路系统116(具体地,钳位模块104)包括第三二极管82、第四二极管84、以及晶体管86。然而,与电路系统76的差别在于,阈值设定模块106由驱动模块118代替。

[0113]

驱动模块118包括二极管120、电容器124、以及驱动器126。晶体管86的栅极被电耦合到节点128。二极管120被电耦合在节点128与同步整流驱动器56的第三输出66之间。电容器124被电耦合在节点128与驱动器126之间。驱动器126被电耦合在电容器124与接地之间。驱动器126接收电源v

cc

和钳位接通(clamp on)信号。

[0114]

驱动模块118基于钳位接通信号来动态地激活钳位模块104。特别地,当钳位接通信号为低时驱动模块118去激活钳位模块104,并且当钳位接通信号为高时驱动模块118激活钳位模块104。在钳位模块104被激活时钳位模块104吸收钳位电流i

clamp

,而在钳位模块104被去激活时钳位模块104不吸收钳位电流i

clamp

。

[0115]

当钳位接通信号为低时,驱动器126将低驱动信号(即,小于晶体管86的电压阈值的电压)输出到电容器124。结果,晶体管86将被关断(即,非导通),而晶体管86将不吸收钳位电流i

clamp

。当驱动信号为低时,电容器124的电压(v

c124

)可以使用方程(16)进行计算:

[0116]vc124

=v

out-v

d120

ꢀꢀꢀꢀꢀꢀ

(16)

[0117]

其中,v

d120

是在二极管120上的电压降。

[0118]

当钳位接通信号为高时,驱动器126将等于电源v

cc

的高驱动信号输出到电容器124。在一个实施例中,电源v

cc

大于晶体管86的电压阈值。结果,晶体管86将被接通(即,导通),并且晶体管86将吸收钳位电流i

clamp

、并且限制在晶体管44、46的漏极处的电压。当驱动信号为高时,电容器124的电压(v

c124

)可以使用方程(17)进行计算:

[0119]vc124

=v

out-v

d120

+v

cc

ꢀꢀꢀꢀꢀꢀ

(17)

[0120]

在一个实施例中,在晶体管44、46的漏极处的电压信号(v

dvs44

、v

dvs46

)的上升沿处激活钳位模块104。图6示出了根据在本文中所公开的一个实施例的、图5的有源钳位器74的波形的示图。

[0121]

如图6所示,当在晶体管44的漏极处的电压信号(v

dvs44

)为低时,钳位接通信号为低。同样地,当在晶体管46的漏极处的电压信号(v

dvs46

)为低时,钳位接通信号为低。如先前所讨论的,当钳位接通信号为低时,电容器124的电压(v

c124

)等于方程(16)所计算的电压。结果,晶体管86为断开(即,非导通),并且钳位电流i

clamp

等于零。

[0122]

当在晶体管44/46的漏极处的电压信号(v

dvs44

/v

dvs46

)从低转变到高时,钳位接通信号在上升沿期间从低转变到高。如先前所讨论的,当钳位接通信号为高时,电容器124的电压(v

c124

)等于方程(15)所计算的电压。结果,晶体管86为闭合(即,导通)、并且开始吸收钳位电流i

clamp

。在一个实施例中,为了避免功率的损失,钳位接通信号在预定的时间量内保持为高。

[0123]

图7示出了根据在本文中所公开的第四实施例的有源钳位器的详细示图。在第四实施例中,有源钳位器74包括电路系统130。类似于在图3中所示的电路系统76,电路系统130(具体地,钳位模块104)包括第三二极管82和第四二极管84。然而,与电路系统76的差别在于,晶体管86由晶体管132代替。在一个实施例中,如图7所示,晶体管132是p沟道mosfet。附加地,阈值设定模块106被去除,而同步整流驱动器56包括第三输入134,该第三输入134被电耦合到晶体管132的栅极。

[0124]

第三二极管82被电耦合在同步整流驱动器56的第一输出58与节点100之间,而第四二极管84被电耦合在同步整流驱动器56的第二输出60与节点100之间。晶体管132的源极被电耦合到节点100,晶体管132的漏极被电耦合到同步整流驱动器56的第三输出66,而晶体管132的栅极被电耦合到同步整流驱动器56的第三输入134。

[0125]

电路系统130允许通过外部电压v

ext

来动态地激活钳位模块104。钳位模块104通过将外部电压v

ext

经由第三输入134施加到晶体管132的栅极来激活。钳位模块104的激活和去激活是基于晶体管132的电压阈值(即,栅极电压)。当在节点100处的电压与外部电压v

ext

之间的差大于晶体管132的电压阈值时,晶体管132将导通,并且将钳位电流i

clamp

吸收到第三输出66。相反地,当在节点100处的电压与外部电压v

ext

之间的差小于晶体管132的电压阈值时,晶体管132将不导通,并且因此钳位电流i

clamp

将不吸收到第三输出66。

[0126]

在第四实施例中,在晶体管44的漏极处的最大电压可以使用方程(18)进行计算:

[0127]vdvs44

=v

ext

+v

th132

+v

d82

ꢀꢀꢀꢀꢀꢀ

(18)

[0128]

其中,v

dvs44

是在晶体管44的漏极处的电压,v

ext

是在第三输入134处所施加的外部电压,v

th132

是晶体管132的电压阈值,而v

d82

是在第三二极管82上的电压降。同样地,在晶体

管46的漏极处的最大电压可以使用方程(19)进行计算:

[0129]vdvs46

=v

ext

+v

th132

+v

d84

ꢀꢀꢀꢀꢀꢀ

(19)

[0130]

其中,v

dvs46

是在晶体管46的漏极处的电压,v

ext

是在第三输入134处所施加的外部电压,v

th132

是晶体管132的电压阈值,而v

d84

是在第四二极管84上的电压降。

[0131]

在一个实施例中,外部电压v

ext

被设定成输出电压v

out

的两倍。外部电压v

ext

可以使用方程(20)进行计算:

[0132]vext

=2

·vout

ꢀꢀꢀꢀꢀꢀꢀ

(20)

[0133]

在该实施例中,在晶体管44的漏极处的最大电压可以使用方程(21)进行计算:

[0134]vdvs44

=2

·vout

+v

th132

+v

d82

ꢀꢀꢀꢀꢀ

(21)

[0135]

其中,v

th132

是晶体管132的电压阈值,而v

d82

是在第三二极管82上的电压降。同样地,在晶体管46的漏极处的最大电压可以使用方程(22)进行计算:

[0136]vdvs46

=2

·vout

+v

th132

+v

d84

ꢀꢀꢀꢀꢀ

(22)

[0137]

其中,v

th132

是晶体管132的电压阈值,并且v

d84

是在第四二极管84上的电压降,而v

out

是输出电压。

[0138]

在一个实施例中,第三输入134被电耦合到外部电压参考136。外部电压参考136确保了外部电压v

ext

保持稳定并且进行适当调节以驱动晶体管132的栅极。

[0139]

应当注意,尽管本技术结合谐振转换器55讨论了同步整流驱动器56,但是同步整流驱动器56可以被用于在特定节点或引脚处经受电压尖峰的其他设备。

[0140]

根据一个或多个实施例,同步整流驱动器56提供了低成本解决方案,以减少在谐振转换器55的晶体管44、46的漏极处的电压尖峰。同步整流驱动器56还通过恢复钳位电流i

clamp

以对输出电容器24充电来增加谐振转换器55的效率。

[0141]

可以结合上文所描述的各种实施例,以提供另外的实施例。鉴于以上详细的描述,可以对实施例进行这些或者其他改变。一般地,在所附的权利要求中,所使用的术语不应当被解释为限制在本说明书和权利要求中所公开的具体实施例的权利要求,而应当被解释为包括所有可能的实施例以及这种权利要求被赋予的等同方案的全范围。因此,权利要求不受本公开的限制。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1