电压倍增器电路的制作方法

mobile phones,”in proc.2

nd ieee-cas r8 workshop,1997,pp.97-100;

15.[gerber]b.gerber,j.c.martin以及j.fellrath,“a 1.5v single-supply one-transistor cmos eeprom,”ieee j.solid-state circuits,vol.sc-16,no.3,pp.195-200,6月1981;

[0016]

[witters]j.s.witters,g.groeseneken以及h.e.maes,“analysis and modeling of on-chip high voltage generator circuits for use in eeprom circuits,”ieee j.solid-state circuits,vol.24,no.5,pp.1342-1380,十月1989;

[0017]

[umezawa]a.umezawa等人“a 5-v-only operation 0.6-um flash eeprom with row decoder scheme in triple-well structure,”ieee j.solid-state circuits,vol.27,no.11,pp.1540-1546,11月1992;

[0018]

[jinbo]t.jinbo等人“a 5-v-only 16-mb flash memory with sector erase mode,”ieee j.solid-state circuits,vol.27,no.11,pp.1547-1554,11月1992;

[0019]

[atsumi]s.atsumi等人“a 16-mb flash eeprom with new self-data-refresh scheme for a sector erase operation,”ieee j.solid-state circuits,vol.29,no.4,pp.461-469,4月1994;

[0020]

[calligaro 1]c.calligaro,p.malcovati以及g.torrelli,“voltage multiplier with output stabilization,”in proc.2

nd ieee-cas r8 workshop,1997,pp.97-100;

[0021]

[calligaro 2]c.calligaro等人“positive and negative cmos voltage multiplier for 5-v-only flash memories,”in proc.2

nd ieee-cas r8 workshop,1997,pp.97-100;

[0022]

[monna]g.l.e.monna et al,“charge pump for optimal dynamic range filters,”in proc.iscas’94,1994,pp.747-750;

[0023]

[berkhout]m.berkhout,g.van steenwijk and a.j.m.van tuijl,“a low-ripple chargepump circuit for high voltage applications,”in proc.esscirc’93,1993,pp.290-293;

[0024]

[wang]c.c.wang以及j.c.wu,“efficiency improvement in charge pump circuits,”ieee j.solid-state circuits,vol.32,no.6,pp.852-860,6月1997;

[0025]

[steenwijk]g.van steenwijk,k.hoen以及hans wallinga,“analysis and design of a charge pump circuit for high output current applications,”in proc.esscirc’93,1993,pp.118-121;

[0026]

[gasparini]f.gasparini以及g.zingales,“sul funzionamento dei moltiplicatori di tensione a raddrizzatori e condensatori,”l’elettrotecnica,vol.46,no.11,pp.742-753,11月1959;

[0027]

[weiner]m.m.weiner,“analysis of cockcroft-walton voltage multipliers with an arbitrary number of stages,”the review of scientific instruments,vol.40,no.2,pp.330-333,2月1969;

[0028]

[brugler]j.s.brugler,“theoretical performance of voltage multiplier circuits,”ieee j.solid-state circuits,pp.132-135,6月1971;

[0029]

[lin]p.m.lin以及l.o.chua,“topological generation and analysis of voltage multipliers circuits,”ieee trans.circuits syst.,vol.cas-24,no.10,pp.517-530,10月1977;以及

[0030]

[pulvirenti]f.pulvirenti以及r.gariboldi,“voltage elevator on the charge pump type,”european patent 0 696 839.

[0031]

具体地,文献[schenkel]公开了具有分立电容器和阀二极管的电压倍增器。

[0032]

文献[cockcroft]公开了用于使用具有较低操作范围的电容器生成比文献[schenkel]所公开的电路所能获得的电压更高的高达几百万伏电压的电压倍增器。然而,在文献[cockcroft]公开的应用中,耦合电容器可以制造得足够大来实现有效的倍增和足够的电流容量,而片上电容器具有几百pf的值和相对较高的杂散电容值。因此,文献[cockcroft]所公开的电压倍增器,通常被称为cockcroft-walton电压倍增器,因为它对杂散电容敏感,在集成电路中没有大量使用。

[0033]

文献[luscher]公开了基于schenkel拓扑的电压倍增器,它对寄生电容非常不敏感,通过使用mos二极管替换阀以单片形式实现。在文献[dickson]中也公开了这样的电压倍增器电路并且它通常被称为dickson倍增器。

[0034]

基于dickson架构的片上电压倍增器被用于智能功率集成电路中,用于驱动例如文献[storti]、[hobrecht]、[wong]、[gariboldi 94]和[baveno]所公开的输出功率晶体管;例如文献[gerber]、[witters]、[umezawa]、[jinbo]、[atsumi]、[calligaro 1]和[calligaro 2]所公开的,它们在非易失性存储器电路中用于对存储单元进行编程和擦除;并且例如文献[monna]所公开的,它们用于低压应用中来优化动态电压范围。

[0035]

例如文献[storti]、[hobrecht]、[gerber]、[monna]和[berkhout]所公开的,基于dickson架构的片上电压倍增器利用由二极管互连并与两个反相时钟信号并联耦合的电容器。这些具有实现二极管功能的mos晶体管的电路的实现方式例如在文献[witters]、[wong]、[calligaro 1]和[calligaro 2]中公开。

[0036]

例如由文献[umezawa]、[jinbo]、[atsumi]、[gariboldi 94]、[gariboldi 96]和[wang]所公开的,具有类似开关一样使用的mos晶体管的电压倍增器在本领域中也是已知的,其特别是用于如文献[baveno]和[steenwijk]所公开的低电压应用。

[0037]

cockcroft-walton电压倍增器中使用的电荷泵电路的示例由文献[gasparini]、[weiner]、[brugler]和[lin]公开。

技术实现要素:

[0038]

尽管该领域有广泛的活动,但已知的片上全集成电压倍增器可能仍然具有占用大硅面积的缺点。

[0039]

因此,本领域需要提供针对具有集成电容器的高倍增因子和低硅面积占用而构思的改进的电压倍增器电路。

[0040]

一些实施例有助于提供这样的改进的电压倍增器电路。

[0041]

根据一个或多个实施例,这样的改进的电压倍增器电路可以通过具有所附权利要求中阐述的特征的电路来实现。

[0042]

权利要求是本文提供的关于实施例的技术教导的组成部分。

[0043]

一些实施例涉及包括电荷泵架构的电压倍增器电路。

[0044]

一个或多个实施例可以被应用于智能功率集成电路、存储器集成电路、低压应用、用于微机电系统(mems)的控制器和驱动器等。

[0045]

在一个实施例中,电压倍增器包括输入节点、输出节点以及用于接收限定两个换向状态的第一和第二时钟信号的第一和第二控制节点。中间节点的有序序列被耦合在输入和输出节点之间并且包括两个有序子序列。电容器被耦合在:第一子序列中的每个奇数中间节点与第一控制节点之间;第一子序列中的每个偶数中间节点与第二控制节点之间;第二子序列中的每个奇数中间节点与第一子序列中对应的奇数中间节点之间;以及第二子序列中的每个偶数中间节点与第一子序列中对应的偶数中间节点之间。电路包括与中间节点耦合的选择性导电电子组件。在第一换向状态下,电子组件在每个偶数中间节点和相应的下一奇数中间节点之间、在输入节点和第一中间节点之间、以及在最后一个中间节点和输出节点之间提供导电路径。在第二换向状态中,电子组件在每个奇数中间节点和相应的下一偶数中间节点之间提供导电路径。

[0046]

在一个或多个实施例中,电压倍增器电路可以包括第一输入节点和第二输入节点,其被配置为在它们之间接收来自电压源的输入电压。电压倍增器电路可以包括第一输出节点和第二输出节点,其被配置为耦合到输出电容器,以跨输出电容器产生输出电压。电压倍增器电路可以包括被配置为接收第一时钟信号的第一输入控制节点和被配置为接收第二时钟信号的第二输入控制节点,第二时钟信号与第一时钟信号反相。电压倍增器电路因此可以根据第一时钟信号和第二时钟信号的值,在第一换向状态和第二换向状态之间切换。电压倍增器电路可以包括在第一输入节点和第一输出节点之间布置的中间电压节点的有序序列。有序序列可以包括中间电压节点的第一有序子序列和中间电压节点的第二有序子序列(例如,至少两个有序子序列)。每个有序子序列可以包括相同数目的中间电压节点。例如,数目可以是偶数。例如,数目可以等于或大于四。电压倍增器电路可以包括在有序序列的第一有序子序列中的每个奇数中间电压节点和第一输入控制节点之间连接的相应电容器。第一有序子序列中的第一中间电压节点可以被选择性地耦合到第一输入节点。电压倍增器电路可以包括在有序序列的第一有序子序列中的每个偶数中间电压节点与第二输入控制节点之间连接的相应电容器。电压倍增器电路可以包括在有序序列的第二有序子序列中的每个奇数中间电压节点和有序序列的第一有序子序列中的对应奇数中间电压节点之间连接的相应电容器。电压倍增器电路可以包括在有序序列的第二有序子序列中的每个偶数中间电压节点和有序序列的第一有序子序列中的对应偶数中间电压节点之间连接的相应电容器。电压倍增器电路可以包括与有序序列的中间电压节点耦合的第一多个选择性导电电子组件。在电压倍增器电路的第一换向状态中,电子组件可以被配置为在有序序列的偶数中间电压节点中的每个偶数中间电压节点与有序序列的相应下一奇数中间电压节点之间提供导电路径,在第一输入节点和有序序列的第一中间电压节点之间提供导电路径,以及在有序序列的最后一个中间电压节点和第一输出节点之间提供导电路径。在电压倍增器电路的第二换向状态中,电子组件可以被配置为在有序序列的奇数中间电压节点中的每个奇数中间电压节点与有序序列的相应下一个偶数中间电压节点之间提供导电路径。

[0047]

在一个或多个实施例中,电压倍增器电路可以包括在第一输入节点和第一输出节点之间布置的中间电压节点的其他有序序列。其他有序序列可以包括中间电压节点的相应

第一有序子序列和中间电压节点的相应第二有序子序列(例如,至少两个有序子序列)。每个有序子序列可以包括相同数目的中间电压节点。例如,数目可以是偶数。例如,数目可以等于或大于四。电压倍增器电路可以包括在其他有序序列的第一有序子序列中的每个奇数中间电压节点和第二输入控制节点之间连接的相应电容器。其他有序序列的第一有序子序列中的第一中间电压节点可以被选择性地耦合到第一输入节点。电压倍增器电路可以包括在其他有序序列的第一有序子序列中的每个偶数中间电压节点与第一输入控制节点之间连接的相应电容器。电压倍增器电路可以包括在其他有序序列的第二有序子序列中的每个奇数中间电压节点和其他有序序列的第一有序子序列中的对应奇数中间电压节点之间连接的相应电容器。电压倍增器电路可以包括在其他有序序列的第二有序子序列中的每个偶数中间电压节点和其他有序序列的第一有序子序列中的对应偶数中间电压节点之间连接的相应电容器。电压倍增器电路可以包括与其他有序序列的中间电压节点耦合的其他多个选择性导电电子组件。在电压倍增器电路的第一换向状态中,其他电子组件可以被配置为在其他有序序列的奇数中间电压节点中的每个奇数中间电压节点与其他有序序列的相应下一个偶数中间电压节点之间提供导电路径。在电压倍增器电路的第二换向状态中,其他电子组件可以被配置为在其他有序序列的偶数中间电压节点中的每个偶数中间电压节点与其他有序序列的相应下一个奇数中间电压节点之间提供导电路径,在第一输入节点和其他有序序列的第一中间电压节点之间提供导电路径,以及在其他有序序列的最后一个中间电压节点和第一输出节点之间提供导电路径。

[0048]

在一个或多个实施例中,中间电压节点的有序序列和中间电压节点的其他有序序列可以包括中间电压节点的至少一个相应的第三有序子序列。每个有序子序列可以包括相同数目的中间电压节点。例如,数目可以是偶数。例如,数目可以等于或大于四。

[0049]

一个或多个实施例因此可以有助于减少电压倍增器电路的硅面积占用。

附图说明

[0050]

现在将参考附图,仅作为示例来描述一个或多个实施例,其中:

[0051]

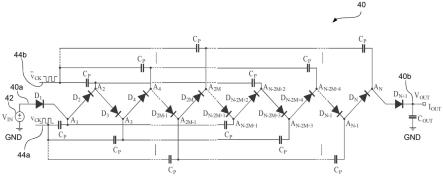

图1是根据cockcroft-walton架构的常规n级电压倍增器电路的示例电路图;

[0052]

图2是根据dickson架构的常规n级电压倍增器的示例电路图;

[0053]

图3是电压倍增器电路的等效电路的示例性电路图;

[0054]

图4是根据本说明书的一个或多个实施例的具有用于生成正电压的单分支架构的电压倍增器电路的示例性电路图;

[0055]

图5和图6是根据图4的电压倍增器电路的示例性操作的电路图;

[0056]

图7是根据本说明书的一个或多个实施例的具有用于生成正电压的双分支架构的电压倍增器电路的示例性电路图;

[0057]

图8是根据本说明书的一个或多个实施例的具有单分支架构的电压倍增器电路的示例性电路图;

[0058]

图9和图10是根据图8的电压倍增器电路的示例性操作的电路图;

[0059]

图11是根据本说明书的一个或多个实施例的具有双分支架构的电压倍增器电路的示例性电路图;

[0060]

图12是根据本说明书的一个或多个实施例的具有用于生成正电压的双分支架构

的电压倍增器电路的示例性电路图;

[0061]

图13和图14是根据图12的电压倍增器电路的实现细节的示例性电路图;

[0062]

图15是根据本说明书的一个或多个实施例的具有用于生成负电压的单分支架构的电压倍增器电路的示例性电路图;

[0063]

图16是根据本说明书的一个或多个实施例的具有用于生成负电压的双分支架构的电压倍增器电路的示例性电路图;以及

[0064]

图17是根据本说明书的一个或多个实施例的具有用于生成负电压的双分支架构的电压倍增器电路的示例性电路图。

具体实施方式

[0065]

在随后的描述中,图示了一个或多个具体细节,旨在提供对本描述的实施例的示例的深入理解。实施例可以在没有一个或多个具体细节的情况下获得,或者利用其他方法、组件、材料等来获得。在其他情况下,未详细图示或描述已知结构、材料或操作,以使得实施例的某些方面将不被遮蔽。

[0066]

在本说明书的框架中对“实施例”或“一个实施例”的引用意在指示关于该实施例所描述的特定配置、结构或特性被包括在至少一个实施例中。因此,可能出现在本说明书的一个或多个点中的诸如“在实施例中”或“在一个实施例中”的短语不一定指代同一实施例。此外,特定构造、结构或特性可以在一个或多个实施例中以任何适当的方式组合。

[0067]

本文中使用的标题/附图标记仅是为了方便而提供的,因此不限定保护范围或实施例的范围。

[0068]

贯穿本文所附附图,除非上下文另有说明,否则相同的部分或元素使用相同的附图标记/数字表示并且为了简洁将不重复对应的描述。

[0069]

通过对示例性实施例的详细描述的介绍,可以首先参考图1、图2和图3。

[0070]

图1是根据cockcroft-walton架构的常规n级电压倍增器10的示例性电路图。电压倍增器电路10包括被配置为从电压源12接收输入电压v

in

的输入节点10a、被配置为跨存储电容器c

out

产生输出电压v

out

的输出节点10b、以及在输入节点10a和输出节点10b之间耦合(例如,串联)并且从输入节点10a向输出节点10b导电的包括n+1个二极管d1,...,d

n+1

的链(或串)。例如,第一二极管d1具有与输入节点10a耦合的阳极端子以及与第二二极管d2的阳极端子耦合的阴极端子,中间二极管d2,...,dn中的每个二极管具有与前一个二极管的阴极端子耦合的相应阳极端子以及与下一个(后续)二极管的阳极端子耦合的相应阴极端子,并且最后一个二极管d

n+1

具有与倒数第二个二极管dn的阴极端子耦合的阳极端子以及与输出节点10b耦合的阴极端子。电压倍增器电路10包括被配置为接收第一驱动时钟信号v

ck

的第一驱动输入节点14a和被配置为接收与第一驱动时钟信号v

ck

反相的第二驱动时钟信号的第二驱动输入节点14b(例如,v

ck

和可以是两个方波时钟信号,具有50%的占空比并且偏移了半个时钟周期)。电压倍增器电路10包括n个泵浦(或耦合)电容器c

p

。第一泵浦电容器c

p

具有与二极管链的第一和第二二极管中间的节点耦合的第一端子(即,耦合到链的第一二极管d1的阴极端子)以及与第一驱动输入节点14a耦合的第二端子。第二泵浦电容器c

p

具有与二极管链的第二和第三二极管中间的节点耦合的第一端子(即,耦合到链的第二二极管d2的阴极端子)以及与第二驱动输入节点14b耦合的第二端子。对于其他泵浦电

容器,通用的第j泵浦电容器具有与链的第j二极管的阴极端子耦合的相应第一端子以及与链的第(j-2)二极管的阴极端子耦合的相应第二端子。

[0071]

图2是根据dickson架构的常规n级电压倍增器20的示例电路图。基本上以与图1所示相同的方式,电压倍增器电路20包括被配置为从电压源22接收输入电压v

in

的输入节点20a、被配置为跨存储电容器c

out

产生输出电压v

out

的输出节点20b、以及在输入节点20a和输出节点20b之间耦合(例如,串联)并且从输入节点20a向输出节点20b导电的包括n+1个二极管d1,...,d

n+1

的链(或串)。电压倍增器电路20包括被配置为接收第一驱动时钟信号v

ck

的第一驱动输入节点24a和被配置为接收与第一驱动时钟信号v

ck

反相的第二驱动时钟信号的第二驱动输入节点24b(例如,v

ck

和可以是两个方波时钟信号,具有50%的占空比并偏移了半个时钟周期)。电压倍增器电路20包括n个泵浦(或耦合)电容器c

p

。每个泵浦电容器c

p

具有与二极管链的两个二极管中间的节点耦合的第一端子以及与第一驱动输入节点24a或第二驱动输入节点24b耦合的第二端子。具体地,第一端子与二极管链的相同二极管耦合的两个泵浦电容器(即,一个耦合到二极管的阳极,另一个耦合到二极管的阴极)具有与两个不同的驱动输入节点耦合的第二端子,使得在电压倍增器电路20的操作期间,二极管链中的每个二极管的阳极和阴极以不同的电压电平驱动。换言之,第一端子与二极管链的奇数二极管的阴极耦合的泵浦电容器的第二端子被耦合到第一驱动输入节点24a,并且第一端子与二极管链的偶数二极管的阴极耦合的泵浦电容器的第二端子被耦合到第二驱动输入节点24b。

[0072]

在图1和图2中例示的两个电路中,存储电容器c

out

被配置为存储电荷并提供稳定的输出电压v

out

,n个泵浦电容器c

p

被配置为泵送电荷,并且二极管被配置为仅在从输入节点到输出节点的一个方向上传输电荷。如图1和图2中例示的倍增器电路的操作是本领域技术人员已知的:由与电压振幅v

ck

反相的两个时钟信号驱动的泵浦电容器c

p

在时钟信号的每个半周期交替充电和放电,使得电荷“包”沿拉高输出电压v

out

的二极管链泵送。

[0073]

图3是电压倍增器电路10和20的等效电路的示例性电路图,其中vo是在负载开路条件下由倍增器电路生成的电压,并且r

out

是等效输出电阻。根据图3中例示的等效电路,输出电压v

out

可以根据以下等式(1)来计算:

[0074]vout

=v

o-r

out

·iout

ꢀꢀꢀ

(1)

[0075]

考虑到杂散电容,在文献[dickson]中报告了电压倍增器电路10和20的开路负载电压vo和输出电阻r

out

。如果时钟周期远长于时间常数r

dcp

(其中rd是二极管电阻),则定义输出电阻r

out

的等式有效。结果总结在以下等式(2)到(4)中,其中等式(2)对两个倍增器均有效,等式(3)对dickson倍增器20有效,并且等式(4)对cockcroft-walton倍增器10有效:

[0076]vo

=v

in-(n+1)

·vd

+n

·vck

ꢀꢀꢀ

(2)

[0077][0078][0079]

其中v

in

是倍增器电路的输入电压,v

ck

是时钟信号的摆幅电压,vd是二极管的正向

压降,并且f是时钟频率。

[0080]

应注意,cockcroft-walton倍增器10具有两个主要限制:只有当泵浦电容器远大于杂散电容器时才能发生有效的电压倍增,并且输出阻抗随着倍增级的数目而迅速增加。cockcroft-walton倍增器10在单片集成电路中实现时的另一个限制是,如果两个电路均被设计为具有相同的输出阻抗,则与dickson倍增器20相比,硅尺寸随着倍增级数的增加而迅速增加。

[0081]

另一方面,由于片上电容器的电压限制,在单片集成电路中实现的dickson倍增器不能达到高输出电压。

[0082]

例如,在电压倍增器电路使用操作电压为12v的泵浦电容器,从输入电压v

in

=3.3v开始产生输出电压v

out

=70v的情况下,dickson倍增器将不会适合由于电容器的电压限制,而根据以下比较等式(3)和(4a)给出的r

out

值而获得的等式(5),具有相同输出阻抗的cockcroft-walton倍增器将具有更大的尺寸:

[0083][0084]

因此,本领域需要提供依赖于片上电容器的最大电压能力,同时减少硅面积占用的改进的电压倍增器电路。

[0085]

一个或多个实施例因此可以涉及如图4中例示的电压倍增器电路40。图4是具有用于生成正电压的单个分支架构的电压倍增器电路40的示例性电路图。

[0086]

如图4中所例示的,电压倍增器电路40包括在输入节点40a和输出节点40b之间布置的二极管d1,

…

,d

n+1

的链,基本上如参考图1和图2所讨论的,输入节点40a被配置为从电压源42接收输入电压v

in

,输出节点40b被配置为产生输出电压v

out

。二极管链在输入节点40a和输出节点40b之间提供中间电压节点a1,...,an的有序序列(例如,通用节点a

x

对应于通用二极管d

x

的阴极端子)。

[0087]

电压倍增器电路40包括被配置为接收第一驱动时钟信号v

ck

的第一驱动输入节点44a和被配置为接收与第一驱动时钟信号v

ck

反相的第二驱动时钟信号的第二驱动输入节点44b。电压倍增器电路40包括n个泵浦(或耦合)电容器c

p

。如图4所示,n个泵浦电容器c

p

被布置在数目为k=n/m的组(例如,集群)中,每个组包括m个电容器。

[0088]

第一泵浦电容器组包括m个泵浦电容器c

p

,其第一端子被耦合到从1至2m编号(即,a1,

…

,a2m)的2m个中间电压节点的第一子序列中的奇数中间电压节点a1,a3,

…

,a

2m-1

(例如,第一节点和第三节点),并且其第二端子被耦合到第一驱动输入节点44a来接收第一驱动时钟信号v

ck

。第二泵浦电容器组包括m个泵浦电容器c

p

,其第一端子被耦合到2m个中间电压节点的第一子序列中的偶数中间电压节点a2,a4,

…

,a

2m

(例如,第二节点和第四节点),并且第二端子被耦合到第二驱动输入节点44b来接收第二驱动时钟信号因此,第一组和第二组中的泵浦电容器基本上按照dickson架构来布置。

[0089]

第三泵浦电容器组包括m个泵浦电容器c

p

,其第一端子被耦合到从2m+1至4m编号(图4中不可见)的2m个中间电压节点的第二子序列中的奇数中间电压节点a

2m+1

,a

2m+3

,

…

,a

4m-1

(例如,第一节点和第三节点),并且第二端子被耦合到从1至2m编号的2m个中间电压节点的第一子序列中的对应奇数中间电压节点a1,a3,

…

,a

2m-1

(例如,第一节点和第三节点)。

换言之,第三组的泵浦电容器与第一组的泵浦电容器堆叠在一起,类似于cockcroft-walton架构。第四泵浦电容器组包括m个泵浦电容器c

p

,其第一端子被耦合到从2m+1至4m编号(图4中不可见)的2m个中间电压节点的第二子序列中的偶数中间电压节点a

2m+2

,a

2m+4

,

…

,a

4m

(例如,第二节点和第四节点),并且第二端子被耦合到从1至2m编号的2m个中间电压节点的第一子序列中的对应奇数中间电压节点a2,a4,

…

,a

2m

(例如,第二节点和第四节点)。换言之,第四组的泵浦电容器与第二组的泵浦电容器堆叠在一起,类似于cockcroft-walton架构。

[0090]

在本说明书中,当两个不同子序列的两个中间电压节点在相应有序子序列中占据相同位置(例如,第1位置、第2位置等)时,它们被称为“对应”。

[0091]

泵浦电容器组的数目与电压倍增器的级数n和每组中电容器的数目m相关。一般而言,倒数第二泵浦电容器组包括m个泵浦电容器c

p

,其第一端子被耦合至从n-2m+1至n编号的2m个中间电压节点的最后子序列中的奇数中间电压节点a

n-2m+1

,a

n-2m+3

,

…

,a

n-1

,并且第二端子被耦合到从n-4m+1至n-2m编号(图4中不可见)的中间电压节点的倒数第二子序列中的对应奇数中间电压节点a

n-4m+1

,a

n-4m+3

,

…

,a

n-2m-1

。换言之,倒数第二组的泵浦电容器与倒数第四组的泵浦电容器堆叠在一起,类似于cockcroft-walton架构。最后一个泵浦电容器组包括m个泵浦电容器c

p

,其第一端子被耦合到从n-2m+1至n编号的2m个中间电压节点的最后子序列中的偶数中间电压节点a

n-2m+2

,a

n-2m+4

,

…

,an,并且第二端子被耦合到从n-4m+1至n-2m编号(图4中不可见)的中间电压节点的倒数第二子序列中的对应偶数中间电压节点a

n-4m+2

,a

n-4m+4

,

…

,a

n-2m

。换言之,最后一组的泵浦电容器与倒数第三组的泵浦电容器堆叠在一起,类似于cockcroft-walton架构。

[0092]

因此,在如图4所例示的电压倍增器电路40中,前两组泵浦电容器c

p

基本上按照dickson架构布置,而其余(中间和最后)组泵浦电容器c

p

堆叠到先前那些泵浦电容器,类似于cockcroft-walton倍增器(例如,它们的较低端子连接到前两组电容器中电容器的较高端子,较高端子连接到二极管链,逐渐朝向输出)。简而言之,属于同一组的泵浦电容器类似于dickson电荷泵“并联”布置,而不同泵浦电容器组彼此堆叠,类似于cockcroft-walton电荷泵。

[0093]

参考图5和图6解释图4中例示的电压倍增器电路40的操作。图5是在特别是当v

ck

=0(低值)和(高值)时,在时钟信号v

ck

和的前半周期期间电路40中的电荷转移的示例。图6是特别是当v

ck

=v

ck

(高值)和(低值)时,在时钟信号v

ck

和的后半周期期间电路40中的电荷转移的示例。

[0094]

在前半个时钟周期中,当v

ck

为低且为高时,由信号v

ck

(即,耦合到奇数中间电压节点)驱动的泵浦电容器以(更多)正电压充电。它们借助奇数二极管从由信号驱动的泵浦电容器(即,耦合到偶数中间电压节点的泵浦电容器)接收电荷“包”,由信号驱动的泵浦电容器在上下文中被放电。在该阶段,第一泵浦电容器由输入电压v

in

直接充电。在后半个时钟周期,当v

ck

为高且为低时,由信号v

ck

驱动的泵浦电容器被放电。它们借助偶数二极管将电荷包提供给由信号驱动的泵浦电容器,由信号驱动的泵浦电容

器在上下文中以更正的电压充电。

[0095]

在由信号v

ck

驱动的第一组m个泵浦电容器中,第一泵浦电容器(耦合在节点44a和节点a1之间)以v

in-vd充电,第三泵浦电容器(耦合在节点44a和节点a3之间)以v

in

+2v

ck-3vd充电,第五泵浦电容器(耦合在节点44a和节点a5之间)以v

in

+4v

ck-5vd充电,依此类推,直到第(2m-1)泵浦电容器(耦合在节点44a和节点a

2m-1

之间)以v

in

+(2m-2)

·vck-(2m-1)

·vd

充电。在由驱动的第二泵浦电容器组中,第二泵浦电容器(耦合在节点44b和节点a2之间)以v

in

+v

ck-2vd充电,第四泵浦电容器(耦合在节点44b和节点a4之间)以v

in

+3v

ck-4vd充电,第六泵浦电容器(耦合在节点44b和节点a6之间)以v

in

+5v

ck-6vd下充电,依此类推,直到第2m泵浦电容器(耦合在节点44b和节点a

2m

之间)在v

in

+(2m-1)

·vck-2m

·vd

以充电。从2m+1到n的泵浦电容器(即,第3组及以后组中的那些)以2m

·

(v

ck-vd)充电;这是跨电容器的两个端子的电压。如等式(2)中已知的倍增器所报告的,输出电容以v

in

+n

·vck-(n+1)

·vd

充电。

[0096]

注意,电压倍增器电路40的等效输出电阻可以根据以下等式(6)被计算为2m级dickson倍增器和n/2m级cockcroft-walton倍增器的组合,假设时钟周期比时间常数r

dcp

长得多,其中rd是二极管电阻:

[0097][0098]

关于硅尺寸,比较用于计算r

out

的等式(3)和(6),注意,如图4中的架构(以下也称为“混合”架构)的尺寸可以被表示为:

[0099][0100]

一个或多个实施例可以涉及如图7中例示的电压倍增器电路70。图7是基于参考图4、图5和图6所讨论的相同概念,具有用于生成正电压的双分支架构的电压倍增器电路70的示例性电路图。

[0101]

如图7所示,电压倍增器电路70包括:在输入节点40a和输出节点40b之间布置的n+1个二极管的第一链,输入节点40a和输出节点40b限定基本上如参考图4所讨论的中间节点a1,

…

,an;以及在输入节点40a和输出节点40b之间布置的n+1个二极管的第二链,同样基本上如参考图4所讨论的,输入节点40a和输出节点40b限定中间电压节点b1,...,bn的另一集合。电压倍增器电路70包括2n个泵浦(或耦合)电容器c

p

/2。如图7所示,2n个泵浦电容器c

p

/2被布置在两个子集中,每个子集包括数目k=n/m的组(例如,集群),每个组包括m个电容器。第一子集包括由时钟信号v

ck

驱动(例如,耦合到节点44a)的泵浦电容器,而第二子集包括由时钟信号驱动(例如,耦合到节点44b)的泵浦电容器。

[0102]

泵浦电容器的第一子集的第一组包括泵浦电容器c

p

/2,其第一端子被耦合到第一电压节点集合a1,

…

,an中从1至m编号的m个中间电压节点的第一子序列中的奇数中间电压节点a1,a3,

…

,a

m-1

(例如,第一节点和第三节点),并且第二端子被耦合到第一驱动输入节点44a来接收第一驱动时钟信号v

ck

。泵浦电容器的第一子集的第一组还包括泵浦电容器c

p

/2,其第一端子被耦合到第二电压节点集合b1,

…

,bn中从1至m编号的m个中间电压节点的第一子序列中的偶数中间电压节点b2,b4,

…

,bm(例如,第二节点和第四节点),并且第二端子被耦合到第一驱动输入节点44a来接收第一驱动时钟信号v

ck

。

[0103]

泵浦电容器的第二子集的第一组包括泵浦电容器c

p

/2,其第一端子被耦合到第一电压节点集合a1,

…

,an中从1至m编号的m个中间电压节点的第一子序列中的偶数中间电压节点a2,a4,

…

,am(例如,第二节点和第四节点),并且第二端子被耦合到第二驱动输入节点44b来接收第二驱动时钟信号泵浦电容器的第二子集的第一组还包括泵浦电容器c

p

/2,其第一端子被耦合到第二电压节点集合b1,

…

,bn中从1至m编号的m个中间电压节点的第一子序列中的奇数中间电压节点b1,b3,

…

,b

m-1

(例如,第一节点和第三节点),并且第二端子被耦合到第二驱动输入节点44a来接收第二驱动时钟信号

[0104]

泵浦电容器的第一子集的第二组包括泵浦电容器c

p

/2,其第一端子被耦合到第一电压节点集合a1,

…

,an中从m+1至2m编号的m个中间电压节点的第二子序列中的奇数中间电压节点a

m+1

,a

m+3

,

…

,a

2m-1

(例如,第一节点和第三节点),并且第二端子被耦合到第一电压节点集合a1,

…

,an中从1至m编号的m个中间电压节点的第一子序列中的对应奇数中间电压节点a1,a3,

…

,a

m-1

(例如,第一节点和第三节点)。泵浦电容器的第二子集的第二组还包括泵浦电容器c

p

/2,其第一端子被耦合到第二电压节点集合b1,

…

,bn中从m+1至2m编号的m个中间电压节点的第二子序列中的偶数中间电压节点b

m+2

,b

m+4

,

…

,b

2m

(例如,第二节点和第四节点),并且第二端子被耦合到第二电压节点集合b1,

…

,bn中从1至m编号的m个中间电压节点的第一子序列中的对应偶数中间电压节点b2,b4,

…

,bm(例如,第二节点和第四节点)。

[0105]

泵浦电容器的第二子集的第二组包括泵浦电容器c

p

/2,其第一端子被耦合到第一电压节点集合a1,

…

,an中从m+1至2m编号的m个中间电压节点的第二子序列中的偶数中间电压节点a

m+2

,a

m+4

,

…

,a

2m

(例如,第二节点和第四节点),并且第二端子被耦合到第一电压节点集合a1,

…

,an中从1至m编号的m个中间电压节点的第一子序列中的对应偶数中间电压节点a2,a4,

…

,am(例如,第二节点和第四节点)。泵浦电容器的第二子集的第二组还包括泵浦电容器c

p

/2,其第一端子被耦合到第二电压节点集合b1,

…

,bn中从m+1至2m编号的m个中间电压节点的第二子序列中的奇数中间电压节点b

m+1

,b

m+3

,

…

,b

2m-1

(例如,第一节点和第三节点),并且第二端子被耦合到第二电压节点集合b1,

…

,bn中从1至m编号的m个中间电压节点的第一子序列中的对应奇数中间电压节点b1,b3,

…

,b

m-1

(例如,第一节点和第三节点)。

[0106]

通常,泵浦电容器的第一子集的最后一组包括泵浦电容器c

p

/2,其第一端子被耦合到第一电压节点集合a1,

…

,an中从n-m+1至n编号的m个中间电压节点的最后子序列中的奇数中间电压节点a

n-m+1

,a

n-m+3

,

…

,a

n-1

(例如,第一节点和第三节点),并且第二端子被耦合到第一电压节点集合a1,

…

,an中从n-2m+1至n-m编号的m个中间电压节点的倒数第二子序列中的对应奇数中间电压节点a

n-2m+1

,a

n-2m+3

,

…

,a

n-m-1

(例如,第一节点和第三节点)。泵浦电容器的第一子集的最后一组还包括泵浦电容器c

p

/2,其第一端子被耦合到第二电压节点集合b1,

…

,bn中从n-m+1至n编号的m个中间电压节点的最后子序列中的偶数中间电压节点b

n-m+2

,b

n-m+4

,

…

,bn(例如,第二节点和第四节点),并且第二端子被耦合到第二电压节点集合b1,

…

,bn中从n-2m+1至n-m编号的m个中间电压节点的倒数第二子序列中的对应偶数中间电压节点b

n-2m+2

,b

n-2m+4

,

…

,b

n-m

(例如,第二节点和第四节点)。

[0107]

通常,泵浦电容器的第二子集的最后一组包括泵浦电容器c

p

/2,其第一端子被耦合到第一电压节点集合a1,

…

,an中从n-m+1至n编号的m个中间电压节点的最后子序列中的偶数中间电压节点a

n-m+2

,a

n-m+4

,

…

,an(例如,第二节点和第四节点),并且第二端子被耦合到

第一电压节点集合a1,

…

,an中从n-2m+1至n-m编号的m个中间电压节点的倒数第二子序列中的对应偶数中间电压节点a

n-2m+2

,a

n-2m+4

,

…

,a

n-m

(例如,第二节点和第四节点)。泵浦电容器的第二子集的最后一组还包括泵浦电容器c

p

/2,其第一端子被耦合到第二电压节点集合b1,

…

,bn中从n-m+1至n编号的m个中间电压节点的最后子序列中的奇数中间电压节点b

n-m+1

,b

n-m+3

,

…

,b

n-1

(例如,第一节点和第三节点),并且第二端子被耦合到第二电压节点集合b1,

…

,bn中从n-2m+1至n-m编号的m个中间电压节点的倒数第二子序列中的对应奇数中间电压节点b

n-2m+1

,b

n-2m+3

,

…

,b

n-m-1

(例如,第一节点和第三节点)。

[0108]

注意,虽然图7的架构已具体参考每个子集中的第一组、第二组和最后一组泵浦电容器进行了描述,但泵浦电容器组的数目(即,数目k=n/m)可以根据设计规范而变化,每个组“堆叠”到前一组上(例如,参见图7中与节点a

i+1

,b

i+2

,a

i+3

,b

i+m

和b

i+1

,a

i+2

,b

i+3

,a

i+m

耦合的中间电容器组)。

[0109]

如果每个泵浦电容器c

p

/2的电容值是单分支架构的泵浦电容器c

p

的电容值的一半,则电压倍增器电路70的开路负载电压vo与等式(2)中报告的相同。单分支和双分支架构之间的电容总量没有变化,双分支架构包括2n*c

p

/2个电容器,而单分支架构包括n*c

p

个电容器。就倍增器输出上的电压纹波以及电容器和二极管中的电流峰值而言,图7中例示的双分支架构可能是有利的,相对于单分支架构减半。

[0110]

双分支电压倍增器70的操作类似于单分支架构的操作,其中跨泵浦电容器的电压减半,因为图7的架构对称并且对于给定的n级倍增器,泵浦电容器的数目是双倍的。

[0111]

在第一子集的第一泵浦电容器组中(直接连接到节点44a并且由信号v

ck

驱动)以及在第二子集的第一泵浦电容器组中(直接连接到节点44b并且由信号驱动),前两个泵浦电容器(分别耦合在节点44a和a1之间,以及节点44b和b1之间)以v

in-vd充电,第二泵浦电容器(分别耦合在节点44a和b2之间,以及节点44b和a2之间)以v

in

+v

ck-2vd充电,第三泵浦电容器(分别耦合在节点44a和a3之间,以及节点44b和b3之间)以v

in

+2v

ck-3vd充电,依此类推,直到第m泵浦电容器(在m为偶数的情况下,分别耦合在节点44a和bm之间,以及在节点44b和am之间;在m为奇数的情况下,分别耦合在节点44a和am之间,以及节点44b和bm之间)以v

in

+(m-1)

·vck-m

·vd

充电。与编号为m+1至n的中间电压节点耦合的其他组的泵浦电容器均以m

·

(v

ck-vd)充电。如等式(2)中针对已知倍增器和单分支架构所报告的,输出电容器在v

in

+n

·vck-(n+1)

·vd

下充电。

[0112]

注意,电压倍增器电路70的等效输出电阻可以根据以下等式(8)被计算为m级dickson倍增器和n/m级cockcroft-walton倍增器的组合,假设时钟周期比时间常数r

dcp

长得多,其中rd是二极管电阻:

[0113][0114]

关于硅尺寸,比较用于计算r

out

的等式(3)和(8),注意,如图7中的架构(以下也称为“混合双”架构)的尺寸可以被表示为:

[0115][0116]

在一个或多个实施例中(例如,在片上实现方式中),二极管d1,

…

,d

n+1

可以由图8

中例示的mos晶体管代替。应当注意,图8的电压倍增器电路80基本上对应于图4的架构,其中二极管d1,

…

,d

n+1

被mos晶体管m1,

…

,m

n+1

替换。mos晶体管可以是n沟道和/或p沟道,只要它们根据时钟信号v

ck

和的电流值被适当地驱动为从输入节点向输出节点导通。

[0117]

参考图9和图10解释图8中例示的电压倍增器电路80的操作。图9是在特别是当v

ck

=0(低值)且(高值)时,在时钟信号v

ck

和的前半周期期间,电路80中的电荷转移的示例。图10是特别是当v

ck

=v

ck

(高值)和(低值)时,在时钟信号v

ck

和的后半周期期间电路80中的电荷转移的示例。

[0118]

在前半个时钟周期中,当v

ck

为低且为高时,由信号v

ck

驱动的泵浦电容器通过由信号驱动的泵浦电容器以(更多)正电压充电,由信号驱动的泵浦电容器在上下文被放电。由v

ck

驱动的泵浦电容器借助奇数开关(mos晶体管)接收电荷“包”,奇数开关在该阶段处于导电状态(导通),而偶数开关(mos晶体管)处于非导电状态(关断)。在该阶段,第一泵浦电容器由输入电压v

in

直接充电。在后半个时钟周期,当v

ck

为高且为低时,由信号v

ck

驱动的泵浦电容器通过由信号驱动的泵浦电容器放电,由信号驱动的泵浦电容器在上下文中以更正的电压充电。由信号v

ck

驱动的泵浦电容器借助偶数开关(mos晶体管)提供电荷包,偶数开关在该阶段处于导电状态(导通),而奇数开关(mos晶体管)处于非导电状态(关断)。

[0119]

在直接连接到节点44a并由信号v

ck

驱动的第一泵浦电容器组中,第一泵浦电容器(耦合在节点44a和节点a1之间)以v

in

充电,第三泵浦电容器(耦合在节点44a和节点a3之间)以v

in

+2v

ck

充电,第五泵浦电容器(耦合在节点44a和节点a5之间)以v

in

+4v

ck

充电,依此类推,直到第(2m-1)泵浦电容器(耦合在节点44a和节点a5之间)以v

in

+(2m-2)

·vck

充电。在直接连接到节点44b并由信号驱动的第二泵浦电容器组中,第二泵浦电容器(耦合在节点44b和节点a2之间)以v

in

+v

ck

充电,第四泵浦电容器(耦合在节点44b和节点a4之间)以v

in

+3v

ck

充电,第六泵浦电容器(耦合在节点44b和节点a6之间)以v

in

+5v

ck

充电,依此类推,直到第2m泵浦电容器(耦合在节点44b和节点a

2m

之间)以v

in

+(2m-1)

·vck

充电。从2m+1到n的泵浦电容全部以2m

·vck

充电;这是跨电容器的两个端子的电压。开路负载输出电压vo在以下等式(10)中报告:

[0120]vo

=v

in

+n

·vck

ꢀꢀꢀ

(10)

[0121]

注意,如图8所示的电压倍增器电路80的等效输出电阻与等式(6)中定义的相同,假设时钟周期比时间常数r

mcp

长得多,其中rm是mos晶体管电阻。

[0122]

在一个或多个实施例中,如图11中所例示的,mos晶体管也可以被用于在双分支架构中替换二极管。应注意,图11的电压倍增器电路110基本上对应于图7的架构,其中使用mos晶体管替换二极管。mos晶体管可以是n沟道和/或p沟道,只要它们被适当地驱动(例如,根据参考图9和图10讨论的驱动方案,如果正输出电压被生成)。

[0123]

注意,如图11中例示的电压倍增器电路110的等效输出电阻与等式(8)中定义的相同,假设时钟周期远长于时间常数r

mcp

,其中rm为mos晶体管电阻。此外,如图11中例示的电

压倍增器电路110的开路负载电压vo与等式(10)中定义的相同。就倍增器输出上的电压纹波以及电容器和mos晶体管中的电流峰值而言,如图11中例示的双分支mos架构可能是有利的,相对于单分支mos架构减半。

[0124]

通常,用于生成正电压的双分支电压倍增器电路可以被实现为如图12的电路图所示。

[0125]

如图12中所例示的,电压倍增器电路120包括在输入节点40a和输出节点40b之间布置的n个电荷转移电路块130的链。如图13所示,每个电荷转移电路块130具有输入端子vd、输出端子vu、第一控制端子和第二控制端子。电荷转移电路块130包括电子组件(例如,二极管和/或晶体管),电子组件被布置为使得当两个反相的切换信号被施加到第一和第二控制端子时,电荷从输入端子vd转移到输出端子vu。具体地,根据在两个控制端子处接收的控制信号的值,电路块130可以在两种不同的换向状态下操作:在第一状态中,输入端子vd被耦合到第一控制端子并且输出端子vu被耦合到第二控制端子;在第二状态下,输入端子vd被耦合到第二控制端子,并且输出端子vu被耦合到第一控制端子。

[0126]

如图12中所例示的,每个电荷转移电路块130的第一控制端子和第二控制端子被配置为经由相应的泵浦电容器c

p

/2接收互补控制信号(例如,v

ck

和)。如图12中所例示的,n个电荷转移电路块130以数目k=n/m的子链布置,每个子链包括m个块130的串。

[0127]

在块130的第一子链中,每个块130的第一控制端子经由相应的泵浦电容器c

p

/2耦合到第一驱动输入节点44a,并且每个块130的第二控制端子经由相应的泵浦电容器c

p

/2被耦合到第二驱动输入节点44b。在块130的第二子链中,每个块130的第一控制端子经由相应的泵浦电容器c

p

/2而被耦合到第一子链中对应块130的第一控制端子,并且每个块130的第二控制端子经由相应的泵浦电容器c

p

/2而被耦合到第一子链中对应块130的第二控制端子。换言之,与第二子链中的块130耦合的泵浦电容器被堆叠至与第一子链中的块130耦合的泵浦电容器。

[0128]

子链的数目k与级数n和每个子链中的块的数目m相关。通常,在块130的第j子链中,每个块130的第一控制端子经由相应的泵浦电容器c

p

/2而被耦合到第(j-1)子链中对应块130的第一控制端子,并且每个块130的第二控制端子经由相应的泵浦电容器c

p

/2而被耦合到第(j-1)子链中对应块130的第二控制端子。

[0129]

例如,在一个或多个实施例中,每个电荷转移电路块130可以包括如图14中例示的布置。布置包括:第一n沟道晶体管n

l

,其具有在输入端子vd和第一控制端子之间的电流路径;第二n沟道晶体管n2,其具有在输入端子vd和第二控制端子之间的电流路径;第一p沟道晶体管p1,其具有在输出端子vu和第一控制端子之间的电流路径;以及第二p沟道晶体管p2,其具有在输出端子vu和第二控制端子之间的电流路径。第一n沟道晶体管n1和第一p沟道晶体管p1的栅极端子被耦合到第二控制端子,并且第二n沟道晶体管n2和第二p沟道晶体管p2的栅极端子被耦合到第一控制端子。

[0130]

在文献[pulvirenti]和[gariboldi 96]中公开了在锁存电荷泵中使用的这样的布置的操作,并且因此为了简洁起见,在此不再重复。

[0131]

一个或多个实施例可以被用于生成负电压。如图17的电路图所示,这可以例如通过如图15和图16的电路图中分别例示的反转图4和图7架构中的二极管的极性来获得,或者反转图8和图11的架构中的mos晶体管的激活信号的极性来获得,或者反转(例如,翻转)图

12的架构中的电荷转移电路块130的方向(例如,交换端子vu和vd)来获得。

[0132]

图15中例示的单分支负电压倍增器电路150的操作类似于图4中例示的单分支正电压倍增器电路40的操作,因此以下仅通过示例方式进行讨论。在前半个时钟周期中,当v

ck

为低且为高时,由信号v

ck

驱动的泵浦电容器(即,耦合到奇数中间电压节点a1,

…

,a

n-1

)被充电。它们借助偶数二极管从由信号驱动(即,耦合到偶数中间电压节点a2,

…

,an)的泵浦电容器接收电荷“包”,由信号驱动的泵浦电容器在上下文中以更负的电压放电。在后半时钟周期中,当v

ck

为高且为低时,由信号v

ck

驱动的泵浦电容器以更负的电压放电。它们借助奇数二极管将电荷包提供给由信号驱动的泵浦电容器,由信号驱动的泵浦电容器根据上下文充电。在该阶段中,第一泵浦电容器被直接放电到输入电压v

in

。

[0133]

第一泵浦电容器(耦合在节点44a和节点a1之间)以v

in-v

ck

+vd充电,第二泵浦电容器(耦合在节点44b和节点a2之间)以v

in-2v

ck

+2vd充电,第三泵浦电容器(耦合在节点44a和节点a3之间)以v

in-3v

ck

+3vd充电,依此类推。在单分支架构中,从2m到n的泵浦电容均以-2m

·

(v

ck-vd)充电;在双分支架构中,从m到n的泵浦电容器均以-m

·

(v

ck-vd)充电。开路负载输出电压vo在以下的等式(11)中报告:

[0134]vo

=v

in-n

·vck

+(n+1)

·vd

ꢀꢀꢀ

(11)

[0135]

注意,电压倍增器电路150的等效输出电阻与等式(6)中报告的相同。

[0136]

还应注意,将第一二极管连接到接地而不是连接到v

in

,输出电压变得更负。

[0137]

如图16中例示的双分支负电压倍增器160的操作类似于单分支负架构的操作,其中跨泵浦电容器的电压减半,并且为了简洁,本文中将不再描述。

[0138]

如图8中例示的基于mos晶体管架构的负电压倍增器电路的操作可以通过反转先前参考图9和图10解释的操作来获得,即,反转mos晶体管相对于时钟信号的两个半周期的激活阶段。在这种情况下,在前半个时钟周期中,当v

ck

为低且为高时,由信号v

ck

驱动的泵浦电容器通过由信号驱动的泵浦电容器充电,由信号驱动的泵浦电容器在上下文中以更负的电压放电。由v

ck

驱动的泵浦电容器借助偶数开关(mos晶体管)接收电荷“包”,偶数开关在该阶段中处于导电状态(导通),而奇数开关(mos晶体管)处于非导电状态(关断)。在第二半时钟周期,当v

ck

为高而为低时,由信号v

ck

驱动的泵浦电容器通过由信号驱动的泵浦电容器以更负的电压放电,由信号驱动的泵浦电容器根据上下文充电。由信号v

ck

驱动的泵浦电容器借助奇数开关(mos晶体管)提供电荷包,奇数开关在该阶段处于导电状态(导通),而偶数开关(mos晶体管)处于非导电状态(关断)。在该阶段,第一泵浦电容器被直接放电到输入电压v

in

。

[0139]

第一泵浦电容器(耦合在节点44a和节点a1之间)以v

in-v

ck

充电,第二泵浦电容器(耦合在节点44b和节点a2之间)以v

in-2v

ck

下充电,第三泵浦电容器(耦合在节点44a和节点a3之间)以v

in-3v

ck

下充电,依此类推。在单分支架构中,从2m到n的泵浦电容均以-2m

·vck

充电;在双分支架构中,从m到n的泵浦电容器均以-m

·vck

下充电。开路负载输出电压vo在以下

等式(12)中报告:

[0140]vo

=v

in-n

·vck

ꢀꢀꢀ

(12)

[0141]

等效输出电阻与等式(6)中定义的相同。

[0142]

具有mos晶体管的双分支负电压倍增器的操作与单分支的操作类似,因此为简洁起见不再进一步描述。

[0143]

在描述末尾处提供的表i和ii总结了本文讨论的电压倍增器电路的开路负载电压vo、输出电阻r

out

和总电容量c

tot

的公式。

[0144]

一个或多个实施例可以仅作为示例应用于针对mems(微机电系统)开关的单片八进制驱动器,其中驱动器的供电轨v

out

=70v从电源v

dd

=3.3v开始生成。例如,一个或多个实施例可以使用诸如soi-bcd6s技术的绝缘体上硅(soi)技术和具有12v操作电压的泵浦电容器来实现。考虑到3.0v的稳压电源,这样的示例性倍增器可以具有几乎n=24个级。此外,假设v

in

=v

ck

=3.0v,m可以被选择来将泵浦电容器的操作电压(例如,12v)除以稳压电源(例如,3.0v)。到目前为止,m可以等于4,因为泵浦电容器上的最大电压不会超过12v的操作值。根据等式(9),当m=1时,24个n级cockcroft-walton倍增器将比dickson大204倍,而根据m=4的等式(9),根据一个或多个实施例的具有24个n级和4个m级的倍增器将比dickson大15.2倍并且比cockcroft-walton小13.4倍。

[0145]

一个或多个实施例因此可以提供具有减小的硅面积占用的集成电压倍增器电路。

[0146]

在不损害基本原理的情况下,在不脱离保护范围的情况下,细节和实施例可以相对于仅以示例方式描述的内容变化甚至显著变化。

[0147]

保护范围由所附权利要求确定。

[0148]

表1

[0149]

倍增器类型具有二极管的倍增器具有mos晶体管的倍增器正电压vo=v

in

+n

·vck-(n+1)

·vdvo

=v

iv

+n

·vck

负电压vo=v

in-n

·vck

+(n+1)

·vdvo

=v

in-n

·vck

[0150]

表2

[0151]

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1