一种应用于全摆幅仪表放大器的电荷泵的制作方法

1.本发明属于运算放大器领域,具体属于一种应用于全摆幅仪表放大器的电荷泵。

背景技术:

2.集成电路产业是信息技术产业的核心,是支撑经济社会发展和保障国家安全的战略性、基础性和先导性产业。

3.随着电子技术的飞速发展,仪表放大器也得到广泛的应用,其中轨到轨全输入摆幅的仪表放大器应用十分广泛。然而,传统轨到轨仪表放大器的输入电压只能做到接近电源,因此使用电荷泵提高输入电压范围至超过电源电压十分有必要。

技术实现要素:

4.为了解决现有技术中存在的问题,本发明提供一种应用于全摆幅仪表放大器的电荷泵,能够输出低于供电电源的电压,从而实现仪表放大器在输入接近低电源电压时正常工作,实现仪表放大器轨到轨的输入能力。

5.为实现上述目的,本发明提供如下技术方案:

6.一种应用于全摆幅仪表放大器的电荷泵,包括nmos管n1、nmos管n2、 nmos管n3、nmos管n4、nmos管n5、nmos管n6、nmos管n7、nmos 管n8、nmos管n9、nmos管n10、电阻r1、电阻r2、电阻r3、电阻r4、电容c1、电容c2、电容c3和三极管q1;

7.所述nmos管n1的栅极与时钟信号clk2相连;nmos管n1的漏极与电阻r1的另一端相连;nmos管n1的源极与gnd相连;

8.所述nmos管n2的栅极与时钟信号clk2n相连;nmos管n2的漏极与电阻r2的另一端相连;nmos管n2的源极与gnd相连;

9.所述nmos管n3的栅极与时钟信号clk3n相连;nmos管n3的漏极与nmos管n4的漏极、电容c3的一端相连;所述nmos管n3的源极与电容c1的另一端、电阻r1的一端相连;

10.所述nmos管n4的栅极与时钟信号clk3相连;nmos管n4的漏极与 nmos管n3的漏极相连;nmos管n4的源极与电容c2的另一端、电阻r2 的一端相连;

11.所述nmos管n5的栅极与vb3相连;nmos管n5的漏极与pmos管 p2的漏极、电容c2的一端相连;nmos管n5的源极与nmos管n7的漏极相连;

12.所述nmos管n6的栅极与vb4相连;nmos管n6的漏极与pmos管 p1的漏极、电容c1的一端相连;nmos管n6的源极与nmos管n8的漏极相连;

13.所述nmos管n7的栅极与时钟信号clk3相连;nmos管n7的漏极与 nmos管n5的源极相连;nmos管n7的源极与nmos管n8的源极、nmos 管n9的漏极、nmos管n10的漏极相连;

14.所述nmos管n8的栅极与时钟信号clk3n相连;nmos管n8的漏极与nmos管n6的源极相连;nmos管n8的源极与nmos管n7的源极、nmos 管n9的漏极、nmos管n10的漏极相连;

15.所述nmos管n9的栅极与第一运放通路相连;nmos管n9的漏极与 nmos管n7的源极、nmos管n8的源极、nmos管n10的漏极相连;nmos 管n9的源极与gnd相连;

16.所述nmos管n10的栅极与第二运放通路相连;nmos管n10的漏极与 nmos管n7的源极、nmos管n8的源极、nmos管n9的漏极相连;nmos 管n10的源极与gnd相连;

17.所述pmos管p1的栅极与时钟信号clk1相连;pmos管p1的源极与 vdd相连;pmos管p1的漏极与nmos管n6的漏极、电容c1的一端相连;

18.所述pmos管p2的栅极与时钟信号clk1n相连;pmos管p2的源极与 vdd相连;pmos管p2的漏极与nmos管n5的漏极、电容c2的一端相连;

19.所述电阻r3的另一端与电阻r4的一端以及第一运放通路和第二运放通路相连,连接点为参考电压vref;所述电阻r4的一端与gnd相连;所述电容 c3的另一端与gnd相连;

20.所述npn三极管q1的基极与nmos管n3的漏极、nkos4的漏极、电容c3的一端相连;npn三极管q1的集电极与第一运放通路和第二运放通路相连;npn三极管q1的发射极与gnd相连。

21.优选的,所述第一运放通路包括pmos管p3、pmos管p4、pmos管p9、 nmos管n11和nmos管n12;

22.所述pmos管p3的栅极与npn三极管q1的集电极、pmos管p5的栅极、 pmos管p6的栅极相连;pmos管p3的源极与pmos管p9的漏极相连;pmos 管p3的漏极与nmos管n11的漏极、nmos管n11的栅极、nmos管n12 的栅极相连;

23.所述pmos管p4的栅极与电阻r3的另一端、电阻r4的一端、pmos管 p7的栅极、pmos管p8的栅极相连;pmos管p4的源极与pmos管p9的漏极相连;pmos管p4的漏极与nmos管n9的栅极、nmos管n12的漏极相连;

24.所述pmos管p9的栅极与vb1相连;pmos管p9的源极与vdd相连; pmos管p9的漏极与pmos管p3的源极、pmos管p4的源极相连;pmos 管p10的栅极与vb2相连;

25.所述nmos管n11的栅极与pmos管p3的漏极、nmos管n11的漏极、 nmos管n12的栅极相连;nmos管n11的漏极与pmos管p3的漏极、nmos 管n11的栅极、nmos管n12的栅极相连;nmos管n11的源极与gnd相连;

26.所述nmos管n12的栅极与pmos管p3的漏极、nmos管n11的漏极、 nmos管n11的栅极相连;nmos管n12的漏极与pmos管p4的漏极、nmos 管n9的栅极相连;nmos管n12的源极与gnd相连;nmos管n13的栅极与pmos管p6的漏极、nmos管n13的漏极、nmos管n14的栅极相连。

27.优选的,所述第二运放通路包括pmos管p5、pmos管p6、pmos管p7、 pmos管p8、pmos管p10、nmos管n13和nmos管n14;

28.所述pmos管p5的栅极与npn三极管q1的集电极、pmos管p3的栅极、pmos管p6的栅极相连;pmos管p5的源极与pmos管p10的漏极相连;pmos 管p5的漏极与pmos管p6的源极相连;

29.所述pmos管p6的栅极与npn三极管q1的集电极、pmos管p3的栅极、 pmos管p5的栅极相连;pmos管p6的源极与pmos管p5的漏极相连;pmos 管p6的漏极与nmos管n13的漏极、nmos管n13的栅极、nmos管n14 的栅极相连;

30.所述pmos管p7的栅极与电阻r3的另一端、电阻r4的一端、pmos管 p4的栅极、pmos管p8的栅极相连;pmos管p7的源极与pmos管p10的漏极相连;pmos管p7的漏极与nmos管n8的源极相连;

31.所述pmos管p8的栅极与电阻r3的另一端、电阻r4的一端、pmos管 p4的栅极、pmos管p7的栅极相连;pmos管p8的源极与pmos管p7的漏极相连;pmos管p8的漏极与nmos管n10的

栅极、nmos管n14的漏极相连;

32.所述pmos管p10的源极与vdd相连;pmos管p10的漏极与pmos管 p5的源极、pmos管p7的源极相连;

33.所述nmos管n13的漏极与pmos管p6的漏极、nmos管n13的栅极、 nmos管n14的栅极相连;nmos管n13的源极与gnd相连;

34.所述nmos管n14的栅极与pmos管p6的漏极、nmos管n13的漏极、nmos管n13的栅极相连;nmos管n14的漏极与pmos管p8的漏极、nmos 管n10的栅极相连;nmos管n14的源极与gnd相连。

35.优选的,所述时钟信号clk1与时钟信号clk1n、时钟信号clk2与时钟信号clk2n、时钟信号clk3与时钟信号clk3n均为反相的时钟信号。

36.优选的,所述时钟信号clk1和时钟信号clk2为占空比低于50%的方波信号。

37.优选的,所述时钟信号clk3为占空比为50%的方波信号。

38.优选的,所述参考电压vref=vdd*r4/(r3+r4)。

39.优选的,当时钟信号clk1为低电平、时钟信号clk2为高电平、时钟信号clk3为高电平,时钟信号clk1n为高电平、时钟信号clk2n为低电平、时钟信号clk3n为低电平时,pmos管p1、nmos管n1导通,nmos管n8 截止,电容c1进行充电;

40.当时钟信号clk1为高电平、时钟信号clk2为低电平、时钟信号clk3 为低电平、时钟信号clk1n为低电平、时钟信号clk2n为高电平、时钟信号 clk3n为高电平时,nmos管n8导通,pmos管p1、nmos管n1截止,电容c1上端电荷通过nmos管n7、nmos管n8、nmos管n9、nmos管n10 泄放,电容c1两端电压均降低,从而输出低于gnd的电压;电容c2与电容 c1交替完成充电、放电过程。

41.与现有技术相比,本发明具有以下有益的技术效果:

42.本发明提供一种应用于全摆幅仪表放大器的电荷泵,通过第一运放通路和第二运放通路以及nmos管n9、nmos管n10组成的反馈环路来决定vout 的电压。能够输出低于供电电源的电压,从而实现仪表放大器在输入接近低电源电压时正常工作,实现仪表放大器轨到轨的输入能力。通过第一运放通路的高速运放通路和第二运放通路的高精度运放通路两路共同反馈调节输出,既减小了建立时间,又提高了精度。

附图说明

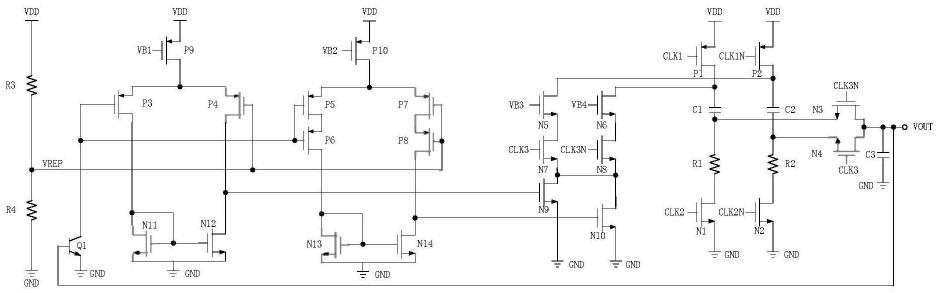

43.图1为本发明一种应用于全摆幅仪表放大器的电荷泵电路示意图。

具体实施方式

44.下面结合具体的实施例对本发明做进一步的详细说明,所述是对本发明的解释而不是限定。

45.实施例

46.本发明的一种应用于全摆幅仪表放大器的电荷泵,包括14个nmos管n 管,10个pmos管p管,4个电阻,3个电容,1个npn三极管。该电路能够输出低于供电电源的电压,从而实现仪表放大器在输入接近低电源电压时正常工作,实现仪表放大器轨到轨的输入能力。

47.如图1所示,nmos管n1的栅极与时钟信号clk2相连;nmos管n1 的漏极与电阻r1的

的源极相连;pmos管p6的栅极与npn三极管q1的集电极、pmos管p3的栅极、pmos管p5的栅极相连;pmos管p6的源极与pmos管p5的漏极相连;pmos管p6的漏极与nmos管n13的漏极、nmos管n13的栅极、nmos 管n14的栅极相连;pmos管p7的栅极与电阻r3的另一端、电阻r4的端;子1、pmos管p4的栅极、pmos管p8的栅极相连(该连线图中命名为vref)。

55.pmos管p7的源极与pmos管p10的漏极相连;pmos管p7的漏极与 nmos管n8的源极相连;pmos管p8的栅极与电阻r3的另一端、电阻r4 的一端、pmos管p4的栅极、pmos管p7的栅极相连(该连线图中命名为vref); pmos管p8的源极与pmos管p7的漏极相连;pmos管p8的漏极与nmos 管n10的栅极、nmos管n14的漏极相连;pmos管p9的栅极与vb1相连; pmos管p9的源极与vdd相连;pmos管p9的漏极与pmos管p3的源极、 pmos管p4的源极相连;pmos管p10的栅极与vb2相连;pmos管p10的源极与vdd相连;pmos管p10的漏极与pmos管p5的源极、pmos管p7 的源极相连。

56.电阻r1的一端与nmos管n3的源极、电容c1的另一端相连;电阻r1 的另一端与nmos管n1的漏极相连;电阻r2的一端与nmos管n4的源极、电容c2的另一端相连;电阻r2的另一端与nmos管n2的漏极相连;电阻r3的一端与vdd相连;电阻r3的另一端与pmos管p4的栅极、pmos管 p7的栅极、pmos管p8的栅极、电阻r4的一端相连(该连线图中命名为vref)。

57.电阻r4的一端与pmos管p4的栅极、pmos管p7的栅极、pmos管p8 的栅极、电阻r3的另一端相连(该连线图中命名为vref);电阻r4的一端与gnd相连;电容c1的一端与pmos管p1的漏极、nmos管n6的漏极相连;电容c1的另一端与nmos管n3的源极、电阻r1的一端相连;电容c2 的一端与pmos管p2的漏极、nmos管n5的漏极相连;电容c2的另一端与 nmos管n4的源极、电阻r2的一端相连;电容c3的一端与nmos管n3的漏极、nmos管n4的漏极、npn三极管q1的基极相连(该连线图中命名为 vout)。

58.电容c3的另一端与gnd相连;npn三极管q1的基极与nmos管n3的漏极、nkos4的漏极、电容c3的一端相连(该连线图中命名为vout);npn 三极管q1的集电极与pmos管p3的栅极、pmos管p5的栅极、pmos管p6 的栅极相连;npn三极管q1的发射极与gnd相连。

59.图1中时钟信号clk1与时钟信号clk1n,时钟信号clk2与时钟信号 clk2n,时钟信号clk3与时钟信号clk3n为反相的时钟信号,时钟信号clk1 和时钟信号clk2为占空比低于50%的方波信号,时钟信号clk3为占空比为 50%的方波信号。

60.电容c1和c2交替完成充电和放电过程,具体原理如下:当时钟信号clk1 为低电平、时钟信号clk2为高电平、时钟信号clk3为高电平(时钟信号 clk1n为高电平、时钟信号clk2n为低电平、时钟信号clk3n为低电平) 时,pmos管p1、nmos管n1导通,nmos管n8截止,电容c1进行充电;当时钟信号clk1为高电平、时钟信号clk2为低电平、时钟信号clk3为低电平(时钟信号clk1n为低电平、时钟信号clk2n为高电平、时钟信号clk3n 为高电平)时,nmos管n8导通,pmos管p1、nmos管n1截止,电容c1 上端电荷通过nmos管n7、nmos管n8、nmos管n9、nmos管n10泄放,电容c1两端电压均降低,从而输出低于gnd的电压;电容c2与c1交替完成充电、放电过程。

61.电荷泵输出的低电平由vref决定,vout=vref-vbe,vref由电阻r3、 r4分压决定,vref=vdd*r4/(r3+r4)。

62.vout由vref决定的原理为:该电路使用由pmos管p3、pmos管p4、 pmos管p9、nmos管n11、nmos管n12组成的高速运放通路和由pmos 管p5、pmos管p6、pmos管p7、pmos管p8、pmos

管p10、nmos管n13、 nmos管n14组成的高精度运放通路及nmos管n9、nmos管n10组成的反馈环路来决定vout的电压。当vout>vref-vbe时,nmos管n9、nmos 管n10的栅极电压升高,流经nmos管n9、nmos管n10的电流增大,电容 c1、c2放电时电压降低,输出电压vout降低,从而实现vout=vref-vbe;当vout<vref-vbe时,nmos管n9、nmos管n10的栅极电压降低,流经nmos管n9、nmos管n10的电流减小,电容c1、c2放电时电压升高,输出电压vout升高,从而实现vout=vref-vbe。

63.本发明的电路中通过vref和vbe来决定电荷泵输出电压,可以自行设计分压电阻r3和r4的阻值,确定参考电压vref,从而确定输出电压vout。

64.本发明通过高速运放通路和高精度运放通路两路共同反馈调节输出,既减小了建立时间,又提高了精度。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1