一种双指数脉冲电流倍增充放电系统和方法与流程

1.本发明属于脉冲电流技术领域,具体涉及一种脉冲电流倍增充放电系统和方法。

背景技术:

2.双指数脉冲电流是单指数脉冲电流通过带电容电路后形成的,其可作为传导电流作用在电子元件上,现有技术中一般采用rlc串联放电电路,图1为其等效电路图,当置地电阻rf 为电阻性负载时,输出波形为双指数脉冲,从发生脉冲电流的过程看,如果想输出大电流, 1.增大源电压即高压直流电源的驱动能力;2.增大储能电容的容值。增大源电压的驱动力则需要加强电路中电阻和电容的绝缘能力,成本较高,且不能无限增大源电压的驱动力;增大储能电容的容值则会导致放电时间延长,不满足脉冲半波宽的要求。并且整体上对高压直流电源的性能和整个系统的绝缘耐压要求更加严苛。

技术实现要素:

3.本发明实施方式的目的在于提供的一种脉冲电流倍增充放电系统和方法,解决了现有技术中增大储能电容的容值会导致放电时间延长,不满足脉冲半波宽的要求,以及增大源电压需要更换绝缘能力更强的电阻和电容,且无法无限增加源电压的问题。

4.为解决上述技术问题,本发明的实施方式提供了一种脉冲电流倍增充放电系统,包括包括直流电源,充电电阻rs,成形电路以及置地电阻rg,所述直流电源的输出端与充电电阻 rs的输入端连接,所述充电电阻rs的输出端与成形电路的输入端连接,所述成形电路的输出端与用电元件和置地电阻连接,所述成形电路与用电元件之间设置有输出开关s1。

5.进一步,所述成形电路包括第一成形电路,所述第一成形电路包括成形电阻r1、成形电容c1,所述成形电阻r1的输入端与充电电阻rs的输出端连接,所述成形电容c1一端与充电电阻rs的输出端、成形电阻r1连接,所述成形电容c1另一端接地,所述成形电阻r1的输出端与输出开关s1连接。

6.进一步,所述成形电路包括第一成形电路,所述第一成形电路包括成形电阻r1、成形电容c1,所述成形电阻r1的输入端与充电电阻rs的输出端连接,所述成形电容c1一端与充电电阻rs的输出端、成形电阻r1连接,所述成形电容c1另一端接地,所述成形电阻r1的输出端与输出开关s1连接。

7.进一步,所述成形电路还包括多条并联的第二成形电路,所述第二成形电路包括成形电阻r2、成形电容c2,所述成形电阻r2一端与成形电阻r1的输出端连接,所述成形电阻r2 另一端与成形电容c2一端连接,所述成形电容c2另一端接地,所述成形电阻r2与输出开关 s1连接。

8.进一步,所述直流电源为高压直流电源。

9.进一步,当所述输出开关s1断开时,所述成形电阻r1与成形电阻r2串联。

10.进一步,当所述输出开关s1闭合时,所述成形电阻r1与成形电阻r2并联。

11.进一步,所述直流电源的输出电流小于用电元件的输入电流。

12.本发明的实施方式还提供一种脉冲电流倍增充放电方法,以下步骤:

13.s1:检测成形电容c1和成形电容c2的初始电压值,若成形电容c1和成形电容c2的电压值低于预设值,则进入步骤s2,反之,则进入步骤s3;

14.s2:控制输出开关s1断开,直流电源输出电流对成形电容c1和成形电容c2充电;

15.s3:控制输出开关s1闭合,成形电容c1输出电流对成形电阻r1充电,成形电容c2输出电流对成形电阻r2充电,当成形电容c1和成形电容c2的电容值低于预设值时,则进入步骤s1。

16.有益效果:

17.1.本脉冲电流倍增充放电系统只需要使用现有元件,组成的电路即可成倍数的提高脉冲电流的输出能力,并且系统元件的参数均可沿用已有的技术指标,保证元件性能的稳定性。

18.2.再输出同样的脉冲电流是,本发明的整体降低了脉冲电流倍增充放电系统的耐压等级。

19.3.多电容的并联可明显减少电容的杂散电感和等效电阻,减少了干扰系统的分布参数,有利于减少脉冲触发的上升时间,脉冲输出更加稳定,波形更平滑。

附图说明

20.一个或多个实施例通过与之对应的附图中的图片进行示例性说明,这些示例性说明并不构成对实施例的限定。

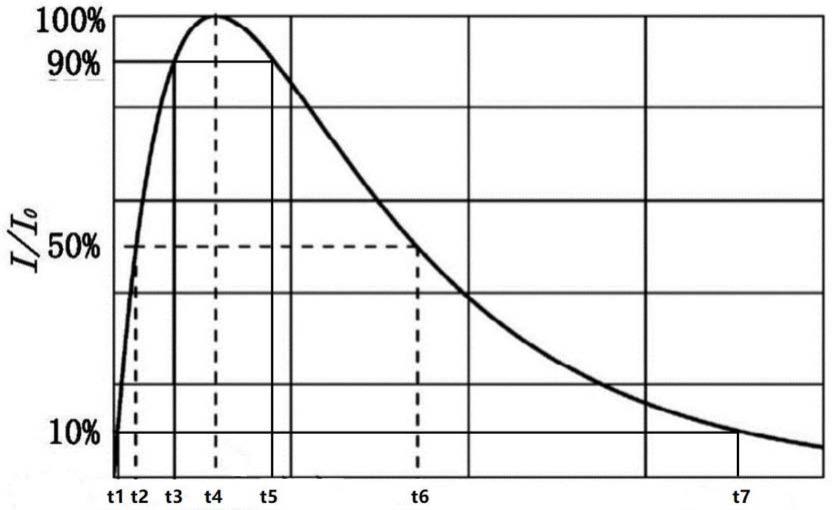

21.图1为双指数脉冲电流的波形图;

22.图2为常规rlc串联放电电路的电路图;

23.图3为双指数脉冲校准电流生成电路等效电路图;

24.图4为本发明一种脉冲电流倍增充放电系统的电路图。

具体实施方式

25.为使本发明实施例的目的、技术方案和优点更加清楚,下面将结合附图对本发明的各实施方式进行详细的阐述。然而,本领域的普通技术人员可以理解,在本发明各实施方式中,为了使读者更好地理解本技术而提出了许多技术细节。但是,即使没有这些技术细节和基于以下各实施方式的种种变化和修改,也可以实现本技术所要求保护的技术方案。

26.如图1所示,为双指数脉冲电流的波形图,横坐标表示时间,纵坐标表示实时电流与峰值电流的比值,由图可知,电流波形的主要参数有电流峰值i0、上升时间tr、衰落时间tf和半峰宽t

0.5

,该主要参数对双指数脉冲电流的产生具有重要影响。

27.tr=t

3-t1,r∈n,n为正整数

28.tf=t

7-t529.t

0.5

=t

6-t230.i(t)=ki0(e-αt-e-βt

)

31.其中:i(t)表示实时电流,tr表示第r时刻。

32.如图2所示,为生成双指数脉冲电流采用的常规rlc串联放电电路的原理图,由图可知,充电阶段开关s断开,直流高压源为成形电容c充电;放电阶段开关s瞬间闭合,成形电

容 c通过成形电阻r和负载放电,产生的电流注入至负载;这个电路的校准电流为负载短路时的电流。

33.如图3所示,为双指数脉冲校准电流生成电路等效电路图,其电路方程为:

[0034][0035]

其中:c表示成形电容,l表示电路的总分布电感,r表示成形电阻。

[0036][0037][0038][0039]

τ1=l/r

[0040]

τ2=rc

[0041]

其中:u0表示直流高压源输出电压。

[0042]

此时电流波形为双指数脉冲波形,根据上式计算的电流峰值i0、上升时间tr、衰落时间tf和半峰宽t

0.5

与成形电容c和成形电阻r满足如下关系:

[0043][0044][0045]

tf≈2.2τ2=2.2rc

[0046]

t

0.5

≈0.7cr

[0047]

由上式可知,要产生快上升时间的大电流,需要在不改变成形电阻r的基础上,增大高压直流源输出电压u0并减小电路总分布电感l。增大高压直流源输出电压u0就需要加大成形 c、成形电阻r和开关s的绝缘能力。减小电路总分布电感l需要减小电路形成的环路的面积,为保证元器件之间的绝缘性能,就需要器件之间保持足够的距离,电压增大的情况下环路面积无法缩小。

[0048]

具体实施方式一

[0049]

如图4所示,本发明提供了一种脉冲电流倍增充放电系统,本系统在常规rlc串联放电电路上进行了改进,包括:直流电源v,充电电阻rs,成形电路以及置地电阻rg,该直流电源v采用高压直流电源,成形电路包括第一成形电路和多条并联的第二成形电路,第一成形电路包括成形电阻r1、成形电容c1,第二成形电路包括成形电阻r2、成形电容c2,直流电源的输出端与充电电阻rs的输入端连接,充电电阻rs的输出端与成形电阻r1的输入端连接,成形电容c1一端与充电电阻rs的输出端、成形电阻r1连接,成形电容c1另一端接地,成形电阻r1的输出端与用电元件连接,成形电阻r1与用电元件之间设置有输出开关s1连接,成形电阻r2一端与成形电阻r1的输出端连接,成形电阻r2另一端与成形电容c2一端连接,成形电容c2另一端接地,成形电阻r2与输出开关s1连接。可以理解为:第二成形电路的数量

可以根据需要的电流大小进行具体设定,每多增加一条,则增加一条串联的成形电阻ri和成形电容ci,i∈(2,n)。

[0050]

如图4所示,输出开关s1断开时,成形电阻ri相互之间串联,此时为充电状态,通过直流电源对多组成形电容充电,具体充电路径为高压直流电源产生的充电电流is经过充电电阻rs对成形电容c1充电;高压直流电源产生的充电电流is经过充电电阻rs、成形电阻r1,成形电阻r2对成形电容c2充电,高压直流电源产生的充电电流is经过充电电阻rs、成形电阻r1,成形电阻r3对成形电容c3充电,高压直流电源产生的充电电流is经过充电电阻 rs、成形电阻r1,成形电阻r4对成形电容c4充电,高压直流电源产生的充电电流is经过充电电阻rs、成形电阻r1,成形电阻rn对成形电容cn充电,同时由图可知,该充电过程并非每条支路对称并联的对各个电容充电。可以理解为:采用非对称结构,由一个电容和一个电阻串联组成一个成型电路,多个成型电路并联降低了回路中的杂散电感;杂散电感的降低,减少了产生脉冲的上升时间tr。

[0051]

如图4所示,输出开关s1闭合时,成形电阻ri相互之间并联,此时为放电状态,首先高压直流电源产生的充电电流is经过充电电阻rs、成形电阻r1然后输出至用电元件,同时成形电容c1对成形电阻r1进行放电,成形电容c2对成形电阻r2进行放电,成形电容c3对成形电阻r3进行放电,成形电容c4对成形电阻r4进行放电,成形电容cn对成形电阻rn进行放电,n条之路形成n倍的电流,由此形成输出电流的倍增。多电容的并联可明显减少电容的杂散电感和等效电阻,减少了干扰系统的分布参数,有利于减少脉冲触发的上升时间,脉冲输出更加稳定,波形更平滑。

[0052]

具体实施方式二

[0053]

一种脉冲电流倍增充放电方法,包括以下步骤:

[0054]

s1:检测成形电容c1和成形电容c2的初始电压值,若成形电容c1和成形电容c2的电压值低于预设值,则进入步骤s2,反之,则进入步骤s3;

[0055]

s2:控制输出开关s1断开,直流电源输出电流对成形电容c1和成形电容c2充电;

[0056]

s3:控制输出开关s1闭合,成形电容c1输出电流对成形电阻r1充电,成形电容c2输出电流对成形电阻r2充电,当成形电容c1和成形电容c2的电容值低于预设值时,则进入步骤s1。

[0057]

以上所述的仅是本发明的实施例,方案中公知的具体结构及特性等常识在此未作过多描述,所属领域普通技术人员知晓申请日或者优先权日之前发明所属技术领域所有的普通技术知识,能够获知该领域中所有的现有技术,并且具有应用该日期之前常规实验手段的能力,所属领域普通技术人员可以在本技术给出的启示下,结合自身能力完善并实施本方案,一些典型的公知结构或者公知方法不应当成为所属领域普通技术人员实施本技术的障碍。应当指出,对于本领域的技术人员来说,在不脱离本发明结构的前提下,还可以作出若干变形和改进,这些也应该视为本发明的保护范围,这些都不会影响本发明实施的效果和专利的实用性。本技术要求的保护范围应当以其权利要求的内容为准,说明书中的具体实施方式等记载可以用于解释权利要求的内容。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1