一种HERIC逆变电路的制作方法

一种heric逆变电路

技术领域

1.本发明涉及逆变电路,尤其涉及一种heric逆变电路。

背景技术:

2.heric逆变拓扑是一种高效可靠逆变拓扑,是应用于单相逆变器的主要拓扑之一,由于其多出两个续流管,整个拓扑的开关管的保护电路也变得复杂。

3.在逆变拓扑中,功率半导体开关管总是成对称地出现,其开关导通时间为逻辑互补关系,即成对称关系的开关管,在某一开关管导通时,另一开关管就必须要关断,若对称关系的开关管同时导通,就相当于开关管将直流母线短路,将会损坏开关管。开关管的导通与关断完全受驱动信号的控制,因此控制好对称关系的开关管的逻辑互补驱动信号就可以对开关管起到保护作用。

4.通常功率半导体开关管的驱动电压比控制芯片cpu发出的驱动信号的电压高得多,以igbt为例,其较佳导通电压为+15v,关断为-5v,控制芯片发出的信号通常只有3-5v,因而需要用隔离电路将控制芯片的低电压驱动信号转换成较高电压的驱动信号。因为驱动信号是逻辑互补的,其在传送到隔离电路的过程中,有可能受到干扰,或者因为元器件的损坏而使得两路驱动信号都变为有效电平,如果此时的隔离电路没有加入带保护功能的电路,就可能输出两路同时有效的驱动信号,导致两个开关管同时导通,引发开关管因短路而损坏。

5.heric逆变拓扑比全桥逆变拓扑多出了两个续流管,续流管的驱动信号也与桥臂的驱动信号逻辑互补,桥臂开关管与其驱动信号逻辑互补的续流管在同时导通的情况下,也可能导致整个拓扑损坏。

技术实现要素:

6.本发明要解决的技术问题是提供一种安全性能好的heric逆变电路。

7.为了解决上述技术问题,本发明采用的技术方案是,一种heric逆变电路,包括主电路和控制电路,主电路包括由两对对角的开关管组成的h桥电路和反向串联的两个续流管组成的续流电路,控制电路包括复数个驱动电路,复数个驱动电路包括第一对对角的开关管驱动电路、第二对对角开关管的驱动电路、第一续流管驱动电路和第二续流管驱动电路;第一对对角的开关管驱动电路由第一pwm信号驱动,第二续流管驱动电路的驱动由第四pwm信号驱动,第一对对角的开关管驱动电路的电源输入端通过第四pwm信号钳位;第二对对角的开关管驱动电路的驱动由第二pwm信号驱动,第一续流管驱动电路由第三pwm信号驱动,第二对对角的开关管驱动电路的电源输入端通过第三pwm信号钳位;驱动电路输入的驱动信号信号低电平为有效,在heric逆变电路输出电压的正半周,第一pwm信号与第四pwm信号逻辑互补,第二pwm信号为高电平,第三pwm信号为低电平;在heric逆变电路输出电压的负半周,第二pwm信号与第三pwm信号逻辑互补,第一pwm信号为高电平,第四pwm信号为低电平。

8.以上所述的heric逆变电路,驱动电路包括光耦,所述的光耦为图腾柱输出型光耦;第一对对角的开关管驱动电路光耦原边的电源输入端通过第一限流电阻接辅助电源,并通过第一钳位电路接第四pwm信号,第一对对角的开关管驱动电路光耦原边的信号输入端接第一pwm信号;第二续流管驱动电路光耦原边的电源输入端通过第二限流电阻接辅助电源,第二续流管驱动电路光耦原边的信号输入端接第四pwm信号;第二对对角的开关管驱动电路光耦原边的电源输入端通过第三限流电阻接辅助电源,并通过第二钳位电路接第三pwm信号,第二对对角的开关管驱动电路光耦原边的信号输入端接第二pwm信号;第一续流管驱动电路光耦原边的电源输入端通过第四限流电阻接辅助电源,第一续流管驱动电路光耦原边的信号输入端接第三pwm信号。

9.以上所述的heric逆变电路,所述的开关管和续流管为igbt管,第一对对角的开关管包括第一开关管和第四开关管,第二对对角的开关管包括第二开关管和第三开关管;第一开关管的集电极和第三开关管的集电极接直流正母线,第二开关管的发射极和第四开关管的发射极接直流负母线;第一开关管的发射极接第二开关管的集电极,第三开关管的发射极接第四开关管的集电极;第一续流管的发射极接第一开关管的发射极,第一续流管的集电极接第二续流管的集电极,第二续流管的发射极接第四开关管的集电极;输出滤波电容的一端接第一续流管的发射极,另一端接第二续流管的发射极;逆变电感串接在第一续流管的发射极、第二续流管的发射极以及输出滤波电容之间。

10.以上所述的heric逆变电路,驱动电路包括npn三极管、pnp三极管,电源输入正引脚、电源输入负引脚和驱动信号输出引脚,光耦副边的电源输入端接电源输入正引脚,光耦副边的接地端接电源输入负引脚;npn三极管的集电极接电源输入正引脚,npn三极管的发射极接pnp三极管的集电极,pnp三极管的发射极接电源输入负引脚;npn三极管的基极和pnp三极管的基极接光耦副边的信号输出端,npn三极管的发射极接驱动信号输出引脚。

11.以上所述的heric逆变电路,第一对对角的开关管驱动电路包括第一开关管驱动电路和第四开关管驱动电路,第一开关管驱动电路光耦原边的电源输入端通过第五限流电阻接辅助电源,并接第一钳位二极管的阳极,第一钳位二极管的阴极接第四pwm信号;第一开关管驱动电路光耦原边的信号输入端接第一pwm信号,第一开关管驱动电路的电源输入正引脚接第一隔离电源正极、电源输入负引脚接第一隔离电源负极,驱动信号输出引脚接第一开关管的门极;第四开关管驱动电路光耦原边的电源输入端通过第六限流电阻接辅助电源,并接第二钳位二极管的阳极,第二钳位二极管的阴极接第四pwm信号;第四开关管驱动电路光耦原边的信号输入端接第一pwm信号,第四开关管驱动电路的电源输入正引脚接第五隔离电源正极、电源输入负引脚接第五隔离电源负极,驱动信号输出引脚接第四开关管的门极。

12.以上所述的heric逆变电路,第二对对角的开关管驱动电路包括第二开关管驱动电路和第三开关管驱动电路,第二开关管驱动电路光耦原边的电源输入端通过第七限流电阻接辅助电源,并接第三钳位二极管的阳极,第三钳位二极管的阴极接第三pwm信号;第二开关管驱动电路光耦原边的信号输入端接第二pwm信号,第二开关管驱动电路的电源输入正引脚接第五隔离电源正极、电源输入负引脚接第五隔离电源负极,驱动信号输出引脚接第二开关管的门极;第三开关管驱动电路光耦原边的电源输入端通过第八限流电阻接辅助电源,并接第四钳位二极管的阳极,第四钳位二极管的阴极接第三pwm信号;第三开关管驱

动电路光耦原边的信号输入端接第二pwm信号,第三开关管驱动电路的电源输入正引脚接第三隔离电源正极、电源输入负引脚接第三隔离电源负极,驱动信号输出引脚接第三开关管的门极。

13.以上所述的heric逆变电路,第一续流管驱动电路光耦原边的电源输入端通过第九限流电阻接辅助电源,第一续流管驱动电路的电源输入正引脚接第四隔离电源正极、电源输入负引脚接第四隔离电源负极,驱动信号输出引脚接第一续流管的门极;第二续流管驱动电路光耦原边的电源输入端通过第十限流电阻接辅助电源,第二续流管驱动电路的电源输入正引脚接第二隔离电源正极、电源输入负引脚接第二隔离电源负极,驱动信号输出引脚接第二续流管的门极。

14.本发明可以防止开关管与逻辑互补的续流管同时导通,电路的安全性好。

附图说明

15.下面结合附图和具体实施方式对本发明作进一步详细的说明。

16.图1是本发明实施例heric逆变电路的电路图。

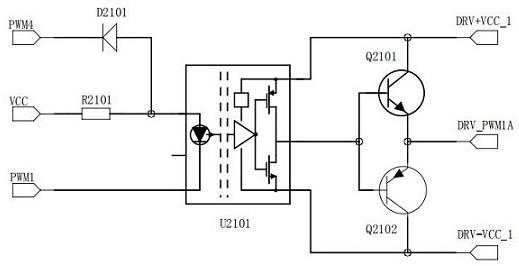

17.图2是本发明实施例第一开关管驱动电路的电路图。

18.图3是本发明实施例第四开关管驱动电路的电路图。

19.图4是本发明实施例第一续流管驱动电路的电路图。

20.图5是本发明实施例第三开关管驱动电路的电路图。

21.图6是本发明实施例第二开关管驱动电路的电路图。

22.图7是本发明实施例第二续流管驱动电路的电路图。

23.图8是本发明实施例heric逆变电路的驱动波形图。

具体实施方式

24.本发明实施例heric逆变电路的结构和原理如图1至图8所示,包括主电路和控制电路。

25.如图1所示,主电路包括由两对对角的开关管组成的h桥电路和反向串联的两个续流管组成的续流电路,开关管和续流管为igbt管,第一对对角的开关管包括第一开关管q101和第四开关管q104,第二对对角的开关管包括第二开关管q102和第三开关管q103。第一开关管q101的集电极和第三开关管q103的集电极接直流正母线bus_+,第二开关管q102的发射极和第四开关管q104的发射极接直流负母线bus_n。第一开关管q101的发射极接第二开关管q102的集电极,第三开关管q103的发射极接第四开关管q104的集电极。第一续流管q105的发射极接第一开关管q101的发射极,第一续流管q105的集电极接第二续流管q106的集电极,第二续流管q106的发射极接第四开关管q104的集电极。第一续流管q105的发射极通过逆变电感l1101接输出滤波电容c1101的第一端,输出滤波电容c1101的第二端通过逆变电感l1102串接第二续流管q106的发射极。

26.控制电路包括6个驱动电路,驱动电路包括图腾柱输出型光耦。npn三极管、pnp三极管,电源输入正引脚、电源输入负引脚和驱动信号输出引脚,光耦副边的电源输入端接电源输入正引脚,光耦副边的接地端接电源输入负引脚。npn三极管的集电极接电源输入正引脚,npn三极管的发射极接pnp三极管的集电极,pnp三极管的发射极接电源输入负引脚。npn

三极管的基极和pnp三极管的基极接光耦副边的信号输出端,npn三极管的发射极接驱动信号输出引脚。

27.6个驱动电路包括第一对对角的开关管的驱动电路、第二对对角开关管的驱动电路、第一续流管q105的驱动电路和第二续流管q106的驱动电路。第一对对角的开关管的驱动电路包括第一开关管q101的驱动电路和第四开关管q104的驱动电路,第二对对角的开关管的驱动电路包括第二开关管q102的驱动电路和第三开关管q103的驱动电路。

28.6个驱动电路具有基本相同的结构,以第一开关管q101的驱动电路为例进行说明:如图2所示,第一开关管q101的驱动电路包括图腾柱输出型光耦u2101。npn三极管q2101、pnp三极管q2102,电源输入正引脚、电源输入负引脚和驱动信号输出引脚,光耦u2101副边的电源输入端接电源输入正引脚,光耦u2101副边的接地端接电源输入负引脚。npn三极管q2101的集电极接电源输入正引脚,npn三极管q2101的发射极接pnp三极管q2102的集电极,pnp三极管q2102的发射极接电源输入负引脚。npn三极管q2101的基极和pnp三极管q2102的基极接光耦u2101副边的信号输出端,npn三极管q2101的发射极接驱动信号输出引脚。

29.如图2所示,光耦u2101原边的电源输入端通过限流电阻r2101接辅助电源vcc,并接第一钳位二极管d2101的阳极,第一钳位二极管d2101的阴极接第四pwm信号pwm4。光耦u2101原边的信号输入端接第一pwm信号pwm1,电源输入正引脚接第一隔离电源正极drv+vcc_1、电源输入负引脚接第一隔离电源负极drv-vcc_1,驱动信号输出引脚接第一开关管q101的门极drv_pwm1a。

30.第四开关管q104的驱动电路如图3所示,光耦u2201原边的电源输入端通过限流电阻r2201接辅助电源vcc,并接第二钳位二极管d2201的阳极,第二钳位二极管d2201的阴极接第四pwm信号pwm4。光耦u2201原边的信号输入端接第一pwm信号pwm1,电源输入正引脚接第五隔离电源正极drv+vcc、电源输入负引脚接第五隔离电源负极drv-vcc,驱动信号输出引脚接第四开关管q104的门极drv_pwm1b。

31.第二续流管q106的驱动电路如图4所示,光耦u2301原边的电源输入端通过限流电阻r2301接辅助电源vcc,光耦u2301原边的信号输入端接第四pwm信号pwm4第二续流管q106驱动电路的电源输入正引脚接第二隔离电源正极drv+vcc_2、电源输入负引脚接第二隔离电源负极drv-vcc_2,驱动信号输出引脚接第二续流管q106的门极drv_pwm4。

32.第二开关管q102的驱动电路如图5所示,光耦u2401原边的电源输入端通过限流电阻r2401接辅助电源vcc,并接第三钳位二极管d2401的阳极,第三钳位二极管d2401的阴极接第三pwm信号pwm3。光耦u2401原边的信号输入端接第二pwm信号pwm2,电源输入正引脚接第五隔离电源正极drv+vcc、电源输入负引脚接第五隔离电源负极drv-vcc,驱动信号输出引脚接第二开关管q102的门极drv_pwm2b。

33.第三开关管q103的驱动电路如图6所示,光耦u2501原边的电源输入端通过限流电阻r2501接辅助电源vcc,并接第四钳位二极管d2501的阳极,第四钳位二极管d2501的阴极接第三pwm信号pwm3。光耦u2501原边的信号输入端接第二pwm信号pwm2,电源输入正引脚接第三隔离电源正极drv+vcc_3、电源输入负引脚接第三隔离电源负极drv-vcc_3,驱动信号输出引脚接第三开关管q103的门极drv_pwm2a。

34.第一续流管q105的驱动电路如图7所示,光耦u2601原边的电源输入端通过限流电阻r 2601接辅助电源vcc,光耦u2601原边的信号输入端接第三pwm信号pwm3第一续流管

q105驱动电路的电源输入正引脚接第四隔离电源正极drv+vcc_4、电源输入负引脚接第四隔离电源负极,驱动信号输出引脚接第一续流管q105的门极drv_pwm3。

35.在heric逆变电路输出电压的正半周,第一pwm信号pwm1与第四pwm信号pwm4逻辑互补,第二pwm信号pwm2为高电平,第三pwm信号pwm3为低电平。在heric逆变电路输出电压的负半周,第二pwm信号pwm2与第三pwm信号pwm3逻辑互补,第一pwm信号pwm1为高电平,第四pwm信号pwm4为低电平。光耦原边的信号输入端输入的pwm信号低电平为有效信号,高电平为无效信号。

36.如图8所示,第一开关管q101的驱动信号drv_pwm1a和第四开关管q104的驱动信号drv_pwm1b与第二续流管q106的驱动信号drv_pwm4逻辑互补,第一续流管q105的驱动信号drv_pwm3为高电平,第二开关管q102的驱动信号drv_pwm2b和第三开关管q103的驱动信号drv_pwm2a为低电平。在heric逆变电路输出电压的负半周,第二开关管q102的驱动信号drv_pwm2b和第三开关管q103的驱动信号drv_pwm2a与第一续流管q105的驱动信号drv_pwm3逻辑互补,第二续流管q106的驱动信号drv_pwm4为高电平,第一开关管q101的驱动信号drv_pwm1a和第四开关管q104的驱动信号drv_pwm1b为低电平。

37.在逆变电压的正半周,当全桥拓扑对角管的第一开关管q101和第四开关管q104导通时,母线电压bus_+经第一开关管q101、lc滤波,流过负载rl,从第四开关管q104流回bus_n。当第一开关管q101和第四开关管q104截止时,逆变电感l1101和l1102的电流可流经第二续流管q106的体二极管和第一续流管q105实现续流,续流时与直流母线完全断开,可以有效地降低系统的共模干扰。

38.在逆变电压的负半周,当全桥拓扑对角管的第二开关管q102和第三开关管q103导通时,母线电压bus_+经第三开关管q103、lc滤波,流过负载rl,从第二开关管q102流回bus_n。当第二开关管q102和第三开关管q103截止时,逆变电感l1101和l1102的电流可流经第一续流管q105的体二极管和第二续流管q106实现续流,续流时与直流母线完全断开,有效地降低了系统的共模干扰。

39.就开关管的开关而言,第一开关管q101和第四开关管q104导通时,第二续流管q106不能导通,否则母线电压bus_+的电压经第一开关管q101,会通过第一续流管q105的体二极管,流经第二续流管q106和第四开关管q104回到bus_n,相当于直流母线短路。而第二开关管q102和第三开关管q103导通时,第一续流管q105不能导通,否则母线电压bus_+的电压经第三开关管q103,会通过第二续流管q106的体二极管,流经第一续流管q105和第二开关管q102回到bus_n,相当于直流母线短路。即,全桥拓扑第一对角管的第一开关管q101和第四开关管q104与续流管第二续流管q106的驱动信号逻辑互补,第一开关管q101、第四开关管q104导通时第二续流管q106截止,第一开关管q101、第四开关管q104截止时第二续流管q106导通;全桥拓扑第二对角管的第二开关管q102和第三开关管q103与续流管第一续流管q105的驱动信号逻辑互补,第二开关管q102、第三开关管q103导通时第一续流管q105截止,第二开关管q102、第三开关管q103截止时第一续流管q105导通。

40.本发明以上实施例的heric逆变电路当第一开关管q101的驱动电路和第四开关管q104的驱动电路的驱动信号pmw1为低电平时,在第一开关管q101的驱动电路中,电流从辅助电源vcc流经限流电阻r2101和光耦u2101的 原边二极管,通过pwm1低阻通路流回辅助电源vcc的参考地,光耦u2101的电源输入正引脚则接通第一隔离电源正极drv+vcc_1。在第四

开关管q104的驱动电路中,电流从辅助电源vcc流经限流电阻r2201和光耦u2201原边二极管,通过pwm1低阻通路流回辅助电源vcc的参考地,光耦u2201的电源输入正引脚则接通第五隔离电源正极drv+vcc。drv_pwm1a和drv_pwm1b分别为第一开关管q101的驱动电路和第四开关管q104的驱动电路输出的驱动信号,幅值分别接近隔离电源drv+vcc_1和drv+vcc 15v的电压。此时,如果第二续流管q106的驱动电路的驱动信号pwm4也为有效电平低电平,那么pmw1所控制的第一开关管q101的驱动电路和第四开关管q104的驱动电路被钳制住,无法输出驱动信号,原理是光电耦合器原边的二极管导通压降为1v左右,而接在限流电路和光电耦合器原边二极管阳极之间的钳位电路二极管d2101、d2201的导通压降为0.3-0.7v左右,辅助电源vcc的电流就不再流经第一开关管q101的驱动电路和第四开关管q104的驱动电路光电耦合器原边的二极管,而是直接流经过钳位电路二极管,通过驱动信号pwm4低阻通路流回辅助电源vcc的参考地,此时第一开关管q101的驱动电路和第四开关管q104的驱动电路的隔离驱动电路的光电耦合器原边的二极管就没有电流经过,光电耦合器输出端无输出,桥臂处于截止状态,使得第一开关管q101和第四开关管q104不会因短路而损坏。第二开关管q102和第三开关管q103的保护原理相同。

41.本发明以上实施例的heric逆变电路简单有效,可应用于heric拓扑及其他开关逻辑互补的功率半导体开关管的驱动,将因干扰或误动作、元器件损坏而造成同时输出有效电平的驱动状态转变成只有一个有效电平的驱动状态,使开关管得到有效保护。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1