一种多路互补输出的驱动电路的制作方法

1.本发明涉及电子电路设计领域,尤其涉及一种多路互补输出的驱动电路。

背景技术:

2.在现代纳米级集成电路技术中,低内部电压被用来进行低功耗数字处理,而外部i/o采用更高的输出电压,以保持与信号标准的兼容性,例如mems、线路驱动器、汽车应用和显示器中可能需要更高的电平,最高可达20v。而高压电路就为功率放大器、线路驱动器等提供了所需的高压驱动能力。高压电路在电源管理中尤为常见,如低压电压调节器、开关转换器或驱动器,其中驱动器是用于电源管理的开关转换器和放大器的基本电路,其供电电压高于标准晶体管的标称电压。

3.早期实现高压驱动器会直接选择高耐压器件以获得更高耐压能力,例如多栅氧化物,但工艺成本昂贵。目前多芯片模块而将大于3.3v的高压开关集成到标准的低压cmos技术中,能实现更低成本和更小面积。在标准的低压技术中,高压设计的目标是找到正确的工作点,使晶体管两端的电压在安全工作区域内,保证可靠工作。

4.在标准cmos技术中,常用的实现高压驱动器的电路拓扑结构是将nmos和pmos晶体管堆叠形成推挽输出级。器件堆叠允许在更多的器件上平均分配高压降,因此比采用单个器件受到压力更小,安全性更高。同时该输出级前还需要一系列缓冲级和处理级的设置。并且为了解决大电流工作状态下瞬态切换时出现的问题,现有技术中构造了两个输入控制信号的死区电路,确保驱动器上下通路不会同时导通,保证了电路的安全和可靠性。但该方法存在很多不足,第一,由于l2h和h2l都是小尺寸晶体管设计,驱动能力严重不足,其和驱动器大晶体管之间需要添加一个反相器级数较多的缓冲器,可能多达五级(包括一级起反相作用),这就意味着大尺寸晶体管的数量增多,而又因为大部分芯片面积被大尺寸晶体管影响,所以导致整体芯片面积增大。第二,由于swp和swn有很明显的先后顺序,即先完整实现vgp1和vgn1的输出,再由它们经过电平位移和反相器才得到vgp2和vgn2,则会导致输出的swp和swn并不是精确的反相关系,存在比较明显的延迟效应。vgp2和vgn2和理想中的波形相比存在一些延时,导致输出swn也存在一些延时,这明显不满足设计和应用需求。若要改善这一现象,需要采用rc延时等延时方法使swp和swn近似反相。需要注意的是,并不能简单地直接对swp进行rc延时,因为rc延时后需要经过缓冲器整流,而我们并不能构造高压下的反相器,所以只能对前一级的vgp1和vgn1分别进行同等的rc延时来达到一样的效果。这样做的结果首先是不能保证两者同时rc延时的精确性和同等性,容易造成很大误差。其次这样做意味着将swp的波形延时,这相当于增加了整个驱动电路的延时。该电路还有最后一个问题,其实现的最终波形swp和swn存在较大的交叠。一般来说,用于控制开关的用途要求输出两路反相的信号尽量不能同时为高电平,从而防止控制的两个开关同时打开,增加系统的稳定性和可靠性。

技术实现要素:

5.技术目的:针对现有技术中的缺陷,本发明公开了一种多路互补输出的驱动电路,在大电流驱动能力要求下,用更小的芯片面积,以及更小的总延时时间输出波形实现两路互补输出、不交叠、高速。

6.技术方案:为实现上述技术目的,本发明提供以下技术方案。

7.一种多路互补输出的驱动电路,包括输入级和输出级,输入级包括输入缓冲器、组合逻辑电路和电平位移电路,输出级包括死区控制电路和高压驱动电路,死区控制电路中还包括电平位移电路;输入信号包括两路gaas开关控制信号即sw1信号和sw2信号、一路电源调制控制信号即rx信号、一路pmos管控制信号即tx信号,输出信号包括sw1p信号、sw1n信号、sw2p信号、sw2n信号、rxp信号、rxn信号、txp信号、txn信号;

8.每一路gaas开关控制信号通过输入级的输入缓冲器、电平位移电路和输出级的死区控制电路、高压驱动电路分别输出两路互补信号,即sw1p信号、sw1n信号和sw2p信号、sw2n信号;rx信号通过输入级的输入缓冲器、组合逻辑电路和输出级的死区控制电路、高压驱动电路分别输出两路互补信号,即rxp信号和rxn信号,tx信号通过输入级的输入缓冲器和输出级的死区控制电路、高压驱动电路分别输出两路互补信号,即txp信号和txn信号;

9.输入信号还包括用于控制rxp信号、rxn信号同相或反向的mode信号,mode信号通过输入缓冲器与组合逻辑电路连接。

10.优选地,所述输入缓冲器用于信号的时序修整和增大信号驱动能力,并将输入的0/1.8v的方波信号转换为0/3.3v的方波信号,输入缓冲器应用在rx信号、tx信号、mode信号、sw1信号和sw2信号的电路上;所述输入缓冲器包括下拉电阻、施密特触发器和缓冲器,输入缓冲器的输入端与下拉电阻的一端连接,下拉电阻的另一端接地,输入缓冲器的输入端与施密特触发器的输入端连接,施密特触发器的输出端与缓冲器的输入端连接,缓冲器的两个输出端v

out

和作为所述输入缓冲器的输出端。

11.优选地,所述组合逻辑电路用于实现mode信号控制rxp和rxn同相和反相的功能,应用在rx信号和mode信号的电路上;组合逻辑电路包括两个传输门和若干反相器;

12.mode信号通过输入缓冲器分别与第一反相器的输入端和第二传输门的输入端连接,第一反相器的输出端与第一传输门的输入端连接,rx信号通过输入缓冲器分别与第二反相器的输入端和第一传输门的输入端连接,第二反相器的输出端与第二反相器的输入端连接,第一传输门的输出端、第二传输门的输出端均与第三反相器的输入端连接,第三反相器的输出端与第四反相器的输入端连接,第三反相器的输出端输出vout_n信号,第四反相器的输出端输出vout_p信号。

13.优选地,所述电平位移电路用于将输入的0/3.3v的方波信号转换为0/-2.5v的方波信号,或将输入的0/-2.5v的方波信号转换为-2.5/-5v的方波信号,应用在sw1信号和sw2信号的电路上,或将输入的0/3.3v的方波信号转换为3.3/5v的方波信号,应用在rx信号、tx信号和mode信号的电路上,其中,将输入的0/-2.5v的方波信号转换为-2.5/-5v的方波信号采用通过电阻分压实现的h2l电平位移电路,将输入的0/3.3v的方波信号转换为3.3/5v的方波信号采用通过电阻分压实现的l2h电平位移电路。

14.优选地,将输入的0/3.3v的方波信号转换为0/-2.5v的方波信号时,电平位移电路通过电阻分压电路实现,分压电阻比例为3:4,使得输入的0/3.3v的方波信号与-5v进行分

压后,经过设计的层层推进的偶数级反相器,最终输出一个满摆幅的、延时较小的0/-2.5v方波信号及其反相的信号。

15.优选地,所述死区控制电路用于将输入的0/3.3v及其反相的方波信号转换为具备一定死区时间的0/3.3v和3.3/5v的方波信号及其反相的方波信号,或将输入的0/-2.5v及其反相的方波信号转换为具备一定死区时间的0/-2.5v和-2.5/-5v的方波信号及其反相的方波信号。

16.优选地,sw路,即sw1信号和sw2信号的电路,其死区控制电路的实现过程为:通过电平位移电路得到前级电平位移后的0/-2.5v的方波信号后,同其再经h2l(高至低电平位移)得到-2.5/-5v的方波信号,0/-2.5v的方波信号和-2.5/-5v的方波信号这两路信号经级联反相器进行层层驱动,得到驱动器的两路控制信号vgp1和vgn1,在vgp1的前级反相器(由mpp11和mnp11组成)中插入一个nmos开关管(mnp12),vgn1的前级反相器(由mpn11和mnn11组成)中插入一个pmos开关管(mpn12),构造两路的反馈控制路径,输出具备一定死区时间的0/-2.5v和-2.5/-5v的方波信号及其反相的方波信号。

17.优选地,所述高压驱动电路采用负电源电压驱动电路,用于将0/3.3v和3.3/5v的方波信号转换为0/5v方波信号,以及将0/-2.5v和-2.5/-5v的方波信号转换为0/-5v方波信号。

18.优选地,所述负电源电压驱动电路采用堆叠晶体管结构,采用0/-5v电源电压,由两个尺寸相同的耐压为2.5v的pmos管控制上通路,两个尺寸相同的耐压为2.5v的nmos管控制下通路。

19.有益效果:本发明在大电流驱动能力要求下,用更小的芯片面积,以及更小的总延时时间输出波形实现两路互补输出、不交叠、高速。

附图说明

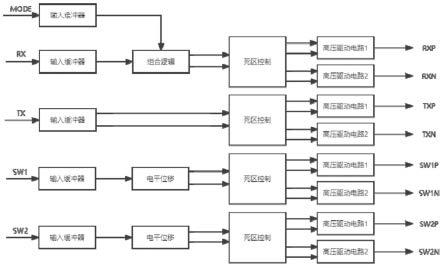

20.图1是本发明的总电路结构框图;

21.图2是本发明中输入缓冲器的结构框图;

22.图3是本发明中输入缓冲器的电路结构示意图;

23.图4是本发明中组合逻辑电路的结构示意图;

24.图5是本发明中电平位移电路的结构示意图;

25.图6是本发明中应用于死区控制电路中的l2h电平位移电路的结构示意图;

26.图7是本发明中应用于死区控制电路中的h2l电平位移电路的结构示意图;

27.图8是本发明中一路sw死区控制电路和负电源电压驱动电路的结构示意图;

28.图9是图8的控制说明图;

29.图10是本发明中正电源电压驱动电路的结构示意图;

30.图11是本发明中未进行互补输出设计的输出级电路结构示意图;

31.图12是互补输出不交叠的波形示意图;

32.图13是本发明中互补输出的波形示意图;

33.图14是本发明中进行互补输出设计的输出级电路结构示意图;

34.图15是本发明互补输出逻辑验证仿真中rxp和rxn波形示意图;

35.图16是本发明互补输出逻辑验证仿真中txp和txn波形示意图;

36.图17是本发明互补输出逻辑验证仿真中swp和swn波形示意图。

具体实施方式

37.为了进一步的说明本发明公开的技术方案,下面结合说明书附图和实施例作详细的阐述。本领域的技术人员应得知,在不违背本发明精神前提下所做出的优选和改进均落入本发明的保护范围,对于本领域的惯用技术在本具体实施例中不做详细记载和说明。

38.如附图1所示,一种多路互补输出的驱动电路,包括输入级和输出级,输入级包括输入缓冲器、组合逻辑电路和电平位移电路,输出级包括死区控制电路和高压驱动电路,死区控制电路中还包括电平位移电路;输入信号包括两路gaas开关控制信号即sw1信号和sw2信号、一路电源调制控制信号即rx信号、一路pmos管控制信号即tx信号,输出信号包括sw1p信号、sw1n信号、sw2p信号、sw2n信号、rxp信号、rxn信号、txp信号、txn信号;sw1信号、sw2信号、rx信号、tx信号均为cmos信号;

39.每一路gaas开关控制信号通过输入级的输入缓冲器、电平位移电路和输出级的死区控制电路、高压驱动电路分别输出两路互补信号,即sw1p信号、sw1n信号和sw2p信号、sw2n信号;rx信号通过输入级的输入缓冲器、组合逻辑电路和输出级的死区控制电路、高压驱动电路分别输出两路互补信号,即rxp信号和rxn信号,tx信号通过输入级的输入缓冲器和输出级的死区控制电路、高压驱动电路分别输出两路互补信号,即txp信号和txn信号;

40.此外,输入信号还包括用于控制rxp信号、rxn信号同相或反向的mode信号,mode信号通过输入缓冲器与组合逻辑电路连接。

41.输入缓冲器用于将输入的0/1.8v的方波信号转换为0/3.3v的方波信号,其中,sw1信号、sw2信号、rx信号、tx信号和mode信号均为0/1.8v的方波信号;组合逻辑电路用于通过mode信号控制rxp和rxn的同相和反相,电平位移电路用于将输入的0/3.3v的方波信号转换为0/-2.5v的方波信号,用于满足后续对于负高压驱动电路的需求;死区控制电路用于将输入的0/3.3v的方波信号转换为3.3/5v的方波信号,将输入的0/-2.5v的方波信号转换为-2.5/-5v的方波信号,高压驱动电路用于将3.3/5v的方波信号转换为0/5v方波信号,将-2.5/-5v的方波信号转换为0/-5v方波信号,具体的rxp信号、rxn信号、txp信号、txn信号均为高压0/5v方波信号,sw1p信号、sw1n信号、sw2p信号、sw2n信号均为高压0/-5v方波信号。

42.本方案实现将2路0/1.8v的cmos信号转换为两路0/-5v的具有1ma电流驱动能力的互补输出sw1p、sw1n和sw2p、sw2n用于控制gaas开关;将1路0/1.8v的cmos信号转换为0/+5v的具有100ma电流驱动能力的互补输出rxp和rxn用于接收低噪放电源调制以及将1路0/1.8v的cmos信号转换为0/+5v的具有1ma电流驱动能力的互补输出txp和用于控制发射调制pmos管。首先,输入缓冲器将输入的0/1.8v的方波信号转换为0/3.3v的方波信号。mode信号用于控制rxp和rxn的同相和反相。其次,两路sw需要经过一级电平位移将0/3.3v的方波信号转换为0/-2.5v的方波信号用于满足后续对于负高压驱动电路的需求。然后,经过设计的死区控制电路,输出能够驱动高压驱动电路的0/3.3v和3.3/5v方波信号及0/-2.5v和-2.5/-5v方波信号,还有各自对应的反相信号。最后,每一路经过高压驱动电路,输出各自对应的互补高压信号0/5v方波信号(rxp/rxn/txp/txn)和0/-5v方波信号(sw1p/sw1n/sw2p/sw2n)。

43.输入级和输出级各电路结构具体包括:

1.25v,然后经过设计的层层推进的偶数级反相器,最终输出一个满摆幅的,延时较小的0/-2.5v方波信号以及其反相的信号。同理,将输入的0/3.3v的方波信号转换为0/-2.5v的方波信号的电平位移电路中,先经过电阻分压,按附图5中得到-0.26/-2.14v的方波,再反相器输出得到0/-2.5v的方波信号;本发明中附图5所示的电平位移电路应用于附图1中所下方的两个电平位移处,附图6和附图7所示的l2h/h2l电平位移电路用于死区控制模块中的电平位移(l2h、h2l)。

55.通过电阻分压实现的l2h/h2l电平位移电路,本发明在输出级中的死区控制电路中进行设计,并且全都是在各自正电压电源5v或负电压电源-5v下实现的,即0/3.3v和3.3/5v之间的电平位移及0/-2.5v和-2.5/-5v之间的电平位移。这种情况下的电平位移电路分为l2h(低到高电平位移电路)和h2l(高到低电平位移电路)两种,其中l2h电路结构如附图6所示,h2l电路结构如附图7所示。

56.4、死区控制电路;

57.所述死区控制电路用于将输入的0/3.3v及其反相的方波信号转换为具备一定死区时间的0/3.3v和3.3/5v的方波信号及其反相的方波信号,或将输入的0/-2.5v及其反相的方波信号转换为具备一定死区时间的0/-2.5v和-2.5/-5v的方波信号及其反相的方波信号。

58.如附图8所示,附图8给出了本发明中sw一路信号的死区控制电路和负电源电压驱动电路,sw路(sw1或sw2)的电源电压为-5v,所以在通过电平位移电路得到前级电平位移后的0/-2.5v的方波信号vin后,vin的另一路相同的输入信号再经h2l(高至低电平位移)得到-2.5/-5v的方波信号一起应用到sw死区控制电路中。

59.死区控制电路中,该两路信号经三级的级联反相器进行层层驱动,得到驱动器的两路控制信号vgp1和vgn1,vgp1和vgn1虽具备驱动能力,但还未进行死区控制。于是选择在vgp1的前级反相器(由mpp11和mnp11组成)中插入一个nmos开关管(mnp12),vgn1的前级反相器(由mpn11和mnn11组成)中插入一个pmos开关管(mpn12),并构造两路的反馈控制路径,输出具备一定死区时间的0/-2.5v和-2.5/-5v的方波信号及其反相的方波信号。死区控制电路的输出就是经过反馈的vgp1和vgn1。附图8最右边框起来的是附图1中的高压驱动电路模块,out信号输出作为高压驱动电路的输入。附图8介绍的只是一路sw路,所以是一路输入两路输出,加上swp路后就变成两路输入四路输出,即附图14的电路。

60.sw路死区控制说明图如附图9所示,附图9的vin对应附图5的vn输出;对于vgp1而言,若前级输入为-2.5v,则mpp11导通,vgp1直接输出为0v。若前级输入为0v,mpp11关断,mnp11导通,此时输出vgp1的电位取决于开关管mnp12是否导通。而mnp12的通断由vgn1控制,只有当vgn1为-5v时,经过l2h(低至高电平位移)电平位移到-2.5v,经过奇数级的反相器得到电位为0v,此时mnp12才能导通,使得vgp1输出为-2.5v。同理,当vgp1为0v时,经另一条反馈回路使电平位移至-5v,从而使得开关管mpn12导通,vgn1电位输出才能为-2.5v。总而言之,对于这种基本同相输入的两个不同电平的方波信号,vgp1先为高电平(0),vgn1才能随之为高电平(-2.5v);vgn1先为低电平(-5v),vgp1才能随之为低电平(-2.5v)。于是最终得到的驱动器的两路控制信号vgp1和vgn1如附图9中所示,具备比较可靠且可控的左右死区时间。

61.另外,较为精确的死区时间能通过该电路结构进行大致的估计和计算。从vgp1为

高电平到vgn1为高电平之间经历的时间t

dl

为:

62.t

dl

=t

h2l

+tinverters1+ton1ꢀꢀꢀ

(4.1)

63.其中,t

h2l

是h2l电平位移的时延,tinverters1是低电平反馈路径上奇数级反相器的时延,低电平反馈路径指的是附图9中的vgp1反馈经过h2l、三级反相器以及带开关管mpn12的反相器控制vgn1,ton1是vgn1前级带开关管的反相器导通时延。同理也可得另外半边的死区时间t

dr

为:

64.t

dr

=t

l2h

+tinverters2+ton2ꢀꢀꢀ

(4.2)

65.其中,t

l2h

是l2h电平位移的时延,tinverters2是高电平反馈路径上奇数级反相器的时延,高电平反馈路径指的是附图9中的vgn1反馈经过l2h、三级反相器以及带开关管mnp12的反相器后控制vgp1,ton2是vgp1前级带开关管的反相器导通时延。

66.其实更精确的死区时间应该为晶体管mp1关断到晶体管mn1开启之间的时间,即vgp1上升至0-|vthp1|时到vgn1上升至-5v+vthn1之间所经历的时间。但由于上升/下降沿时间和死区时间相比较小,所以在设计死区电路时可以采取前者对死区时间进行较为大致的估计和计算。

67.需要注意的是,数字电路中边沿过陡导致的电源波动问题在电路尺寸较大,负载要求过高时也显现出来,所以在死区控制电路最后级的尺寸选择时需要综合考虑电源波动问题和驱动不足所带来的延时问题,折中进行尺寸的优化。本发明中公开的死区控制电路在大尺寸、大电流下完成。本发明指标要求大电流,所以体现在需要大尺寸的晶体管以及电路及版图设计的安全稳定性(例如电源波动问题和版图走线宽度问题)。rxp是100ma,rxn是5ma驱动能力。本发明中提到的大电流指的就是rxp路。

68.5、高压驱动电路(driver);

69.在标准cmos技术下设计高压驱动电路,最重要的是找到正确的工作点,确保各个晶体管工作在限制电压下,从而保证电路的安全可靠性。

70.高压驱动电路采用负电源电压驱动电路,用于将0/3.3v和3.3/5v的方波信号转换为0/5v方波信号,以及将0/-2.5v和-2.5/-5v的方波信号转换为0/-5v方波信号。

71.本实施例中采用负电源电压驱动电路,如附图10所示,采用了堆叠晶体管结构,由两个尺寸相同((w/l)

p1

=(w/l)

p2

)的耐压为2.5v的pmos管控制上通路,两个尺寸相同((w/l)

n1

=(w/l)

n2

)的耐压为2.5v的nmos管控制下通路,同时应避免同时导通。实际上,为了确保安全性,晶体管可以采用更高的3.3v耐压管,来确保各种情况下晶体管任意两端之间的压降不超过耐压条件。并且之所以pmos(nmos)管的尺寸相同,是因为尽可能使导通时两管分到的压降相同,从而使5v平均分到两个管子,确保其满足安全性条件。

72.同时需要注意的是,m

p2

和m

n2

的body端需要接至各自的源极,而不是接至电源或地。这是由于在上通路导通时,out端电压为5v,此时若m

n2

的body端接至地,则会导致m

n2

存在两端之间的压降为5v,大大超过了耐压条件,使晶体管最终会被击穿破坏。反之下通路导通同理。所以,在设计堆叠晶体管式驱动电路时,要严格控制各端点之间的电压,尽可能地使其都在安全电压范围之内。

73.另外需要注意的是,由于没有-2.5v电源,所以m

p2

和m

n2

的栅极电压需要由一个-2.5v电源产生电路来提供。-2.5v电源产生电路直接采用两个电阻对地和-5v电源进行分压产生-2.5v电源,同时并联两个去耦电容,减小耦合到电源端的噪声,提供较为稳定的电源。

同时,电阻值的大小需要折中考虑,过大的电阻值会导致-2.5v电源有更大的电压波动,而过小的电阻值会使得该电路产生了较大的静态功耗。

74.以sw路为例将上一小节的死区控制电路与高压驱动电路相连接,便得到最终的输出级电路,如图11所示。

75.6、互补输出设计;

76.为实现附图12要求的输出波形,首先,不交叠的输出需要减小swp或swn的占空比,而从减小占空比后的方波可以再倒推回vgp和vgn的波形,大致如附图13所示。在观察图中的vgp和vgn的波形及结合驱动器的原理分析后可以发现,vgp2的下降沿应尽量延后于vgn1的上升沿,以及vgp1的下降沿尽量延后于vgn2的上升沿,而延后的具体的时间应结合swp和swn的上升下降沿统筹考虑。与此同时又要保证各自两路vgp和vgn信号的左右死区控制时间,所以结合上述几点要求,得到只要vgp1“涵盖”vgn2的反相信号,vgn1“涵盖”vgp2的反相信号,各自两路vgp“涵盖”vgn即可。以及出于复杂度考虑,vgn1和vgn2的关系可以直接令它们为反相关系,之后将会说明这样做的好处。综上所述,我们根据各信号之间已确定的时序逻辑关系,便能进一步得到该互补输出设计方案的雏形。且在考虑电路结构时要注意不能再像前文提到的基本方法一样只倒退一级在驱动器前思考结构变化,而是要再倒退一级,在死区控制模块就需要寻求电路结构的变化。

77.首先,先保证sw路的左右死区控制时间,即将sw路按负电源电压驱动方式实现输出级电路,其中注意死区控制电路的输入vin也需要反相再作为输入。这样,vgp2和vgn2的波形已大致按附图13中实现。其次,由于vgn1和vgn2的时序逻辑关系为反相,所以可以直接将已实现的vgn2经过一级尺寸较大的反相器inverterd后作为vgn1。最后,我们还需要考虑vgp1波形的实现,其具体要求是vgp1的下降沿尽量延后于vgn2的上升沿,同时又要保证vgp1和vgn1之间有一定的左右死区时间。这里就体现出vgn1作为vgn2的反相波形的好处,不仅使电路复杂度降低,而且将vgp1的下降沿尽量延后于vgn2的上升沿这一要求近似等同于vgp1和vgn1之间有一定的下降沿死区时间。所以综上所述,最后我们只需要考虑如何在确定vgn1波形之后实现带有左右死区时间的如附图13所示的vgp1波形。

78.在第4点中已经介绍过,死区控制电路的本质在波形图上可以理解为vgp的上升沿控制vgn的上升沿,即当vgp上升沿快结束时vgn才能开启上升沿。同理vgn的下降沿控制vgp的下降沿。而目前是vgn1已经确定上升沿和下降沿,所以我们首先可以通过vgn1的下降沿来控制vgp1的下降沿,即采用半边死区控制电路,从而率先保证满足了右死区时间功能。最后,便只剩下如何实现控制vgp1的上升沿领先于vgn1的上升沿这一问题。

79.按以上思路设计出对应的电路原理图,如附图14所示,即为本发明一个实施例中整个sw路(sw1和sw2)的输出级电路结构示意图包括死区控制及高压驱动,其中driver1和driver2对应的是附图1中的高压驱动电路1和高压驱动电路2,driver1和driver2均采用负电源电压驱动电路。观察图中各节点时序逻辑后发现,电路已实现了vgp1上升沿领先于vgn1上升沿。这是由于vgp1前一级栅极的电位只要为-2.5v时,mpp11即刻导通,vgp1直接输出上升沿而不受控制管mnp12影响。所以vgp1的上升沿同输入vin相比的延时t1仅等于vin经过的几级反相器的延时tinverters1与vgn1前级带开关管的反相器导通时延ton1之和。反观vgn1的上升沿,由于其是由vgn2反相而来,所以可以关注vgn2的下降沿并加上tinverterd即可。同样由于vgn2的前一级栅极的电位为-2.5v时,mnn21即刻导通,vgn2直接

输出下降沿而不受控制管mpn22影响。所以vgn2的下降沿同输入vin相比的延时t2为:

80.t2=tinverter

+

t

h2l

+tinverters2+ton2

ꢀꢀꢀ

(4.3)

81.其中,tinverter是vin至所经过的一级反相器延时,t

h2l

是h2l电平位移延时。通过分析发现,借助于中间量vin,可以得到vgp1的上升沿是领先于vgn1的上升沿,领先时间td为:

82.td=t

2-t1+tinverterd=tinverter+t

h2l

+tinverters2+t

on2-tinverters

1-t

onl

+tinverterd

ꢀꢀꢀ

(4.4)

83.至此,我们实现了如附图13的所有波形。对比互补输出本方案和基本方法,可以发现本方案成功解决了现有技术中存在的几个问题。第一,本发明电路少使用一个h2l电平位移电路而且由于构建的新反馈路径控制的为开关管,所以反相器的尺寸并不用很大,整体而言所芯片所占面积也会更小。第二,本发明利用电路拓扑结构便能成功实现死区控制和输出互补波形,不需要额外的rc延时等操作来调整波形时序逻辑,从而使得总延时也更短。第三,本发明实现了尽量不交叠的两路互补输出信号,这对于开关应用等场景是非常重要的一个需求。第四,本发明实现了延时和上升下降沿小,并实现了高速的开关应用。

84.本发明公开了一种多路互补输出的驱动电路,采用标准低压管(标准cmos技术)实现高压的驱动电路,将2路0/1.8v的cmos信号(sw1和sw2)转换为两路0/-5v的具有1ma电流驱动能力的互补输出sw1p、sw1n和sw2p、sw2n用于控制gaas开关;将1路0/1.8v的cmos信号转换为0/+5v的具有100ma电流驱动能力的互补输出rxp和rxn用于接收低噪放电源调制以及将1路0/1.8v的cmos信号转换为0/+5v的具有1ma电流驱动能力的互补输出txp和用于控制发射调制pmos管,在大电流驱动能力要求下,即得到互补输出具有100ma电流驱动能力的rxp和具有5ma电流驱动能力的rxn用于接收低噪放电源调制,用更小的芯片面积,以及更小的总延时时间输出波形实现两路互补输出、不交叠、高速。

85.仿真证明:

86.如附图15-附图17所示,为本发明利用cadence软件进行仿真的结果,附图15中,在输入0/1.8v的rx信号时,输出0/+5v的两路互补的rxp信号和rxn信号;附图16中,在输入0/1.8v的tx信号时,输出0/+5v的两路互补的txp信号和txn信号;附图17中,在输入0/1.8v的sw信号时,输出0/-5v的两路互补的swp和swn信号;从附图15-附图17中可以看出不仅本发明成功实现了互补输出,且二者之间几乎不存在交叠,为实际用途的安全性和稳定性提供了保障,也就是说本发明公开的一种多路互补输出的驱动电路,能够在互补输出的同时保证死区控制,以及用作开关时两输出交叠极小。

87.以上所述仅是本发明的优选实施方式,应当指出:对于本技术领域的普通技术人员来说,在不脱离本发明原理的前提下,还可以做出若干改进和润饰,这些改进和润饰也应视为本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1