三单元H桥级联逆变器多电平调制方法

三单元h桥级联逆变器多电平调制方法

技术领域

1.本发明涉及高压大功率调速技术领域,尤其涉及一种三单元h桥级联逆变器多电平调制方法。

背景技术:

2.高压交流电机需由大功率dc/ac逆变器驱动,在高交流电压输出而功率器件耐压能力有限的情况下,可采用功率器件串联或是功率单元串联的方法来解决。功率器件在串联使用时,由于各器件的动态电阻和极间电容不同,而存在静态均压和动态均压问题。如果采用与器件并联r和rc的均压措施,会使电路复杂,损耗增加;同时,器件的串联对驱动电路的要求也大大提高,要尽量做到串联器件同时导通和关断,否则由于各器件开断时间不一致,承受电压不均,会导致器件损坏甚至整个装置崩溃。而h桥级联型逆变器可产生多电平pwm电压,并且不存在复杂的电压均衡问题;同时,每个h桥功率单元可独立控制,在输出电平数相同的情况下,h桥级联型多电平逆变器所需功率器件少,易于实现模块化,便于拓展。

3.h桥级联型多电平逆变器采用传统三角载波移相控制时,由于各单元功率开关管都处于高频工作状态,开关损耗在总体损耗中占据主导。并且各单元中每个桥臂上下开关管互补导通,为防止输入侧直流母线发生直通现象需在桥臂上下开关管驱动信号中添加死区时间,死区时间的加入必定会引起输出交流电压波形畸变。

技术实现要素:

4.本发明要解决的技术问题是,克服三单元h桥级联型多电平逆变器严重的开关损耗以及死区效应引起输出电压波形畸变。

5.为解决技术问题,本发明的解决方案是:提供一种能够减少高频工作开关管并能避免各桥臂上下开关管互补导通的三单元h桥级联逆变器多电平调制方法,主电路由三个功率单元级联而成,每个功率单元中电压值为e的直流电源两端跨接一个由两个半桥组成的h桥,各半桥由两个带反并联二极管的全控开关管串联而成。将三个功率单元分为一个高频工作单元与两个低频工作单元。当调制波vm>2e时,低频工作功率单元1输出电平+e,低频工作功率单元2输出电平+e;e<调制波vm≤2e时,低频工作功率单元1输出零电平,低频工作功率单元2输出电平+e;-e≤调制波vm≤e时,低频工作功率单元1输出零电平,低频工作功率单元2输出零电平;-2e≤调制波vm<-e时,低频工作功率单元1输出零电平,低频工作功率单元2输出电平-e;当调制波vm<-2e时,低频工作功率单元1输出电平-e,低频工作功率单元2输出电平-e。

6.当调制波vm>2e时,(v

m-2e)*0.5与载波比较后获得逻辑信号p1,(v

m-2e)*(-0.5)与载波比较后获得逻辑信号p2,逻辑信号p1与逻辑信号p2两者做异或操作后获得信号p,高频工作功率单元3输出电平p*e;e<调制波vm≤2e时,(v

m-e)*0.5与载波比较后获得逻辑信号p1,(v

m-e)*(-0.5)与载波比较后获得逻辑信号p2,逻辑信号p1与逻辑信号p2两者做异或操作后获得信号p,高频工作功率单元3输出电平p*e;-e≤调制波vm≤e时,vm*0.5与载波比

较后获得逻辑信号p1,vm*(-0.5)与载波比较后获得逻辑信号p2,逻辑信号p1与逻辑信号p2两者做异或操作后获得信号p,高频工作功率单元3输出电平p*e;-2e≤调制波vm<-e时,(vm+e)*0.5与载波比较后获得逻辑信号p1,(vm+e)*(-0.5)与载波比较后获得逻辑信号p2,逻辑信号p1与逻辑信号p2两者做异或操作后获得信号p,高频工作功率单元3输出电平p*e;当调制波vm<-2e时,(vm+2e)*0.5与载波比较后获得逻辑信号p1,(vm+2e)*(-0.5)与载波比较后获得逻辑信号p2,逻辑信号p1与逻辑信号p2两者做异或操作后获得信号p,高频工作功率单元3输出电平p*e。每个载波周期内各桥臂在保证其中一个开关管驱动信号为低电平的前提下根据所需输出电平、调制电压、直流母线电压以及输出电流确定各功率开关管的驱动信号。

7.相邻两个调制波周期中,对于高频工作功率单元中各桥臂高频工作状态与低频工作状态替换一次;对于低频工作功率单元,一个调制波周期内输出零电平由两桥臂的上管动作产生,另一个调制波周期内输出零电平由两桥臂的下管动作产生。

8.本发明的有益效果是:避免三个功率单元都处于高频工作状态,减少了开关损耗,并且在整个运行期间保证各功率单元中四个全控开关管开关次数均衡;同时克服了死区效应引起的输出电压波形畸变。

附图说明:

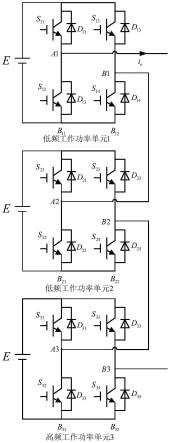

9.图1三单元h桥级联逆变器主电路。

具体实施方式

10.本发明的实现基础是,基于三单元级联逆变器,低频工作功率单元1直流母线两端跨接电压值为e的直流电源、半桥b

11

与半桥b

12

,低频工作功率单元2直流母线两端跨接电压值为e的直流电源、半桥b

21

与半桥b

22

,高频工作功率单元3直流母线两端跨接电压值为e的直流电源、半桥b

31

与半桥b

32

。带反并联二极管d

11

的全控开关管s

11

与带反并联二极管d

12

的全控开关管s

12

串联构成半桥b

11

,带反并联二极管d

13

的全控开关管s

13

与带反并联二极管d

14

的全控开关管s

14

串联构成半桥b

12

。带反并联二极管d

21

的全控开关管s

21

与带反并联二极管d

22

的全控开关管s

22

串联构成半桥b

21

,带反并联二极管d

23

的全控开关管s

23

与带反并联二极管d

24

的全控开关管s

24

串联构成半桥b

22

。带反并联二极管d

31

的全控开关管s

31

与带反并联二极管d

32

的全控开关管s

32

串联构成半桥b

31

,带反并联二极管d

33

的全控开关管s

33

与带反并联二极管d

34

的全控开关管s

34

串联构成半桥b

32

。半桥b

12

中点b1与半桥b

21

中点a2相连,半桥b

22

中点b2与半桥b

31

中点a3相连,半桥b

11

中点a1与半桥b

32

中点b3两端电压作为逆变器输出电压。载波周期起始时刻抓取调制电压vm,输出电流io。计数值num起始值为0,当前载波周期调制电压vm极性从负变为正则计数值num增1,若num=2则num=0。低频工作单元状态变量s_low的确定规则为,若num=0且io<0且调制波vm<-2e时s_low=1,若num=0且io<0且-2e≤调制波vm<-e时s_low=2,若num=0且io<0且-e≤调制波vm≤e时s_low=3,若num=0且io<0且e<调制波vm≤2e时s_low=4,若num=0且io<0且调制波vm>2e时s_low=5,若num=0且io≥0且调制波vm<-2e时s_low=6,若num=0且io≥0且-2e≤调制波vm<-e时s_low=7,若num=0且io≥0且-e≤调制波vm≤e时s_low=8,若num=0且io≥0且e<调制波vm≤2e时s_low=9,若num=0且io≥0且调制波vm>2e时s_low=10,若num=i且io<0且调制波

vm<-2e时s_low=11,若num=1且io<0且-2e≤调制波vm<-e时s_low=12,若num=1且io<0且-e≤调制波vm≤e时s_low=13,若num=1且io<0且e<调制波vm≤2e时s_low=14,若num=1且io<0且调制波vm>2e时s_low=15,若num=1且io≥0且调制波vm<-2e时s_low=16,若num=1且io≥0且-2e≤调制波vm<-e时s_low=17,若num=1且io≥0且-e≤调制波vm≤e时s_low=18,若num=1且io≥0且e<调制波vm≤2e时s_low=19,若num=1且io≥0且调制波vm>2e时s_low=20。高频工作单元状态变量s_high的确定规则为,若num=0且io≥0且调制波vm≥0时s_high=4,若num=0且io<0且调制波vm≥0时s_high=3,若num=0且io≥0且调制波vm<0时s_high=2,若num=0且io<0且调制波vm<0时s_high=1,若num=1且io≥0且调制波vm≥0时s_high=14,若num=1且io<0且调制波vm≥0时s_high=13,若num=1且io≥0且调制波vm<0时s_high=12,若num=1且io<0且调制波vm<0时s_high=11。表征高频工作功率单元在载波周期内输出平均电压的逻辑信号p产生原则为,若调制波vm>2e时则(v

m-2e)*0.5与载波比较后获得逻辑信号p1且(v

m-2e)*(-0.5)与载波比较后获得逻辑信号p2,若e<调制波vm≤2e时则(v

m-e)*0.5与载波比较后获得逻辑信号p1且(v

m-e)*(-0.5)与载波比较后获得逻辑信号p2,若-e≤调制波vm≤e时则vm*0.5与载波比较后获得逻辑信号p1且vm*(-0.5)与载波比较后获得逻辑信号p2,若-2e≤调制波vm<-e时则(vm+e)*0.5与载波比较后获得逻辑信号p1且(vm+e)*(-0.5)与载波比较后获得逻辑信号p2,若调制波vm<-2e时则(vm+2e)*0.5与载波比较后获得逻辑信号p1且(vm+2e)*(-0.5)与载波比较后获得逻辑信号p2,逻辑信号p1与逻辑信号p2两者做异或操作后获得信号p。低频工作功率单元根据状态变量的值按规则产生各开关管驱动信号,高频工作功率单元根据状态变量及逻辑信号p按规则产生各开关管驱动信号。

11.对于低频工作功率单元1,若s_low=1则s

11

与s

14

驱动信号为低电平且s

12

与s

13

驱动信号为高电平,若s_low=11则s

11

与s

14

驱动信号为低电平且s

12

与s

13

驱动信号为高电平,若s_low=2则s

11

、s

12

与s

14

驱动信号为低电平且s

13

驱动信号为高电平,若s_low=12则s

11

、s

13

与s

14

驱动信号为低电平且s

12

驱动信号为高电平,若s_low=3则s

11

、s

12

与s

14

驱动信号为低电平且s

13

驱动信号为高电平,若s_low=13则s

11

、s

13

与s

14

驱动信号为低电平且s

12

驱动信号为高电平,若s_low=4则s

11

、s

12

、s

13

与s

14

驱动信号为低电平,若s_low=14则s

11

、s

12

、s

13

与s

14

驱动信号为低电平,若s_low=5则s

11

、s

12

、s

13

与s

14

驱动信号为低电平,若s_low=15则s

11

、s

12

、s

13

与s

14

驱动信号为低电平,若s_low=6则s

11

、s

12

、s

13

与s

14

驱动信号为低电平,若s_low=16则s

11

、s

12

、s

13

与s

14

驱动信号为低电平,若s_low=7则s

11

、s

12

、s

13

与s

14

驱动信号为低电平,若s_low=17则s

11

、s

12

、s

13

与s

14

驱动信号为低电平,若s_low=8则s

12

、s

13

与s

14

驱动信号为低电平且s

11

驱动信号为高电平,若s_low=18则s

11

、s

12

与s

13

驱动信号为低电平且s

14

驱动信号为高电平,若s_low=9则s

12

、s

13

与s

14

驱动信号为低电平且s

11

驱动信号为高电平,若s_low=19则s

11

、s

12

与s

13

驱动信号为低电平且s

14

驱动信号为高电平,若s_low=10则s

11

与s

14

驱动信号为高电平且s

12

与s

13

驱动信号为低电平,若s_low=20则s

11

与s

14

驱动信号为高电平且s

12

与s

13

驱动信号为低电平。

12.对于低频工作功率单元2,若s_low=1则s

21

与s

24

驱动信号为低电平且s

22

与s

23

驱动信号为高电平,若s_low=11则s

21

与s

24

驱动信号为低电平且s

22

与s

23

驱动信号为高电平,若s_low=2则s

21

与s

24

驱动信号为低电平且s

22

与s

23

驱动信号为高电平,若s_low=12则s

21

与s

24

驱动信号为低电平且s

22

与s

23

驱动信号为高电平,若s_low=3则s

21

、s

22

与s

24

驱动信号为

低电平且s

23

驱动信号为高电平,若s_low=13则s

21

、s

23

与s

24

驱动信号为低电平且s

22

驱动信号为高电平,若s_low=4则s

21

、s

22

、s

23

与s

24

驱动信号为低电平,若s_low=14则s

21

、s

22

、s

23

与s

24

驱动信号为低电平,若s_low=5则s

21

、s

22

、s

23

与s

24

驱动信号为低电平,若s_low=15则s

21

、s

22

、s

23

与s

24

驱动信号为低电平,若s_low=6则s

21

、s

22

、s

23

与s

24

驱动信号为低电平,若s_low=16则s

21

、s

22

、s

23

与s

24

驱动信号为低电平,若s_low=7则s

21

、s

22

、s

23

与s

24

驱动信号为低电平,若s_low=17则s

21

、s

22

、s

23

与s

24

驱动信号为低电平,若s_low=8则s

22

、s

23

与s

24

驱动信号为低电平且s

21

驱动信号为高电平,若s_low=18则s

21

、s

22

与s

23

驱动信号为低电平且s

24

驱动信号为高电平,若s_low=9则s

21

与s

24

驱动信号为高电平且s

22

与s

23

驱动信号为低电平,若s_low=19则s

21

与s

24

驱动信号为高电平且s

22

与s

23

驱动信号为低电平,若s_low=10则s

21

与s

24

驱动信号为高电平且s

22

与s

23

驱动信号为低电平,若s_low=20则s

21

与s

24

驱动信号为高电平且s

22

与s

13

驱动信号为低电平。

13.对于高频工作功率单元3,若s_high=4则s

31

驱动信号为信号p且s

34

驱动信号为高电平且s

32

与s

33

驱动信号为低电平,若s_high=14则s

34

驱动信号为信号p且s

31

驱动信号为高电平且s

32

与s

33

驱动信号为低电平,若s_high=3则s

31

、s

33

与s

34

驱动信号为低电平且s

32

驱动信号为信号p的取反信号,若s_high=13则s

31

、s

32

与s

34

驱动信号为低电平且s

33

驱动信号为信号p的取反信号,若s_high=2则s

32

、s

33

与s

34

驱动信号为低电平且s

31

驱动信号为信号p的取反信号,若s_high=12则s

31

、s

32

与s

33

驱动信号为低电平且s

34

驱动信号为信号p的取反信号,若s_high=1则s

32

驱动信号为信号p且s

33

驱动信号为高电平且s

31

与s

34

驱动信号为低电平,若s_high=11则s

33

驱动信号为信号p且s

32

驱动信号为高电平且s

31

与s

34

驱动信号为低电平。

14.下面结合附图进一步说明本发明。

15.图1所示为三单元h桥级联逆变器主电路结构图,由低频工作功率单元1、低频工作功率单元2与高频工作功率单元3级联构成。低频工作功率单元1直流母线两端跨接电压值为e的直流电源、半桥b

11

与半桥b

12

,低频工作功率单元2直流母线两端跨接电压值为e的直流电源、半桥b

21

与半桥b

22

,高频工作功率单元3直流母线两端跨接电压值为e的直流电源、半桥b

31

与半桥b

32

。带反并联二极管d

11

的全控开关管s

11

与带反并联二极管d

12

的全控开关管s

12

串联构成半桥b

11

,带反并联二极管d

13

的全控开关管s

13

与带反并联二极管d

14

的全控开关管s

14

串联构成半桥b

12

。带反并联二极管d

21

的全控开关管s

21

与带反并联二极管d

22

的全控开关管s

22

串联构成半桥b

21

,带反并联二极管d

23

的全控开关管s

23

与带反并联二极管d

24

的全控开关管s

24

串联构成半桥b

22

。带反并联二极管d

31

的全控开关管s

31

与带反并联二极管d

32

的全控开关管s

32

串联构成半桥b

31

,带反并联二极管d

33

的全控开关管s

33

与带反并联二极管d

34

的全控开关管s

34

串联构成半桥b

32

。半桥b

12

中点b1与半桥b

21

中点a2相连,半桥b

22

中点b2与半桥b

31

中点a3相连,半桥b

11

中点a1与半桥b

32

中点b3两端电压作为逆变器输出电压。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1